| |

MG Expedition ликбез ... MG Expedition ликбез ... |

|

|

|

|

Ответов

(2145 - 2159)

|

|

Jan 13 2013, 13:48 Jan 13 2013, 13:48

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Помогите пожалуйста понять, как решить следующие 2 проблемы: 1) при трассировке дифпары (стек задан) в CES имеется предупреждение о значительном расхождениее величины актуапльного волнового сопротивления от заданного. Исходя из вида трассы, не удается понять причину вывода таких значений- см. скриншот. 2)Никак не могу разобраться с teardrops - при куче перебранных комбинаций чисел, возникает одна и та же ошибка: Error: Secondary distance must be less than Preferred distance. Please reenter it. Error: The T-Junction and Neckdown ratios must be > 0.0 and <= 10.0. Please reenter уже просто тупо перебираю числа- а ничего не меняется  см скриншот

Эскизы прикрепленных изображений

|

|

|

|

|

|

|

|

Jan 14 2013, 08:47 Jan 14 2013, 08:47

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(SM @ Jan 13 2013, 11:57)  Подскажите пожалуйста, есть ли в Exp средство для оценки индуктивности сегмента дорожки? (оценить индуктивность низкоомного медного резистора, разведенного различными "змейками") Есть же спец. средство генерации\оптимизации встроенных пассивных компонентов - Setup>Embeded>Planer(Optimiser). Попробуйте ввести ( Setup>Materia/Process_Editor) в качестве нового материала параметры металла данного слоя и посмотрите разные результаты в планировщике\оптимизаторе. Цитата(EvilWrecker @ Jan 13 2013, 17:48)  Помогите пожалуйста понять, как решить следующие 2 проблемы: 1) при трассировке дифпары (стек задан) в CES имеется предупреждение о значительном расхождениее величины актуапльного волнового сопротивления от заданного. Исходя из вида трассы, не удается понять причину вывода таких значений- см. скриншот. 2)Никак не могу разобраться с teardrops - при куче перебранных комбинаций чисел, возникает одна и та же ошибка: Error: Secondary distance must be less than Preferred distance. Please reenter it. Error: The T-Junction and Neckdown ratios must be > 0.0 and <= 10.0. Please reenter уже просто тупо перебираю числа- а ничего не меняется  см скриншот 1. Она же показывает минимальное и максимальное значение - соотвественно в местах подключения к КП у вас такой большой имепеданс и получается. 2. Давайте тестовый проект. Т.к. у меня с вашими значениями не ругается.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

Jan 16 2013, 10:34 Jan 16 2013, 10:34

|

Участник

Группа: Участник

Сообщений: 32

Регистрация: 15-06-09

Пользователь №: 50 288

|

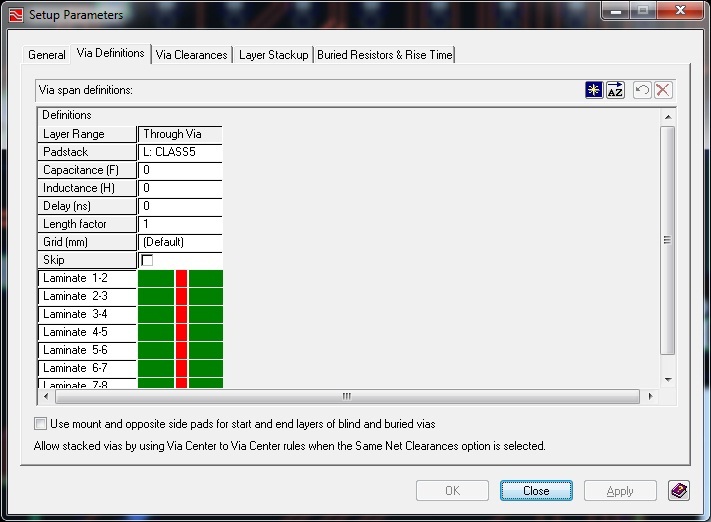

Добрый день! Подскажите как можно учесть время прохождения / длину сигнала через переходное отверстие в CES, необходимо для разводки DDR3. Нашел в настройках возможность задать это значение через все переходное отверстие - setup/setup parameters/via definitions  Но вот если проводник из первого слоя переходит в третий CES все равно учитывает как будто он через все переходное прошел.

|

|

|

|

|

|

|

|

Jan 16 2013, 11:21 Jan 16 2013, 11:21

|

Гуру

Группа: Свой

Сообщений: 7 946

Регистрация: 25-02-05

Из: Moscow, Russia

Пользователь №: 2 881

|

Цитата(EvilWrecker @ Jan 16 2013, 15:08)  2) Есть скажем группу резисторов установленных на плате, но не разведенных. Можно ли осуществить следующее- и если да, то как:

-в схемном редакторе меняю например типоразмер с 0402 на 0805

- в псб редакторе положение сохранется с учетом зазоров/правил, но футпринт меняется Оно примерно так и работает само по себе. Меняете атрибуты компонента в схеме - part number, part name, cell name, PKG_TYPE (два последних можно просто убить). Потом, после forward annotation получаете обновление платы, где новые целлы оказываются по старым координатам, причем даже если уже и разведенные были.

|

|

|

|

|

|

|

|

Jan 16 2013, 13:07 Jan 16 2013, 13:07

|

Участник

Группа: Участник

Сообщений: 57

Регистрация: 7-11-10

Из: Киев

Пользователь №: 60 702

|

При трансляции библиотеки из DC в DxD выдает ошибку " Unable to reserve partition 'CAN'. It is already reserved by 'Имя_Пользователя@Имя_Компютера:Part Editor::Library Manager' " Имя_ Компьютера - соответствует имени другого компьютера домена

Как решить данную проблему?

Сообщение отредактировал LeDima - Jan 16 2013, 13:12

|

|

|

|

|

|

|

|

Jan 16 2013, 14:04 Jan 16 2013, 14:04

|

Частый гость

Группа: Свой

Сообщений: 118

Регистрация: 9-12-12

Из: Курск

Пользователь №: 74 767

|

Такая же проблема была, вот не помню как решилось, но что то очень простое. То ли read-only флаг убрал со всех файлов в библиотеке, то ли файлик она там создает текстовый со словом lock в названии. Его надо убрать. Попробуйте всю библиотеку скопировать в другую папку и поиздевайтесь на ней.

--------------------

улыбаемся ...

|

|

|

|

|

|

|

|

Jan 16 2013, 15:48 Jan 16 2013, 15:48

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(EvilWrecker @ Jan 16 2013, 15:08)  У меня совершенно нубские вопросы:

1) Имеются два компонента на разных слоях- но расположенных друг на другом. Как не выделяй- все время выбирается компонент на верхнем слое. Как правильно выделит ьс первого раза компонент на нижнем? В диалоге Place_Part_&_Cell установите активным только тот слой на котором размещен данный компонент (Bottom), тоже самое через галочку в Display_Control (Placement layers). Цитата(LeDima @ Jan 16 2013, 17:07)  При трансляции библиотеки из DC в DxD выдает ошибку " Unable to reserve partition 'CAN'. It is already reserved by 'Имя_Пользователя@Имя_Компютера:Part Editor::Library Manager' " Имя_ Компьютера - соответствует имени другого компьютера домена

Как решить данную проблему? LM меню Setup>Unreserve_Partitions Если не поможет, то удалить файл Sysindex.cbf и далее пересобрать ЦБ открытием в LM

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

Jan 16 2013, 20:28 Jan 16 2013, 20:28

|

Частый гость

Группа: Участник

Сообщений: 104

Регистрация: 21-12-06

Пользователь №: 23 770

|

Помогите решить проблему.

Имеется проект состоящий из 2 плат. После разных корректировок и исправлений первая плата открывается нормально, проходит и прямая и обратная аннотация. А вторая нет. Идет попытка восстановления из бэкапа и выдается ошибка:

Error: Unable to find padstack '0,2/0,4' for via range 1 to 10.

Error: Unable to load design (G:\Work\Mentor\MZP_14\MZP_14_160113\Board2_PCB\Work\Layout_Temp\LayoutDB.lyt). Padstack missing from Padstack partition. No padstack called "0,2/0,4" defined for via layer range 1 - 10

Библиотека одна и такой падстек в ней есть. Непонятно еще то, что данная плата имеет 4 слоя, зачем ей падстек на 10 слоев ?

--------------------

Затравленный и прижатый к стене кот превращается в тигра. Мигель Сервантес.

|

|

|

|

|

|

|

|

2 чел. читают эту тему (гостей: 2, скрытых пользователей: 0)

Пользователей: 0

|

|

|