| |

RS-232 + FPGA RS-232 + FPGA |

|

|

|

|

May 18 2006, 20:52 May 18 2006, 20:52

|

Местный

Группа: Свой

Сообщений: 253

Регистрация: 28-08-04

Из: Ленинград

Пользователь №: 562

|

Доброго времени суток, уважаемые. Есть задача: между платой и датчиками существует RS-232 канал, точнее 3 канала в направлении от платы к датчикам и 3 - противоположном. Цель - обеспечить работоспособность этой связки. В качестве ядра системы предполагаю использовать FPGA (естественно не только для целей обмена с датчиками). Если Я правильно понимаю, то придется ставить внешние микросхемы (типа MAX220–MAX249) для преобразования уровней TTL <-> RS-232. Остается дело за малым - реализовать в системе приемопередатчики. С этого момента постараюсь раскрыть проблему более подробно. С передатчиком более-менее понятно: типичный Serializer с двумя регистрами и одним PLL (старт_бит:байт_данных:контроль:стоп_бит и все это наружу). С приемником сложнее: только deserializer'ом, наверное, обойтись не получится  В классическом представлнии (в соответствии с остаточными знаниями, полученными в ВУЗе) приемник должен запустить свой внутренний генератор (работающий с частотой, например, в 16 раз превышающей бодовую) после обнаружения на линии перехода сигнала с 1 в 0, т.е. обнаружения старт-бита. Через 8 импульсов после этого события еще раз проверяем состояние линии, и если там 0, то считаем что пришел старт-бит. Далее входной поток мереем через каждые 16 тактов (т.е. с бодовой скоростью), предположительно попадая на середину бита. Записав биты в регистр, проверяем четность, наличие стоп-бита и все по-новой. Помимо попытки вычисления значения бита в середине интервала, Я встречал еще в литературе варианты когда в битовом интервале производится 3 выборки и по мажоритарному принципу определяется значение. Теперь к вопросу реализации: Вариант 1. Брать внешнюю миросхему с реализованным UART'ом. Вроде Intel 8251 для этих целей используется в качестве внешнего устрйоства процессора. Есть и встроенные в корпус МК UART'ы, но ставить МК на плату только ради этих целей как-то нелепо. Кстати, а существует ли вариант, объединяющий UART с драйвером RS-232? Вариант 2. Самому делать на FPGA. В этом случае Я вижу несколько проблем: - как мне осуществить "запуск" генератора приемника при обнаружении старт-бита? - т.к. мне требуется реализовать 3 передатчика и 3 приемника RS-232, и скорее всего эти каналы будут работать независимо друг от друга, то вроде как получается, чересчур большие затраты по количеству PLL-ресурсов. Как бы не вышло, что придется ставить несколько ПЛИС... Нашел в закромах VHDL код UART'а (прикладываю в тему). Бегло просмотрев код, выявил для себя одну интересную вещь - там используется CLK в 4 раза быстрее бодовой скорости, производится выборка значения бита 3 раза за интервал. Т.е. если вдвинутое из Rx-линии в трехразрядный регистр значение = 000, то считаем, что пришел старт-бит. Далее - по алгоритму. Насколько такой способ отражает реальные потребности реализации? Влиять на UART на стороне датчиков не представляется возможным. Всвязи с этим непонятно, будет ли всегда данные от датчика адекватно приниматься в FPGA'шный приемник. И еще - встречал в каких-то статьях, что в FPGA встраиваются блоки SERDES. В hepl'е Quartus'а говорится что вроде как в Stratix'е есть такая возможность. Кто-нибудь работал с ними? И не слишком ли "жирно" будет использовать такие SERDES для 115 Кбит/с? Быть может Я делаю из РПГ-18 (гранатомет "муха") слона, и задача решается современными средствами намного проще? Вообщем если у кого есть опыт общения с датчиками по RS-232, то просьба поделиться знаниями. P.S.: Резюмируя вышесказанное, прошу по возможности ответить на следующие вопросы: 1. Применяются ли сейчас отдельные микросхемы UART'ов? Есть ли варианты UART+драйвер RS-232 в одном корпусе? 2. Обязательно ли использовать PLL для этой задачи? 3. Приложенный VHDL код UART'а (или аналогичный ему) может гарантировать правильный обмен информацией? 4. К месту ли применение аппаратных встроенных в ПЛИС блоков SERDES? 5. Есть ли у кого опыт решения похожей задачи?

Прикрепленные файлы

hUART.zip

hUART.zip ( 2.07 килобайт )

Кол-во скачиваний: 303

--------------------

Лень - это не врожденное чувство русского человека, а средство борьбы с неуемной, но бестолковой энергией начальника.

|

|

|

|

|

|

|

|

Ответов

(45 - 59)

|

|

Jul 13 2006, 00:42 Jul 13 2006, 00:42

|

Местный

Группа: Участник

Сообщений: 290

Регистрация: 18-02-06

Пользователь №: 14 469

|

Цитата(NiOS @ Jul 12 2006, 18:05)  1. Да согласен - есть лишний такт на выходе МЖФ, впесто простого assign <wire>=...

Но он ничего не меняет в алгоритме. Он нужен тк FPGA - "любит" синхронный дизайн. Если любит, то почему бы тогда конвеер из 10-ти лишних тактов не впиндюрить. Или из 100? Кашу маслом не испортишь. Цитата(NiOS @ Jul 12 2006, 18:05)  2. Счетчик я использую только, чтобы считать отсчеты (до 3х) внутри бита. Так, значит счётчик сэмплов всё-таки сущетвует. Можно конечно делать выборку с каждым отсчётом и потом голосовать. На мой взгдяд -- параноя. Проще выбирать один раз в серёдке, как все делают. Дополнительные биты как раз употребить счётчик 4-х битный. Да и без разницы наверное, что делать многобитный делитель основной частоты до 3х baudrate или перекинуть пару бит из него на SampleCnt для 16х baudrate, а точность вычисления центра битового интервала повысится. Цитата(NiOS @ Jul 12 2006, 18:05)  САМИ биты я не считаю! Как можно не считая биты узнать, что кадр окончился? Цитата(NiOS @ Jul 12 2006, 18:05)  А есть ли смысл разговаривать с человеком, который даже не удосужился перед ответом "не слышал" попробовать посмотреть в любои поиске слово "стробирование".  А особено который имеет дело с ПЛИС!! В моём поримании, стробирование = выборка, стробирующий сигнал -- синхросигнал. Какое отношение данный процесс имеет к ФНЧ я совершенно не представляю. Вообще, каждый вкладывает свой смысл в данное слово. Так что разъяснение. Особенно это отноится любителям изобретать собственные термины вроде "бодовыех байтов". Но раз уж они обижаются на просьбу о разъяснении смысла своих мудрёных слов, предпочитая вместо этого удар промеж глаз, я умываю руки. Себя по голове ударь. Цитата TO NIOS:

А не могли бы Вы привести схему Вашего приемника. Для ознакомления. Ведь она явно отлична от классического представления. И на словах ничего не понятно. Во-во, мозги всем запарил якобы оригинальной простотой своей схемы, магическим сдвигом, не требующим синхронизации и счётчиков, когда на самом деле она содержит лишние компоненты.

|

|

|

|

|

|

|

|

Jul 13 2006, 08:01 Jul 13 2006, 08:01

|

Знающий

Группа: Свой

Сообщений: 601

Регистрация: 1-03-05

Из: Spb

Пользователь №: 2 972

|

Цитата(sazh @ Jul 12 2006, 22:45)  TO NIOS:

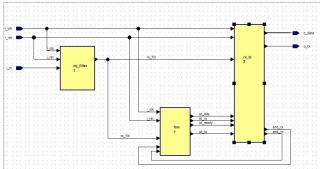

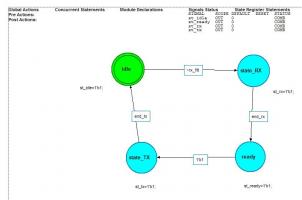

А не могли бы Вы привести схему Вашего приемника. Для ознакомления. Ведь она явно отлична от классического представления. И на словах ничего не понятно. Привожу проект. Но тк это был мой первый пробный проект, то я в нем отрабатывал саму идею реализации. Поэтому это не универсальный стандарт RS232, а конкретная задача, правильность выполнения в живую проверялась в HyperTerminale Винды. Задача: скорость 115200, без паритета, 8 байт, один стоповый. Принимаем "байт" от компа -> суммируем с предыдущим принятым "байтом" и отправляем результат обратно в комп. На компе контролируем правильность работы по сумме скан-кодов. Схема блоками (наглядная) (МЖФ входной, FSM и "общий блок")

Р В Р’ВзображенРСвЂР В Р’Вµ СѓРСВеньшено

(67.65 килобайт)

|

Простой FSM (в графике наглядней)

Р В Р’ВзображенРСвЂР В Р’Вµ СѓРСВеньшено

(33.13 килобайт)

|

Сам код "Общего блока" - по нему наврное будет больше всего вопросов(коментил мало) - задавайте. Код parameter T = 1;

//Mj_filter bitov--------------------------------------------

wire en_bit;

reg [2:0] dd;

always @ (posedge i_rst or posedge i_clk)

if (i_rst)

dd[2:0] <= #T 3'b111;

else if (en_bit)

dd[2:0] <= #T {dd[1:0], rx_filt};

reg rx_bit;

always @ (posedge i_rst or posedge i_clk)

if (i_rst)

rx_bit <= #T 1'b1;

else if (en_bit)

rx_bit <= #T (dd[0]&dd[1])|(dd[0]&dd[2])|(dd[1]&dd[2]);

//End Mj_filter bitov-----------------------------------------

//Counter clk - Из 40МГЦ получает утроенную 115200

reg [7:0] cnt;

always @ (posedge i_rst or posedge i_clk)

if (i_rst)

cnt[7:0] <= #T 8'h0;

else if (cnt[7:0] == 8'd144 ) cnt[7:0] <= #T 8'h0;

else

cnt[7:0] <= #T cnt[7:0] + 8'h1;

//------------------------------------------------------------

//Counter 3x i_clk

reg [1:0] cnt_bit;

always @ (posedge i_rst or posedge i_clk)

if (i_rst)

cnt_bit[1:0] <= #T 2'h0;

else if (cnt_bit[1:0] == 2'h3) cnt_bit[1:0] <= #T 2'h0;

else if ((st_rx | st_tx) & cnt==7'd114)

cnt_bit<=#1 cnt_bit + 1;

//----------------------------------------------------------------

// Main Block

reg [9:0]rx_tx; // Типа общего сдвигового регистра для передачи и приема

reg [7:0] rx_reg; // Регистр для хранения предыщего принятого значения, с которым симмирется нынешнее (циклически)

always @ (posedge i_rst or posedge i_clk)

if (i_rst) begin

rx_tx[9:0] <= #T 10'h0;

rx_reg[7:0]<= #T 8'h0; // Save RX data

end

else if(st_idle)

rx_tx <= #T 10'h3ff;

else if(st_rx & cnt_bit==2'h3)

rx_tx[9:0] <= #T {rx_bit,rx_tx[9:1]};

else if(st_ready) begin

rx_reg[7:0]<= #T rx_tx[8:1] + rx_reg[7:0];

rx_tx[8:1] <= #T rx_reg[7:0];

end

else if(st_tx & cnt_bit==2'h3)

rx_tx[9:0] <= #T {1'b1,rx_tx[9:1]};

//---------------------------------------------------------------

//

assign en_bit = (st_rx & cnt==7'd114) ? 1'b1:1'b0;

assign end_rx = (st_rx & rx_tx[0]==1'b0 & rx_tx[9])?1'b1:1'b0;

assign end_tx = (rx_tx[9:0] == 10'h3ff & st_tx) ? 1'b1:1'b0;

assign o_tx = (st_tx)?rx_tx[0]:1'b1;

//---------------------------------------------------------------

assign o_data[3:0] = rx_reg[3:0]; И общий проект модуль на Verilog  RS232.zip

RS232.zip ( 1.45 килобайт )

Кол-во скачиваний: 271PS Принимаются замечания по стилю описания на Verilog!!! Совершенству - нет предела.

--------------------

Насколько проще была бы жизнь, если бы она была в исходниках

|

|

|

|

|

|

|

|

Jul 13 2006, 10:02 Jul 13 2006, 10:02

|

Знающий

Группа: Свой

Сообщений: 601

Регистрация: 1-03-05

Из: Spb

Пользователь №: 2 972

|

Цитата(sazh @ Jul 13 2006, 13:46)  Сам текст понятен. А вот идея всегда будет вызывать споры. Да и кто, когда будет reset нажимать. reset должен быть, потомучто нету такого блока (для не SRAM ПЛИС проект) Я для этого и опубликовал, предполагая, что со стороны Вы (в полной мере) сможет обозначить узкие моменты самого алгоритма тк я прикинул много сложных вариантов и всегда находил из них выход в моем алгоритме. Мне он кажется проще - избавились от некоторых критичных элементов (хотя бы точность определения старта) Кста на AHDL я (как и Вы) тоже прием кадра разворачивл временой диаграмой по счетчикам - мне тоже нравится так. Но на Verilog'e решил попробовать по-другому - идейку подкинули про МЖФ -> и получилось

--------------------

Насколько проще была бы жизнь, если бы она была в исходниках

|

|

|

|

|

|

|

|

Jul 13 2006, 12:32 Jul 13 2006, 12:32

|

Местный

Группа: Участник

Сообщений: 290

Регистрация: 18-02-06

Пользователь №: 14 469

|

Теперь понял. Отслеживалка числа принятых битов совмещёна в сдвиговом регистре с данными. Прежде не доходило, как такое возможно, хотя протогол rs232 основан на этой идее. В таком случае отдельный счётчик бит действительно не нужен.  Но. Попробуте как я грузить битики данных с rs232 прямо в регистр контроллера (контроллер -- набор регистров команд с логикой для управления FPGA системой, команды принимаются по с компьютера по rs232). Придётся выход каждого регистра инициализировать единицами и снабжать выходной связью на rs232 приёмник, ведь стартовый бит будет путешествовать каждый раз по новому регистру. Куча регистров -- много нелокальных связей. Компактный счётчик возле rs232-автомата выйдет дешевле. К тому же совершенно не обязательно, что все загружаемые таким непосредственным образом регистры будут 8-битные. Да и сам сброс в единицы как реализуется? 9 мультиплксоров подле каждой ячейки данных выбирают между 1 и shift_in. Может 3-битный счётчик принятых битов всё же экономнее? Цитата идейку подкинули про МЖФ -> и получилось А они не объяснили -- на фига МЖФ, если без него работает идеально надёжно?

|

|

|

|

|

|

|

|

Jul 13 2006, 14:48 Jul 13 2006, 14:48

|

Знающий

Группа: Свой

Сообщений: 601

Регистрация: 1-03-05

Из: Spb

Пользователь №: 2 972

|

Цитата(sazh @ Jul 13 2006, 14:13)  Reset не обязателен. Этот ресет нужен обязательно при включении питания ПЛИС, а не для проекта. (я же говорю это НЕ SRAM-ПЛИС, а флеш) Подается от простого монитора питания, когда установилось. кста про четверть такта "0" - он и не поймет что был ноль - так и будет единица. А вот если >=2/3 такта "0", тогда есть вероятность что схватит "левый старт". Но ваш метод тоже схватит "левый ноль" >=1/2 такта - он же проверит снова в середине -> и будет принимать ...

--------------------

Насколько проще была бы жизнь, если бы она была в исходниках

|

|

|

|

|

|

|

|

Jul 18 2006, 09:08 Jul 18 2006, 09:08

|

Знающий

Группа: Свой

Сообщений: 601

Регистрация: 1-03-05

Из: Spb

Пользователь №: 2 972

|

Цитата(sazh @ Jul 13 2006, 20:49)  Этот ресет нужен обязательно при включении питания ПЛИС, а не для проекта. (я же говорю это НЕ SRAM-ПЛИС, а флеш)

Подается от простого монитора питания, когда установилось./////

А вот это уже интересно. Причем тут включение плис, и тем более его структура. Это работает на любой структуре Альтеры, у Xilinx работал только на FPGA 3000 тысячнике без всяких там прммитивов установки сетапов.

Если речь об Эктел, снимаю шляпу. Такой хоккей нам не нужен. Что-то вы не сразу догадались про определение не SRAM-ПЛИС  Не сталкивались видать... Там просто нет цепей сброса по причине того, что универсальная ячейка может быть как тригером так и логической функцией.

--------------------

Насколько проще была бы жизнь, если бы она была в исходниках

|

|

|

|

|

|

|

|

Jul 19 2006, 06:52 Jul 19 2006, 06:52

|

Знающий

Группа: Свой

Сообщений: 601

Регистрация: 1-03-05

Из: Spb

Пользователь №: 2 972

|

Цитата(sazh @ Jul 18 2006, 22:57)  Что-то вы не сразу догадались про определение не SRAM-ПЛИС

Не сталкивались видать... Там просто нет цепей сброса по причине того, что универсальная ячейка может быть как тригером так и логической функцией./////

Я не стал догадываться. Еще раз повторю. Нет необходимости в цепях сброса. Не имеет значения в каком состоянии все триггеры по включению. Дались Вам эти нули. Система сама должна переходить в начальное состояние при наличии в линии 1. И при этом подстраивать свои внутренние часы по каждому стопу. Иначе грош цена такой схеме. Не думаю, что хорошая идея завязыватся на сигнал 1 на линии. От него ничего толового не сделать. Я же написал, что Вы правильно предположили производителя ПЛИС - поэтому сигнал сброса нужен по-определению(поверьте!). А по подстраивание по стопу я не понял - или, если это Вы совместно с начальным состоянием при наличие 1 на линии - то я про это уже написал.

--------------------

Насколько проще была бы жизнь, если бы она была в исходниках

|

|

|

|

|

|

|

|

Sep 26 2006, 09:15 Sep 26 2006, 09:15

|

Участник

Группа: Новичок

Сообщений: 20

Регистрация: 31-08-06

Пользователь №: 19 985

|

Цитата(NiOS @ May 20 2006, 21:49)  Для чего брать частоту больше раз в 8, чем бодовая??? Я же писал, что нужна частота только в 3!!! раза больше, чем бодовая, один МЖФ, ну и второй МЖФ для фильтрации входа.

Могу привести код работающего проекта на Verilog’e (хотя он только для скорости 115.200, без проверки паритета и с одним стоповым)

Как это происходит (повторяюсь и уточняю).

При входе сигнала RX (UART’a) постоянно работающий входной МЖФ– для фильтрации коротких пичков на линии. Принцип работы МЖФ - из трех последовательных отсчетов он выбирает 2 совпадающих.

А дальше счетчик работающий от основной частоты 40 МГц считает до ‘d114 и сбрасывается – получается частота 3*бодовая (крутится постоянно без сброса по стартовому биту!)

А теперь, как счетчик == 114 я на один такт разрешаю продвинуть данные во втором МЖФ.

Мне без разнице, в какой части «бодового» бита, на МЖФ защелкнутся три значения (может даже одно значение попасть из другого «бодового» бита, а может попасть на перепад(в обычном RS-232 он пологий получается) – для такого подхода это «фиолетово») -> а второй счетчик считает, когда (первый счетчик==114) уже 3 раз и на выходе второго МЖФ получаю значение «бодового» бита, которой и вдвигаю.

Когда автомат, находясь в «idle», получил значение «бодового» бита «0» -> это стартовый -> задвигаю в регистр [9:0] (в «idle» инициализированный всеми «1») -> как стартовый «0» добрался до конца регистра [9:0] -> всё посылка принята!

И не нужна НИКАКАЯ синхронизация при стартовом бите, и внутри бита – просто по двум из трех значений определяется значение бита.

Дописал - посмотрел – слов много, а объяснил ли?

В общем, если что не понятно на буднях смогу привести код (это более универсальный язык =8) ) Спасибо большое за идею(или даже за решение). Сделал как Вы советуете - работает как часы.  Упс. Тут уже даже код появился. Я правда все равно в VHDL писал  Сообщение отредактировал sanek78 - Sep 26 2006, 09:27

Сообщение отредактировал sanek78 - Sep 26 2006, 09:27

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|