| |

|

|

Синтезаторы частот. От концепции к продукту. Синтезаторы частот. От концепции к продукту., Ищу книгу, Frequency Synthesizers: Concept to Product |

|

|

|

|

Jan 2 2017, 21:43 Jan 2 2017, 21:43

|

Узкополосный широкополосник

Группа: Свой

Сообщений: 2 316

Регистрация: 13-12-04

Из: Moscow

Пользователь №: 1 462

|

Цитата(Chenakin @ Jan 2 2017, 02:38)  С ЛЧМ должно быть проще, т.к. частота (фаза) растет относительно медленно (без рывков). А что если в этот режим ввести некую инерционность, которая не даёт резко рвать фазу. Например: 1. На выходе блока(ов) апконверсии-очистки-фильтрации-коммутации поставить повторитель-ФАПЧ (N=1) с петлёй в несколько МГц (за что боролись  ). Смысл в том, что ГУН/фильтр будет затягивать фазу с нужной динамикой. 2. На выходе …(см. выше)… поставить DDS в качестве делителя на 2. Смысл, собственно, не в самом DDS, а в ФНЧ, который будет сглаживать отсчеты, убирая фазовые рывки. 3. Что ещё? Прежде чем бороться с разрывом фазы, нужно понимать, важно абсолютное значение фазы на каждом шаге. Если нет возможности избежать переходных процессов при переключении частоты, то нужно гасить последствия модуляцией амплитуды (отключением). Лучше конечно модуляцией, по определенному закону, чтобы не усугублять ситуацию. Без входа синхронизации у делителя, остается только измерять фазу на выходе, и по результату вносить добавку на фазовращателе. Мне этот вариант не нравится, поскольку возвращаемся к системе с обратной связью, да и точность установки фазы гробится, она существенно хуже цифровой, которую дает сам DDS. Цитата(Chenakin @ Jan 2 2017, 02:38)  А в итоге? Удалось решить проблему? Да, все решается. Путем некоторого усложнения схемы, поскольку без синхронизации не исключается вероятность расхождения фаз в полифазной системе. Цитата(Chenakin @ Jan 2 2017, 02:38)  Противоречие. Если дополнительный DDS (используемый в качестве делителя) рвет фазу, то и ведущий (который задает шаг) будет делать тоже самое. Тогда уж совсем приплыли. Без FPGA не обойтись. Цитата(Chenakin @ Jan 2 2017, 02:38)  Какие требования будут к фазе? Определение когерентности? Rloc, тут Вы бы могли многое прояснить. А когда задача сформулирована, то дальше уже дело техники. Интересно было б построить универсальный интструмент (модуль), который бы закрывал много разных применений, ведь основа внутри очень мощная закладывается. Пока понятие когерентности ввел по аналогии с радиолокацией, где ФАПЧ невозможно использовать при переключении частоты, рассыпается обработка, основанная на фазовых соотношениях. Не могу пока формализовать в количественном виде. Интуитивно, разница состоит в законе установления конечной частоты (фазы).

|

|

|

|

|

|

|

|

Jan 11 2017, 20:25 Jan 11 2017, 20:25

|

Местный

Группа: Участник

Сообщений: 394

Регистрация: 7-01-11

Из: г. Трубчевск

Пользователь №: 62 074

|

Цитата(VCO @ Jan 8 2017, 23:36)  Пршу прощения у администрации форума, Виталия Козлова и Александра Ченакина за неуместный эмоциональный нервный срыв.

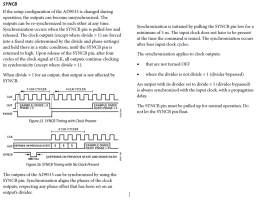

Дальнейшее своё пребывание в этой теме, в Электрониксе и электронике считаю невозможным и бесперспективным. Прощайте. Со всеми бывает. Надеюсь, всё образуется. Не прощаемся и ждём Вас в этой теме; без Ваших комментариев общение не так зажигательно. Только Виталия сильно не забижайте (шутка  ). У него, конечно, PDS уж больно мудреный, но в такие годы это двигать не так просто. Уважаю, что не сдается. Ну а пока, давайте ДДС вместе добьем, хотя бы в концепте. Цитата(dm.pogrebnoy @ Jan 2 2017, 06:08)  Существует техника построения DDS с непрерывным временем. Красивая картинка. Самое оно. Цитата(rloc @ Jan 2 2017, 13:43)  Без входа синхронизации у делителя, остается только измерять фазу на выходе, и по результату вносить добавку на фазовращателе. Мне этот вариант не нравится, поскольку возвращаемся к системе с обратной связью, да и точность установки фазы гробится, она существенно хуже цифровой, которую дает сам DDS. Согласен. Мне тоже это никак не нравится. Цитата(rloc @ Dec 30 2016, 03:52)  И еще как вариант FPGA + внешний триггер. Kintex7 работает на скоростях 1866+ Mbps в двунаправленном режиме, только на выход - немного больше. Шумы будут определяться внешним триггером, плюсом к этому - быстрота переключения и синхронизация, что во многих случаях является ключевым моментом (не все делители имеют вход сброса, а еще лучше - вход внешней синхронизации). ПЛИС хорошо использовать в качестве интерфейса-передачи данных (т.е. изолированная цифровая часть). Не хотелось бы использовать в качестве RF-компонента (делителя). Делитель нужен для подавления спур до очень низких величин. А как скажется влияние ПЛИС в этом случае (Вы сами не раз говорили о проблеме ЭМС)? Цитата(rloc @ Dec 30 2016, 03:52)  Вопрос к Александру и Сергею: каким образом контролировать фазу делителя в схеме апконверсии с делением? Ведь после смены коэффициента деления фаза на выходе получается случайной. Цитата(Sergey Beltchicov @ Dec 30 2016, 13:36)  Да уж  это подстава. Насколько я понял, у линеаровского семейства LTC6954 есть система выравнивания фаз выходов делителей как одной микросхемы Вернёмся к AD9515. Там есть функция SYNCB для синхронизации выхода (см. стр. 18-19). Можно ли этим как-то воспользоваться?  AD9515.pdf

AD9515.pdf ( 462.47 килобайт )

Кол-во скачиваний: 26

Уменьшено РґРѕ 83%

972 x 753 (311.72 килобайт)

|

--------------------

|

|

|

|

|

|

|

|

Jan 12 2017, 08:10 Jan 12 2017, 08:10

|

Узкополосный широкополосник

Группа: Свой

Сообщений: 2 316

Регистрация: 13-12-04

Из: Moscow

Пользователь №: 1 462

|

Цитата(Chenakin @ Jan 11 2017, 23:25)  ПЛИС хорошо использовать в качестве интерфейса-передачи данных (т.е. изолированная цифровая часть). Не хотелось бы использовать в качестве RF-компонента (делителя). Делитель нужен для подавления спур до очень низких величин. А как скажется влияние ПЛИС в этом случае (Вы сами не раз говорили о проблеме ЭМС)? С внешним триггером ПЛИС как раз и выполняет роль интерфейса передачи данных, которые пересинхронизируются чистым тактовым сигналом триггера. Для более низких частот (до 500 МГц) такой вариант опробован. Остается избавиться от ФАПЧ, который компенсирует задержки распространения буферов ввода/вывода ПЛИС. Есть еще один вариант обхода проблемы случайной фазы делителя - использовать несколько переключаемых делителей. Но здесь стоит вопрос в развязке. Цитата(Chenakin @ Jan 11 2017, 23:25)  Вернёмся к AD9515. Там есть функция SYNCB для синхронизации выхода (см. стр. 18-19). Можно ли этим как-то воспользоваться? Вроде можно. Достаточно древний делитель со специфическим управлением: Цитата Device configured with 4-level logic pins И частоту желательно побольше.

|

|

|

|

|

|

|

|

Jan 12 2017, 12:31 Jan 12 2017, 12:31

|

Знающий

Группа: Участник

Сообщений: 620

Регистрация: 4-12-09

Из: Kiev

Пользователь №: 54 052

|

Цитата(Chenakin @ Jan 11 2017, 23:25)  Со всеми бывает. Надеюсь, всё образуется. Не прощаемся и ждём Вас в этой теме; без Ваших комментариев общение не так зажигательно. Только Виталия сильно не забижайте (шутка  ). У него, конечно, PDS уж больно мудреный, но в такие годы это двигать не так просто. Уважаю, что не сдается. Ну а пока, давайте ДДС вместе добьем, хотя бы в концепте. Ну да, Виталий мол-де старый, тронулся умом и упёрса в свой PDS. Да, конечно, невозможно мне одному двигать идею дальше. Но жалеть меня не надо. Я вижу перспективу и потому упёрся. Работоспособность идеи показана на макете, а потенциальные возможности промоделированы (см. сообщение 2223). Результаты макетирования посредственные из-за использования примитивного ЦАП. Кто-то здесь на Форуме, кажется, rloc, предложил использовать 2 стандартных ЦАП. Давно это было, тогда понял как это сделать, а теперь стёрлось в памяти. Найти это среди тьмы сообщений практически невозможно. Добрый человек, прошу, повторите.

|

|

|

|

|

|

|

|

Jan 12 2017, 13:16 Jan 12 2017, 13:16

|

Местный

Группа: Участник

Сообщений: 257

Регистрация: 22-12-10

Пользователь №: 61 804

|

Цитата(Chenakin @ Jan 11 2017, 23:25)  Вернёмся к AD9515. Там есть функция SYNCB для синхронизации выхода (см. стр. 18-19). Можно ли этим как-то воспользоваться? Судя по описанию, если при каждой смене кэффициента деления подавать ноль на эту ногу, то через четыре такта клока сигналы на выходах делителей будут снова в фазе. Просто появятся дополнительные накладные временные расходы, которые придется заложить во время перестройки. Попутно вопрос: а будет ли рваться фаза при одном фиксированном коэффициенте деления (когда свипируется только частота на входе делителя)? И рвется ли фаза при работе СВЧ переключателей? И еще вопрос: как правильно реализовать широкополосную I/Q модуляцию в подобном прямосинтезном генераторе? Будут ли ограничения (и какие?) со стороны блоков апконверсии/фильтрации/делительной очистки?

|

|

|

|

|

|

|

|

Jan 12 2017, 19:47 Jan 12 2017, 19:47

|

Местный

Группа: Участник

Сообщений: 394

Регистрация: 7-01-11

Из: г. Трубчевск

Пользователь №: 62 074

|

Цитата(Vitaly_K @ Jan 12 2017, 04:31)  Я вижу перспективу и потому упёрся. Поэтому и отношусь с симпатией и к Вашей идее, и к Вашей упёртости. Цитата(Vitaly_K @ Jan 12 2017, 04:31)  Работоспособность идеи показана на макете, а потенциальные возможности промоделированы (см. сообщение 2223). Остаётся ряд нераскрытых моментов: - сложность восприятия метода (я думаю Вы сами смогли здесь в этом убедиться) - более детальное моделирование, например, сходимость метода, т.е. необходимо доказать отсутствие ложных захватов; учет нелинейности ЦАП (тоже, что и в DDS – разного рода нелинейности типа глитчей, переходные процессы, динамические нелинейности и т.д.) - макетирование, которое бы подтвердило не только качественно (захват частоты), но и количественно (спуры, шумы) ценность Вашего метода Цитата(Vitaly_K @ Jan 12 2017, 04:31)  Кто-то здесь на Форуме, кажется, rloc, предложил использовать 2 стандартных ЦАП. Давно это было, тогда понял как это сделать, а теперь стёрлось в памяти. Найти это среди тьмы сообщений практически невозможно. Добрый человек, прошу, повторите. Вы не раз говорили, что нельзя отмакетировать PDS, т.к. нет ЦАП с двумя раздельными тактовыми входами. Возможное решение – суммирование двух раздельных ЦАП (каждый со своим тактовым входом). Цитата(Vitaly_K @ Jan 12 2017, 04:31)  Да, конечно, невозможно мне одному двигать идею дальше. Одно из решений – дипломный проект или (лучше) канд. работа под Вашим руководством. Такая работа предполагает решение ряда задач, а именно: - мат. моделирование - сравнительный анализ (количественный) с конкурирующими методами (fractional-N, offset) - эксперимент (макетирование) с анализом полученных результатов - возможное внедрение метода Т.е. всё то, чего сейчас не хватает. Нужен толковый студент (аспирант), для которого эта работа могла бы стать хорошим трамплином. К сожалению, я сейчас с университетской средой не сильно связан. Но если нужно, мог бы поучаствовать в качестве оппонента, со-руководителя и т.д. – всё, что может оказаться полезным. Цитата(rloc @ Jan 12 2017, 00:10)  Есть еще один вариант обхода проблемы случайной фазы делителя - использовать несколько переключаемых делителей. Но здесь стоит вопрос в развязке. Просьба пояснить. Допустим, вопрос развязки решили. Если у нас есть два (несколько) переключаемых делителей, то они будут расфазированы по той же самой причине. Т.е. надо осуществлять их начальную фазировку? Тогда в чем преимущество? Цитата(rloc @ Jan 12 2017, 00:10)  Вроде можно. Достаточно древний делитель со специфическим управлением: По-видимому, чтобы сократить кол-во выводов в микросхеме. В результате нужно заводить по две линии на ногу с кучей резисторов. Неудобно, но что делать. Цитата(rloc @ Jan 12 2017, 00:10)  И частоту желательно побольше. Мне как раз подходит. Шумы бы поменьше, но тут уж дареному коню… Цитата(Sergey Beltchicov @ Jan 12 2017, 05:16)  Судя по описанию, если при каждой смене кэффициента деления подавать ноль на эту ногу, то через четыре такта клока сигналы на выходах делителей будут снова в фазе. Просто появятся дополнительные накладные временные расходы, которые придется заложить во время перестройки. По описанию минимальная длина сигнала SYNCB равна 5 нс. Четыре такта на 1 ГГц (к примеру) – это 4 нс. Т.е. накладные расходы порядка 10 нс? Вполне терпимо. Вроде ”подставу” обходим? Теперь по реализации. Правильно ли я понимаю, что делитель A мы используем как time reference (т.е. его к-т деления не меняется, фактически канал нигде не используется), а делитель B (рабочий в блоке очистки) после каждого перепрограммирования будем перефазировать, посылая короткий импульс на SYNCB. Вроде всё правильно? Цитата(Sergey Beltchicov @ Jan 12 2017, 05:16)  Попутно вопрос: а будет ли рваться фаза при одном фиксированном коэффициенте деления (когда свипируется только частота на входе делителя)? Я так понимаю, что нет. Цитата(Sergey Beltchicov @ Jan 12 2017, 05:16)  И рвется ли фаза при работе СВЧ переключателей? Сам переключатель фазу рвать не должен (за вычетом нескольких нс на переключение). Тут вопрос – что будет переключаться (какие сигналы/фазы). Цитата(Sergey Beltchicov @ Jan 12 2017, 05:16)  И еще вопрос: как правильно реализовать широкополосную I/Q модуляцию в подобном прямосинтезном генераторе? Будут ли ограничения (и какие?) со стороны блоков апконверсии/фильтрации/делительной очистки? O! Это классная тема - отдельная и не менее ёмкая, чем сам прямой синтез. Конверсия (up/down) IQ-модуляцию не меняет (сохраняет). Деление не сохраняет (т.к. искажает амплитудную составляющую). Т.е. IQ должна быть сформирована уже после всех делений.

Сообщение отредактировал Chenakin - Jan 12 2017, 20:38

--------------------

|

|

|

|

|

|

|

|

Jan 13 2017, 07:57 Jan 13 2017, 07:57

|

Узкополосный широкополосник

Группа: Свой

Сообщений: 2 316

Регистрация: 13-12-04

Из: Moscow

Пользователь №: 1 462

|

Цитата(Vitaly_K @ Jan 12 2017, 15:31)  Результаты макетирования посредственные из-за использования примитивного ЦАП. Кто-то здесь на Форуме, кажется, rloc, предложил использовать 2 стандартных ЦАП. khach предлагал, но действительно найти сложно. Цитата(Sergey Beltchicov @ Jan 12 2017, 16:16)  Попутно вопрос: а будет ли рваться фаза при одном фиксированном коэффициенте деления (когда свипируется только частота на входе делителя)? И рвется ли фаза при работе СВЧ переключателей? При фиксированном - не будет, можно еще поиграться с верхней/нижней частотой. Переключатели влияют только на переходные процессы. Цитата(Sergey Beltchicov @ Jan 12 2017, 16:16)  И еще вопрос: как правильно реализовать широкополосную I/Q модуляцию в подобном прямосинтезном генераторе? Будут ли ограничения (и какие?) со стороны блоков апконверсии/фильтрации/делительной очистки? Если делать модуляцию со стороны DDS, делители убьют амплитудную модуляцию. Вариант с регенеративными делителями думаю не будем рассматривать, из-за сложности реализации. Остается фазо-частотная модуляция. В этом смысле мне нравится "топорная" структура UXG - при использовании активных удвоителей (на ячейке Гильберта) сохраняется полный диапазон для модуляции по амплитуде - это дает возможность реализации не только полноценной I/Q модуляции, но и быстрой перестройки/согласованию по амплитуде при переключении между диапазонами, что может быть равносильно решению проблемы с разрывом фазы. Цитата(Chenakin @ Jan 12 2017, 22:47)  Просьба пояснить. Допустим, вопрос развязки решили. Если у нас есть два (несколько) переключаемых делителей, то они будут расфазированы по той же самой причине. Т.е. надо осуществлять их начальную фазировку? Тогда в чем преимущество? Вместо начальной фазировки можно измерить и потом учесть при формировании. В любом случае, процесс калибровки/настройки однократный и не влияет на быстродействие.

|

|

|

|

|

|

|

|

Jan 14 2017, 16:28 Jan 14 2017, 16:28

|

Знающий

Группа: Участник

Сообщений: 620

Регистрация: 4-12-09

Из: Kiev

Пользователь №: 54 052

|

Цитата(Chenakin @ Jan 12 2017, 22:47)  Поэтому и отношусь с симпатией и к Вашей идее, и к Вашей упёртости.

Спасибо.

Остаётся ряд нераскрытых моментов:

- сложность восприятия метода (я думаю Вы сами смогли здесь в этом убедиться)

- более детальное моделирование, например, сходимость метода, т.е. необходимо доказать отсутствие ложных захватов; учет нелинейности ЦАП (тоже, что и в DDS – разного рода нелинейности типа глитчей, переходные процессы, динамические нелинейности и т.д.)

- макетирование, которое бы подтвердило не только качественно (захват частоты), но и количественно (спуры, шумы) ценность Вашего метода

Согласен

Вы не раз говорили, что нельзя отмакетировать PDS, т.к. нет ЦАП с двумя раздельными тактовыми входами. Возможное решение – суммирование двух раздельных ЦАП (каждый со своим тактовым входом).

Так это ж я поворял то, что мне посоветовал некто, которого теперь не могу найти на Форуме.

Одно из решений – дипломный проект или (лучше) канд. работа под Вашим руководством. Такая работа предполагает решение ряда задач, а именно:

- мат. моделирование

- сравнительный анализ (количественный) с конкурирующими методами (fractional-N, offset)

- эксперимент (макетирование) с анализом полученных результатов

- возможное внедрение метода

Т.е. всё то, чего сейчас не хватает. Нужен толковый студент (аспирант), для которого эта работа могла бы стать хорошим трамплином. К сожалению, я сейчас с университетской средой не сильно связан. Но если нужно, мог бы поучаствовать в качестве оппонента, со-руководителя и т.д. – всё, что может оказаться полезным.

Обязательно сразу же студент (аспирант)? А если просто сначала толковый специалист, который освоит идею, изложит задачу её исследования, а уж потом с этим обратится в университет за местом в аспирантуре. Не знаю как там делаются диссертации и их защищают, а вот такой, возможно, глупый вопрос: а с готовой диссертацией нельзя прийти в Совет университета и попросить рассмотреть возможность защиты её у них?

Цитата(rloc @ Jan 13 2017, 10:57)  khach предлагал, но действительно найти сложно. Спасибо. Иногда он тут появляется. Подожду, вопрос не срочный.

Сообщение отредактировал Vitaly_K - Jan 14 2017, 16:23

|

|

|

|

|

|

|

|

Jan 15 2017, 16:48 Jan 15 2017, 16:48

|

Знающий

Группа: Участник

Сообщений: 620

Регистрация: 4-12-09

Из: Kiev

Пользователь №: 54 052

|

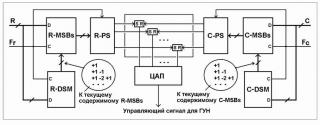

Цитата(khach @ Apr 22 2014, 21:54)  Тяжело было найти описание внутрененй архитектуры. Например тут http://zi.zavantag.com/docs/119/index-253588-15.html?page=4 Рис. 4.7 и около. Основные особенности- код защелкивается по внешену стробу, выходной сигнал может быть задержан на 1-2 периода клока. Выход ЦАПа- дифференциальный токовый. В качестве клока планировал использовать входную частоту синтезатора, возможно после прескалера чтобы частотного диапазона хватило. А код ЦАПа формировать в ПЛИС. Из-за реклокинга внутри TxDAC джиттер внутри ПЛИС не будет ухудшать фазовый шум синтезатора. Специально искал в мусорнике старую платку с двумя микросхемами TxDAC, т.к по блок-схеме синтезатора для двух ЦАПов нужны разные тактовые частоты. Меня данная архтектура синтезатора интересует в плане ускорить переходной процесс в конце процесса перестройки синтезатора, когда частота ГУН уже достаточно близка к заданной- уж очень этот эффект мешает, так что такое усложнение архитектуры синтезатора будет оправдано. Нет, тут что-то не то. Ответа на вопрос нету. Взгляните на прилагаемый рисунок. Углубляться в детали не будем. После фазорасщепителей, опорного RC и сигнального C-PC, импульсы поступают на RS-триггеры. ЦАП – резистивная матрица на выходе триггеров (так в макете). А куда вставлять два стандартных ЦАП, что на них подавать и чем тактировать?

Эскизы прикрепленных изображений

Уменьшено РґРѕ 79%

808 x 315 (35.6 килобайт)

|

|

|

|

|

|

|

|

|

Jan 15 2017, 22:41 Jan 15 2017, 22:41

|

Гуру

Группа: Свой

Сообщений: 3 439

Регистрация: 29-12-04

Пользователь №: 1 741

|

Цитата(Vitaly_K @ Jan 15 2017, 19:48)  А куда вставлять два стандартных ЦАП, что на них подавать и чем тактировать? В этой блок-схеме синтезатора есть системная ошибка- ЦАП считается идеальным, как только нужный код появится на входах, так он и выдаст нужное напряжение. Про гонки между разрядами ЦАП наверно слышали? И про аналоговые глитчи из за гонок на выходе ЦАП тоже. Это и было причиной ухода от асинхронных архитекур ЦАП к синхронным. И даже внутри ИС ЦАП построенный по современным архитектурам будет синхронный. Поэтому на него все равно придется подвести тактовую частоту. Вот какую ее выбрать-вопрос. Предполагалось попробовать использовать опорную частоту и частоту VCO, предварительно поделив ее чтобы попасть в диапазон рабочих частот ЦАП. Т.е каждая половинка синтезатора работает со своей частотой, часто со стороны VCO- с переменной. А суммирование сигналов происходит не в цифре, как в вышеприведенной блок-схеме, а аналогово, после ЦАП. Был еще вариант- использовать готовые модули ФЧД в качестве ЦАП с весовыми коэффициентами для токов соотвественно разряду ЦАП. Тут получалась действительно асинхронная архитектура, но только на рассыпухе. PS. Возвращаясь к другим архитектурам синтеза. http://www.markimicrowave.com/blog/2015/02...hase-detectors/ напомните, мы тут рассматривали применение квадратурного смесителя в качестве ФД синтезатора?

|

|

|

|

|

|

|

|

Jan 16 2017, 09:26 Jan 16 2017, 09:26

|

Знающий

Группа: Участник

Сообщений: 620

Регистрация: 4-12-09

Из: Kiev

Пользователь №: 54 052

|

Цитата(khach @ Jan 16 2017, 01:41)  В этой блок-схеме синтезатора есть системная ошибка- ЦАП считается идеальным, как только нужный код появится на входах, так он и выдаст нужное напряжение. Про гонки между разрядами ЦАП наверно слышали? И про аналоговые глитчи из за гонок на выходе ЦАП тоже. Это и было причиной ухода от асинхронных архитекур ЦАП к синхронным. И даже внутри ИС ЦАП построенный по современным архитектурам будет синхронный. Поэтому на него все равно придется подвести тактовую частоту. Вот какую ее выбрать-вопрос. Предполагалось попробовать использовать опорную частоту и частоту VCO, предварительно поделив ее чтобы попасть в диапазон рабочих частот ЦАП. Т.е каждая половинка синтезатора работает со своей частотой, часто со стороны VCO- с переменной. А суммирование сигналов происходит не в цифре, как в вышеприведенной блок-схеме, а аналогово, после ЦАП. Был еще вариант- использовать готовые модули ФЧД в качестве ЦАП с весовыми коэффициентами для токов соотвественно разряду ЦАП. Тут получалась действительно асинхронная архитектура, но только на рассыпухе. PS. Возвращаясь к другим архитектурам синтеза. http://www.markimicrowave.com/blog/2015/02...hase-detectors/ напомните, мы тут рассматривали применение квадратурного смесителя в качестве ФД синтезатора?

|

|

|

|

|

|

|

|

1124 чел. читают эту тему (гостей: 1124, скрытых пользователей: 0)

Пользователей: 0

|

|

|