Добрый день.

Пытаемся реализовать преобразователь HD-SDI видео в формат MIPI CSI-2. Схема проста: SDI проходит эквалайзер, реклокер и десериализотор, затем в виде 20-разрядного параллельного потока поступает в ПЛИС (EP3C16Q240C8), которая должна его должным образом обработать и в виде CSI-2 выдать наружу, чтобы затем подцепить Raspberry.

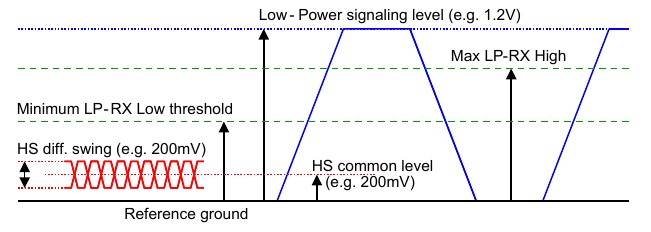

Интерфейс CSI-2 оказался весьма непростым, его физический уровень представляет собой сочетание дифференциального тактового сигнала и от 1 до N двухуровневых дифференциальных пар, работающих в низкоскоростном служебном (LP, low power) и высокоскоростном (HS, high speed, для передачи данных) режимах:

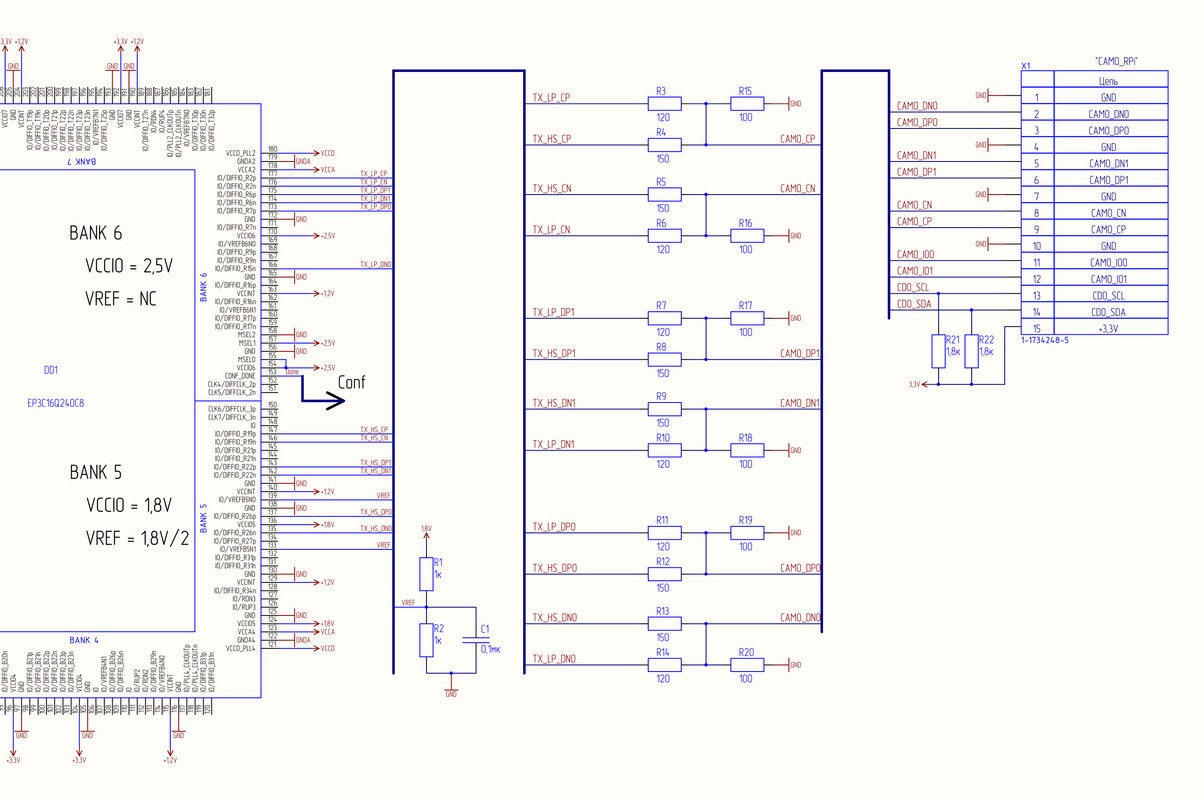

Как реализовать такой режим подсмотрели в отладочной плате 10m50 eval board от той же Altera. С единственным отличием - там используется другое семейство ПЛИС, MAX10 (10M50DAF484C6GES). Нами были выбраны соответствующие диф пары и режимы работы выходных ног ПЛИС:

CODE

set_location_assignment PIN_146 -to TX_HS_CN

set_location_assignment PIN_147 -to TX_HS_CP

set_location_assignment PIN_135 -to TX_HS_DN0

set_location_assignment PIN_142 -to TX_HS_DN1

set_location_assignment PIN_137 -to TX_HS_DP0

set_location_assignment PIN_143 -to TX_HS_DP1

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_CN

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_CP

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DN0

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DN1

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DP0

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DP1

Таким образом на физическом уровне мы выдержали все рекомендации, которые удалось найти.

Далее создали простой тестовый проект в Quartus9.1 для передатчика данных по SCI-2. На данном этапе нам необходимо убедиться, что выбранные нами порты ПЛИС поддерживают требуемые стандарты, и что фиттер всё сможет развести хотя бы в таком примитивном виде. Не хотелось бы попадать в ситуацию, когда печатные платы уже произведены, и только потом обнаружить, что развели их неправильно.

Quartus выдал следующий варнинг:

Error: Pin "TX_HS_CP" requires a pseudo-differential I/O assignment.

Error: Can't fit design in deviceВ Assignment Editor не удалось найти подходящий настроек, чтобы убрать данную ошибку. Да и не понятно откуда ей взяться, ведь всё повторили по примеру вышеуказанной эволюшен боард.

Кто-нибудь сталкивался с подобным? Что можете посоветовать попробовать?