Мне стыдно признаться, но даже сейчас я не совсем Вас понимаю

. Возможно связано с тем, что я сам себя своими рассуждениями загнал в тупик и не вижу способа из него выбраться.

Попробую обьяснить свою логику, может так получится понять друг друга и если я ошибаюсь мне укажут на ошибку в моих рассуждениях.

Итак, за основу своих рассуждений я беру следующую аксиому: для того чтобы вывести на матрицу правильно изображение я должен выполнить требования стандарта VESA, а именно:

Код

pixel_clk 25.175 MHz

Visible area 640 pixel

Front porch 16 pixel

Sync pulse 96 pixel

Back porch 48 pixel

Visible area 480 lines

Front porch 10 lines

Sync pulse 2 lines

Back porch 33 lines

И сли отклонение частоты

pixel_clk ±100...500 КГц еще допускается, то изменение длительности

Front porch,

Back porch приводит к тому, что видимая область изображения будет отображаться за пределами экрана, т.е часть выводимого изображеня будет обрезана. Неточность же

Sync pulse приводит к тому, что матрица вообще может отказываться понимать входной видеосигнал.

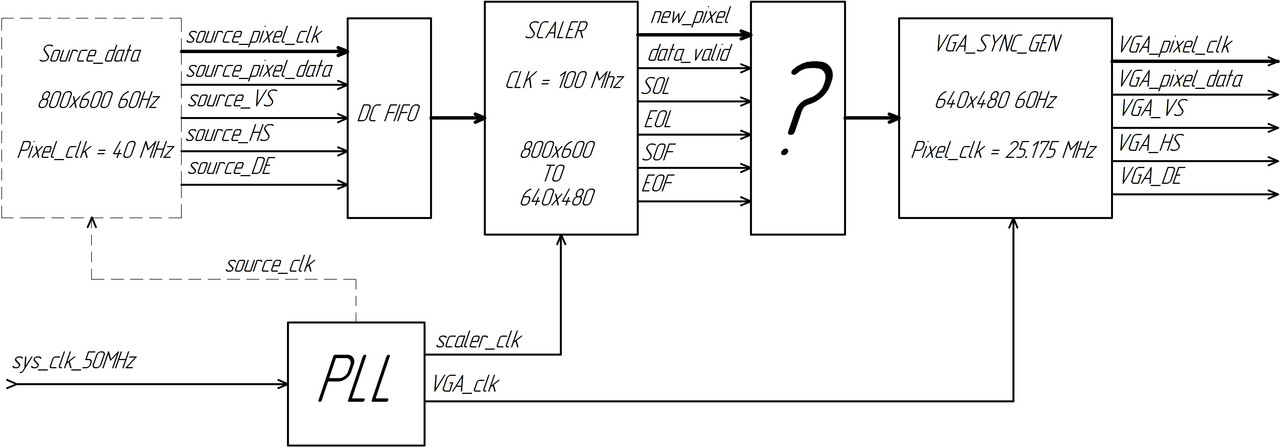

Итого мы имеем 3 клоковых домена:

Домен

Vga_sync_gen - синхрогенератор, который генерирует сигналы H_sync, V_sync, Data_enable для разрешения 640х480х60Hz

Домен

source_data - источник виедосигнала, данные которого я масштабирую. Он имеет свои синхросигналы H_sync, V_sync, Data_enable, имеет свой pixel_clk 40MHz.

Домен

scaler - собственно сам scaler который работает на частоте выше доменов Vga_out и source_data. Это сделано специально для того, чтобы scaler успевал обрабатывать данные независимо от входной или выходной частоты.

Данные из домена source_data посредством FIFO переносятся в домен scaler, обрабатываются там по алгоритму билинейной интерполяции и scaler выдает сигналы:

Данные нового отмасштабированного пикселя

new_pixel.

Сигнал

Data_valid - показывающий что данные нового пикселя можно использовать.

Сигнал

SOL (start of line ) - сообщающий что это у нас первый пиксель в линии.

Сигнал

EOL (end of line ) - сообщающий что это у нас последний пиксель в линии.

Сигнал

SOF (start of frame) - сообщающий что это у нас первый пиксель кадра.

Сигнал

EOF (end of frame) - сообщающий что это у нас последний пиксель в кадре.

Вы говорите, что:

Цитата

Частота кадров одинаковая.

Но ведь кадровые синхроимпульсы формируются на разных частотах, и частота кадров реально будет разная.

Например прии разрешении 640x480 частота кадров 16.683217477656 ms.

А вот на разрешении 800х600 частота кадров уже 16.5792 ms.

С этими я полностью согласен, да это и так вроде очевидно

:

Цитата

2. За один кадр приходит 600 строк выходит 480 строк.

3. На каждые пришедшие 5 строк выдаётся синхронно 4 строки.

4. в каждой принятой строке 800 пиксель клоков внутри строчной - в каждой отданной - 640.

Цитата

Теоретически количество пиксельклоков вне строчного импульса, а также пиксельклоков и строчных импульсов вне кадровой - может быть любым и даже не постоянным.

А вот это утверждение уже интересно, и непонятно одновременно. У нас же после строчного импульса - каждый клок начинает отсчитывать рамку Front porch. Соответственно через определенное количество импульсов у нас должны быть поданы данные. Иначе картинка будет смещена относительно краев видимой области.

Для примеря я покажу структуру проекта.

Источник разрешения 800x600 сейчас находится внутри FPGA, но в последствии это будет отдельное внешнее устройство. Сейчас для отладки так удобнее. Поэтому на блок-схеме он изображен пунктиром