| |

|

|

Расчет необходимого тока выходного пина Расчет необходимого тока выходного пина, Как рассчитать максимальный ток ножки ПЛИС |

|

|

|

|

Aug 28 2018, 16:10 Aug 28 2018, 16:10

|

Группа: Участник

Сообщений: 11

Регистрация: 17-03-15

Пользователь №: 85 739

|

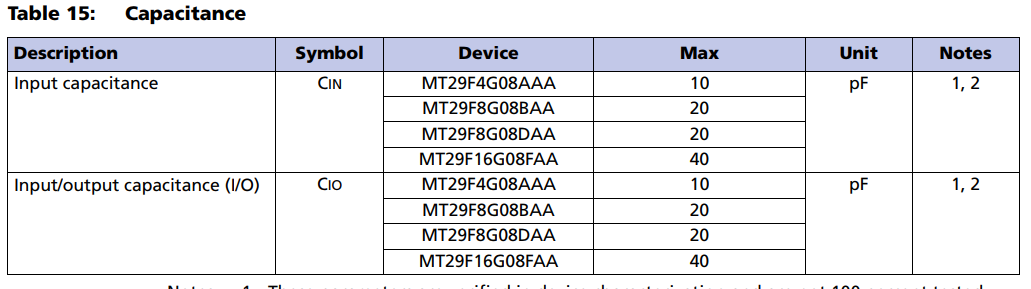

Добрый вечер! 1) Как рассчитать какой максимальный ток нужен ножки ПЛИС, чтобы фронты были нормальные и без помех? 2) Как рассчитывать если ни одна микросхема висит, а несколько? 3) Как рассчитывать если есть подтягивающий резистр на питание или на землю? Правильно ли я понимаю что от микросхемы нам нужно емкость входных ножек, для примера возьмем из datasheeta флешки?

|

|

|

|

|

|

|

|

Aug 28 2018, 16:25 Aug 28 2018, 16:25

|

Группа: Участник

Сообщений: 11

Регистрация: 17-03-15

Пользователь №: 85 739

|

Цитата(Boris_TS @ Aug 28 2018, 17:16)  Я бы посоветовал воспользоваться чем-нибудь типа HyperLynx (PCB Analysis and verification tool от Mentor Graphics).

Для начала IBIS моделей (передатчика и приёмника) вполне должно хватить. Спасибо. Знаком с данной программой, но к сожалению нету средств для использования её в каждой непонятной ситуацией. Думал может есть какие нибудь расчеты для быстрого получения результатов.

Сообщение отредактировал mrjoun - Aug 28 2018, 16:28

|

|

|

|

|

|

|

|

Aug 28 2018, 20:56 Aug 28 2018, 20:56

|

Знающий

Группа: Свой

Сообщений: 779

Регистрация: 3-01-05

Из: Минск

Пользователь №: 1 783

|

Цитата(mrjoun @ Aug 28 2018, 19:25)  Спасибо. Знаком с данной программой, но к сожалению нету средств для использования её в каждой непонятной ситуацией.

Думал может есть какие нибудь расчеты для быстрого получения результатов. Максимальный ток ножки задаётся в проекте плис. Ёмкость известна. Время её заряда считается t=CU/I. Чем не примерный расчёт. Плюс можно добавить ёмкость монтажа. Ёмкость самого пина ПЛИС. Цитата(mrjoun @ Aug 28 2018, 19:10)  Добрый вечер!

1) Как рассчитать какой максимальный ток нужен ножки ПЛИС, чтобы фронты были нормальные и без помех? Про нормальные написал выше. Про помехи не очень понятно как ток ножек связан с помехами.... Цитата 2) Как рассчитывать если ни одна микросхема висит, а несколько? Сложить ёмкости. Цитата 3) Как рассчитывать если есть подтягивающий резистр на питание или на землю? Смотря чем управялем. Если открытым коллектором то обычная RC цепь. Если активным выводом то по сути подтяжка ни на что не влияет при разумных величинах подтяжки. Цитата Правильно ли я понимаю что от микросхемы нам нужно емкость входных ножек, для примера возьмем из datasheeta флешки? Если не секрет что за задача стоит? Что такое разрабатывается что встаёт вопрос не согласования линий и пр... а нагрузочная способность выходов? За последние лет 20 я не помню чтобы приходилось считать нагрузочную способность выходов плис. Ещё у жёсткой логики помню были такие развлечения. А сейчас это накой? Есть желание подцепить к ПЛИС десяток другой флешей в параллель?

|

|

|

|

|

|

|

|

Aug 29 2018, 06:23 Aug 29 2018, 06:23

|

Участник

Группа: Участник

Сообщений: 18

Регистрация: 10-08-18

Пользователь №: 106 692

|

Фронты нормальные и без помех - это имеется в виду без колебаний, способных вызвать ложные переключения?

Думается, в данном случае использование согласованных линий не подходит. Делать связи покороче, нормальную возвратную землю, подавить колебания могут помочь последовательные резисторы на несколько десятков Ом.

|

|

|

|

|

|

|

|

Aug 29 2018, 09:06 Aug 29 2018, 09:06

|

Гуру

Группа: Модераторы

Сообщений: 4 011

Регистрация: 8-09-05

Из: спб

Пользователь №: 8 369

|

Цитата(MegaVolt @ Aug 28 2018, 23:56)  Максимальный ток ножки задаётся в проекте плис. Ёмкость известна. Время её заряда считается t=CU/I.

Чем не примерный расчёт. Плюс можно добавить ёмкость монтажа. Ёмкость самого пина ПЛИС. Я только немного добавлю. В ПЛИС можно задать "скорость наростания" и "силу тока" для конкретного вывода. Но при этом есть ограничение на число одновременно переключаемых выходов в зависимости от выбранного тока. При 24 мА число выводов невелико, при 2 мА на порядок больше. Как выбрать "силу тока"? Естественно, чем меньше ток, тем дольше заряжается емкость нагрузки. Но!!! Все дело в самой нагрузке. Если у нее тактовая 1 Мгц, то для нее фронты в 0,1 от длительности клока вполе возможно будут приемлемы. А вот если внутренняя тактовая 100 Мгц, как у ПЛИС, то для такой нагрузки медленный фронт импульса - будет восприниматься как пологая пила... Потому как на фронт еще наложатся колебания от отражений, наводок, помех и т.д. В любом случае, Вы можете в реальном железе оценить фронты и потом изменить настройки проекта, либо чтобы улучшить фронты, либо наоборот завалить фронты, но уменьшить потребление и помехи от переключения.

--------------------

www.iosifk.narod.ru

|

|

|

|

|

|

|

|

Aug 29 2018, 16:06 Aug 29 2018, 16:06

|

Группа: Участник

Сообщений: 11

Регистрация: 17-03-15

Пользователь №: 85 739

|

Цитата(twix @ Aug 29 2018, 09:44)  Разводите плату, суете осциллограф и выбираете ток и резисторы по ходу тестов. Спасибо, плата уже готова, все корпуса BGA, резисторов нет. Не подлезть.

|

|

|

|

|

|

|

|

Aug 29 2018, 18:39 Aug 29 2018, 18:39

|

Знающий

Группа: Свой

Сообщений: 779

Регистрация: 3-01-05

Из: Минск

Пользователь №: 1 783

|

Цитата(iosifk @ Aug 29 2018, 12:06)  Но при этом есть ограничение на число одновременно переключаемых выходов в зависимости от выбранного тока. Есть. Только я в реальной жизни ни разу на это ограничение не наступал. При этом в большинстве случаев кристаллы по IO заняты на 100% Ведь ограничение как я понимаю срабатывает когда все линии нагружены именно на этот ток а постоянку. А это в КМОП схемах скорее редкость. Соответственно максимум на что можно наткнуться это на затягивание фронтов.

|

|

|

|

|

|

|

|

Aug 29 2018, 18:49 Aug 29 2018, 18:49

|

Местный

Группа: Свой

Сообщений: 449

Регистрация: 28-10-04

Из: Украина

Пользователь №: 1 002

|

Цитата(MegaVolt @ Aug 29 2018, 20:39)  Есть. Только я в реальной жизни ни разу на это ограничение не наступал. При этом в большинстве случаев кристаллы по IO заняты на 100%

Ведь ограничение как я понимаю срабатывает когда все линии нагружены именно на этот ток а постоянку. А это в КМОП схемах скорее редкость. Соответственно максимум на что можно наткнуться это на затягивание фронтов. Вы ошибаетесь. Ваше счастье, что не попадались проекты, где количество SSO превышает лимиты. Начинается жесть с питанием и рандомными сбоями. И самое главное, причина совсем не очевидна. Удачи.

--------------------

Умею молчать на 37 языках...

|

|

|

|

|

|

|

|

Aug 30 2018, 07:10 Aug 30 2018, 07:10

|

Участник

Группа: Участник

Сообщений: 29

Регистрация: 28-06-11

Пользователь №: 65 930

|

Цитата(MegaVolt @ Aug 29 2018, 21:39)  ...

Ведь ограничение как я понимаю срабатывает когда все линии нагружены именно на этот ток а постоянку. А это в КМОП схемах скорее редкость. ... Самое критичное место в цифровых схемах - это момент смены состояния выхода. Обусловлено тем, что за малое время переключения выхода (до наносекнд и менее) необходимо перезарядить линию и входные ёмкость подключенных к ней элементов (в сумме до сотен пикофарад и более). Таким образом из школьной формулы можно оценить, что при фронте в 1 В/нс для перезарядки ёмкости в 100 пф требуется ( [Ф] = [Кл]·[1/В] = [А]·[с]·[1/В] -> [Ф]·[В] = [А]·[с] -> [А] = [Ф]·[В]/[с] ) 0,1А импульсного тока. И всё бы ничего, но десяток таких ног создаёт на оммическом и индуктивном сопротивлении выводов питания м/с напряжения, достаточные для сбоя цифровой схемы. Оттого и ограничения...

|

|

|

|

|

|

|

|

Aug 30 2018, 07:41 Aug 30 2018, 07:41

|

Знающий

Группа: Свой

Сообщений: 779

Регистрация: 3-01-05

Из: Минск

Пользователь №: 1 783

|

Цитата(Gorby @ Aug 29 2018, 21:49)  Вы ошибаетесь. Ваше счастье, что не попадались проекты, где количество SSO превышает лимиты.

Начинается жесть с питанием и рандомными сбоями. И самое главное, причина совсем не очевидна. Я про это же и говорю что мне сложно представить проект где нужно шевелить большущим количеством полновольтовых выходов на огромной частоте и с большими ёмкостями. Т.е. там где нужны большие скорости там LVDS где скорости не нужны можно ставить полновольтовые выходы но раз скорость не важна то можно ограничить ток. Если не секрет а что за проект был?

|

|

|

|

|

|

|

|

Aug 30 2018, 09:18 Aug 30 2018, 09:18

|

Участник

Группа: Участник

Сообщений: 29

Регистрация: 28-06-11

Пользователь №: 65 930

|

Цитата(MegaVolt @ Aug 30 2018, 10:41)  Я про это же и говорю что мне сложно представить ... Кажется, может быть достаточно широкошинного ОЗУ, например использования ПЛИС в качестве некоего моста или коммутатора потоков данных.

|

|

|

|

|

|

|

|

Aug 31 2018, 08:49 Aug 31 2018, 08:49

|

Злополезный

Группа: Свой

Сообщений: 608

Регистрация: 19-06-06

Из: Russia Taganrog

Пользователь №: 18 188

|

Цитата(MegaVolt @ Aug 30 2018, 10:41)  Т.е. там где нужны большие скорости там LVDS где скорости не нужны можно ставить полновольтовые выходы но раз скорость не важна то можно ограничить ток.

Если не секрет а что за проект был? Дело в том, что там, где нужны действительно большие скорости и огромная пропускная способность, часто применяется не LVDS, а SSTL/HSTL: в таком случае количество I/O на один IO-Bank возрастает практически в 2 раза (по сравнению с LVDS) - и в этом случае очень легко поиметь проблемы с SSO. Сейчас, конечно, в современных ПЛИС хорошо развились SerDes'ы (MGT) - и частенько для высокоскоростных обменов они подходят лучше, а вот лет 5-7 назад с MGT была тоска полная. Да и в современных DDR’ах пока ещё используют SSTL, а не MGT (Про Hybrid Memory Cube знаю... даже как-то обсуждал с представителями Micron его сильные и слабые стороны по сравнению с DDR, естественно, применительно к ПЛИС).

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|