| |

|

|

В протеле замечена проблема, суппорт бессилен В протеле замечена проблема, суппорт бессилен, Примите к сведению и по возможности посоветуйте решение |

|

|

|

|

Nov 9 2005, 09:38 Nov 9 2005, 09:38

|

Гуру

Группа: Свой

Сообщений: 2 752

Регистрация: 10-11-04

Из: Железнодорожный

Пользователь №: 1 093

|

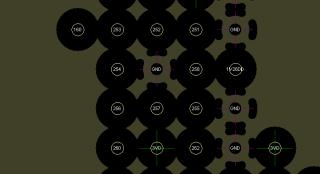

Клиент обнаружил, что если цепь, например GND назначена на план, то DRC не вылавливает отсутствие соединения отдельных пинов с остальной поверхностью слоя. Случается это. когда пользователь неправильно задает слишком большим изолирующий ободок на плане для не присоединенного пина. В результате области изоляции перекрываются и в корпусах типа BGA получаются пины, лишь теоретически соединенные с планом. Рисунок приаттачить не могу из-за глюков форума, потом добавлю. В службу техподдержки была отправлена соответствующая предъява, но суппорт констатировал отсутствие возможности с помощью DRC выловить подобную ошибку и рекомендовал тщательнее проверять правила зазоров на планах. Собственно, я не удивлюсь, если кто-то из юзеров придумал способ проверки, о котором не додумался суппорт. Прошу поделиться информацией. Остальным прошу принять к сведению и быть внимательнее.

Эскизы прикрепленных изображений

Р В Р’ВВВВВВВВзображенРСвЂВВВВВВВР В Р’Вµ СѓРСВВВВВВВВеньшено

(8.48 килобайт)

|

|

|

|

|

|

|

|

|

Nov 11 2005, 10:52 Nov 11 2005, 10:52

|

Местный

Группа: Свой

Сообщений: 307

Регистрация: 4-10-05

Из: Москва

Пользователь №: 9 217

|

Цитата(Yuri Potapoff @ Nov 9 2005, 14:37)  С помощью камовских средств я вижу два способа.

1. Генерация нетлиста после импорта протеловского pcb файла. Камтастик тут не поможет, так как сам протел IPC нетлист из pcb делать не умеет. Генерация нетлиста из импортированных герберов той же платы. И сравнение в конце концов нетлистов.

2. Анализ гербера с плана на предмет изолированных островков. Если они есть, то это или сплит план, или описанная бяка. А не поможет загрузка в CAM350 ODB++ файлов из Протеля (для версии 9 мне это удавалось, хотя подробно не щупал пока), ведь там должен быть Нетлист?

|

|

|

|

|

|

|

|

Nov 14 2005, 04:15 Nov 14 2005, 04:15

|

Участник

Группа: Свой

Сообщений: 56

Регистрация: 23-06-04

Пользователь №: 128

|

Ещё это можно проверить с помощью Valor Enterprise. Затягиваете в него PCB целиком, генерите Current Netlist и сравниваете его с CAD Netlist. Все дела.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|