| |

DDR3-Spartan6 DDR3-Spartan6, импеданс 43 Ом |

|

|

|

|

Sep 6 2011, 07:39 Sep 6 2011, 07:39

|

Знающий

Группа: Свой

Сообщений: 756

Регистрация: 14-08-07

Из: Москва

Пользователь №: 29 765

|

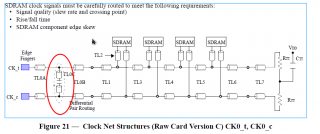

UreeПрошу прощения за кросспост, по вашей ссылке не ходил, поэтому не видел что она ведет на jedec.  Просматривая дизайн DDR3 модулей обратил внимание что дифф. пара частоты синхронизации шунтируется конденсатором несколько пФ. Так ли необходим этот конденсатор или можно обойтись без него? Тем более у меня топология простая: один контроллер - один чип памяти. Понятно что нужно это смоделировать, но до этого дойду только через несколько недель, когда плата будет в более-менее готовом виде...

РЈРСВеньшено Р В РўвЂР  С• 83%

976 x 407 (53.39 килобайт)

|

|

|

|

|

|

|

|

|

Sep 6 2011, 12:43 Sep 6 2011, 12:43

|

Знающий

Группа: Свой

Сообщений: 551

Регистрация: 3-09-10

Из: Беларусь, Минск

Пользователь №: 59 267

|

Цитата Понятно что нужно это смоделировать, но до этого дойду только через несколько недель, когда плата будет в более-менее готовом виде... А в HyperLynx LineSim если попробовать смоделировать подобную линию передачи? Это можно сделать и на этапе пред-топологического анализа по идее.

|

|

|

|

|

|

|

|

Nov 29 2011, 19:34 Nov 29 2011, 19:34

|

Знающий

Группа: Свой

Сообщений: 672

Регистрация: 18-02-05

Пользователь №: 2 741

|

Цитата(Ant_m @ Nov 29 2011, 21:01)  Да, нужны. В руководстве на S-6 сказано 4.7 к на землю. Там что, не параллельная терминация? И ещё, сколько рекомендуемый уровень кросстоков если замерять в HL?

|

|

|

|

|

|

|

|

Nov 30 2011, 05:35 Nov 30 2011, 05:35

|

Знающий

Группа: Свой

Сообщений: 756

Регистрация: 14-08-07

Из: Москва

Пользователь №: 29 765

|

Мы оба частично не правы  Извиняюсь вчера ответил почти не подумав. ODT - терминация нужна. CKE - резистор 4,7к в землю. Цитата For DDR3 memory devices, the RESET and CKE signals should each have a 4.7 kΩ

resistor to ground to ensure that these signals are Low during memory initialization.

• For DDR2 memory devices, the ODT and CKE signals should each have a 4.7 kΩ

resistor to ground to ensure that these signals are Low during memory initialization. Вот еще, рекомендации на DDR3 интрефейс V6: Цитата The RESET and CKE signals are not terminated. These signals should be pulled down

during memory initialization with a 4.7 kΩ resistor connected to GND.

|

|

|

|

|

|

|

|

Nov 30 2011, 08:03 Nov 30 2011, 08:03

|

Знающий

Группа: Свой

Сообщений: 672

Регистрация: 18-02-05

Пользователь №: 2 741

|

Цитата(Ant_m @ Nov 30 2011, 08:35)  Мы оба частично не правы  Извиняюсь вчера ответил почти не подумав. ODT - терминация нужна. CKE - резистор 4,7к в землю. Вот еще, рекомендации на DDR3 интрефейс V6: Спасибо!

|

|

|

|

|

|

|

|

Dec 2 2011, 06:31 Dec 2 2011, 06:31

|

Знающий

Группа: Свой

Сообщений: 756

Регистрация: 14-08-07

Из: Москва

Пользователь №: 29 765

|

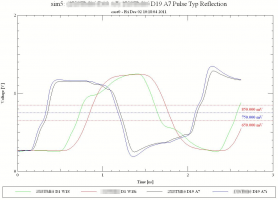

Проверяйте модели. Проблема либо в неправильном ODT, либо неправильный буфер в модели ПЛИС. Про модели Спартана сказать не могу, но например для Виртекса, модели SSTL15_DCI есть только вход и только выход. Двунаправленной модели нет. Поэтому приходится руками указывать нужную модель.

РЈРСВеньшено Р В РўвЂР  С• 86%

1205 x 869 (289.62 килобайт)

|

З.Ы. Моделировано не в гиперлинксе. Индекс i - сигнал внутри корпуса(или на кристалле).

|

|

|

|

|

|

|

|

Dec 8 2011, 06:00 Dec 8 2011, 06:00

|

Знающий

Группа: Свой

Сообщений: 756

Регистрация: 14-08-07

Из: Москва

Пользователь №: 29 765

|

Цитата(Alexer @ Dec 7 2011, 19:38)  Для DDR3 вроде как на младший разряд повесили дополнительную функцию - участие в процедуре write-leveling: ...............

........... Получается что младший разряд свапировать на другие разряды нельзя? Можно ли свапировать другие разряды внутри байта между собой? Вообще, вопрос конечно интересный  Ответ такой - в общем виде у DQ0 и DQ7 DQ8 менять расположение нельзя. А если погрузиться в частности, то Spartan6 не поддерживает write-leveling  Write-leveling требуется только тогда когда на шине адреса висит много микросхем памяти. Т. е к одному контроллеру подключено от 2-х микросхем. А это, для Spartan6 не возможно - у него даже нет сигнала CS# для памяти... Так-что можете смело менять данные как вам угодно.

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|