| |

DDR3: Терминация сигналов CK DDR3: Терминация сигналов CK, Выбор топологии |

|

|

|

|

May 25 2018, 21:13 May 25 2018, 21:13

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Здравствуйте. Нужен совет практиков. Проектируется узел с DDR3 MT41J128M16JT-125IT. Моделирование ЦС выполняется в Hyper Lynx. Для сигнала CK имеем ошибку по точке пересечения комплементарных сигналов:

Стандартом JEDEC предписано следующее:

Действительно, если посмотреть на осциллограммы сигналов CK_P и CK_N (пробник на кристалле памяти), видна асимметрия (227 мВ):

Причём это связано с разными временами нарастания и спада: Avg fall time: 119.773 ps Min fall time: 118.092 ps High voltage: 1.19 V Max fall time: 130.519 ps Low voltage: 385.9 mV Avg rise time: 93.433 ps Min rise time: 89.377 ps Low voltage: 385.9 mV Max rise time: 95.155 ps High voltage: 1.19 V Сигнал спадает медленнее, чем нарастает. Если посмотреть на сигнал DQS (режим записи в память, пробник на кристалле памяти), то там асимметрия меньше (112 мВ):

Хотя скорость нарастания и спада по-прежнему разная: Avg fall time: 142.460 ps Min fall time: 141.122 ps High voltage: 1.20 V Max fall time: 143.345 ps Low voltage: 326.8 mV Avg rise time: 125.503 ps Min rise time: 121.370 ps Low voltage: 326.8 mV Max rise time: 126.889 ps High voltage: 1.20 V. Я подозреваю, что разница в том, что сигнал CK терминируется, как простой LVDS - на резистор 100 Ом (так рекомендует Micron в TN-46-14: "VTT does not terminate any DDR clock pairs. CK and CK# termination is a parallel 100...121 Ohm resistor between the two lines. Micron has found that only differential termination on CK and CK# produces optimal SI."), а DQS - уже на Vdd/2 внутри чипа памяти.

Возможно, нужно поставить под сомнение рекомендацию производителя. Вопрос: сталкивался ли кто-нибудь с необходимостью терминации сигналов тактирования CK на Vdd/2 вместо того, что рекомендует Micron? Или устранение данной проблемы нужно вести другим способом? В похожей теме ответа не нашёл. Спасибо.

|

|

|

|

|

|

|

|

Ответов

(1 - 89)

|

|

May 29 2018, 13:54 May 29 2018, 13:54

|

Участник

Группа: Участник

Сообщений: 55

Регистрация: 7-02-09

Из: Ростов-на-Дону

Пользователь №: 44 537

|

Если не секрет, в чем разница?

|

|

|

|

|

|

|

|

May 29 2018, 22:15 May 29 2018, 22:15

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Благодарю всех за ответы. Провёл сравнение исходного (терминация на 100 Ом) и правильного (2 резистора по 50 Ом, из центра ёмкость 100 нФ на 1,5 В) вариантов. Сначала промоделировал оба варианта в LineSim (предтопологический анализ у Mentor). Исходный вариант:

Avg fall time: 127.011 ps Min fall time: 127.011 ps High voltage: 1.16 V Max fall time: 127.011 ps Low voltage: 341.7 mV Avg rise time: 74.722 ps Min rise time: 74.722 ps Low voltage: 391.2 mV Max rise time: 74.722 ps High voltage: 1.19 V Правильный вариант:

Видно, что асимметрия сократилась (стало 263 мВ вместо 347 мВ). Avg fall time: 118.569 ps Min fall time: 118.569 ps High voltage: 1.14 V Max fall time: 118.569 ps Low voltage: 259.9 mV Avg rise time: 96.200 ps Min rise time: 96.200 ps Low voltage: 409.0 mV Max rise time: 96.200 ps High voltage: 1.26 V Видно также, что сократилась разница во временах нарастания и спада (стало 22 пс вместо 53 пс). Далее внёс изменения в схему, скорректировал трассировку и выполнил посттопологический анализ.

CK_P: Avg fall time: 109.226 ps Min fall time: 107.515 ps High voltage: 1.21 V Max fall time: 110.143 ps Low voltage: 399.7 mV Avg rise time: 102.426 ps Min rise time: 98.577 ps Low voltage: 399.7 mV Max rise time: 103.840 ps High voltage: 1.21 V CK_N: Avg fall time: 119.107 ps Min fall time: 117.673 ps High voltage: 1.14 V Max fall time: 130.393 ps Low voltage: 304.8 mV Avg rise time: 107.905 ps Min rise time: 101.301 ps Low voltage: 304.8 mV Max rise time: 108.514 ps High voltage: 1.14 V Однако в отчёте по-прежнему фигурирует несоответствие стандарту в параметре Vix (только для режима работы Fast; для Typical и Slow ошибок нет):

Ошибка сократилась примерно в два-три раза. Вывод: в данном случае терминация сигнала СК с помощью двух резисторов и конденсатора позволяет добиться лучшей целостности сигнала по сравнению с терминацией на один 100 Ом резистор, однако не позволяет исправить асимметрию сигнала до приемлемого уровня для режима Fast.

|

|

|

|

|

|

|

|

May 30 2018, 13:58 May 30 2018, 13:58

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Что вы имеете в виду под сетапом? Откуда у вас к примеру в дизайне с одной планкой памяти столько TL, причем в разном числе и с разными propagation delay- притом на одном слое? Это маразм  Далее: Цитата Данная асимметрия подпадает под второй случай Да что-то не похоже  - я бы начал с самого первого случая, но вообще тут помимо всего сказанного очень интересна природа overshoot/pre-shoot с ваших графиков, те два зубца в начале и конце полупериода. Ну и разводка конечно у вас мусор, особенно подвод к шарам  - а есть ли изображение всей цепи клока(и заодно строба около артикса), включая терминацию? Тот же вопрос про изображение опорного слоя, вместе с антипадами. ПС. Термалы на виа это конечно победа, бесспорно. По TL в 55 и 70Ом соображения примерно схожие

|

|

|

|

|

|

|

|

May 30 2018, 14:46 May 30 2018, 14:46

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

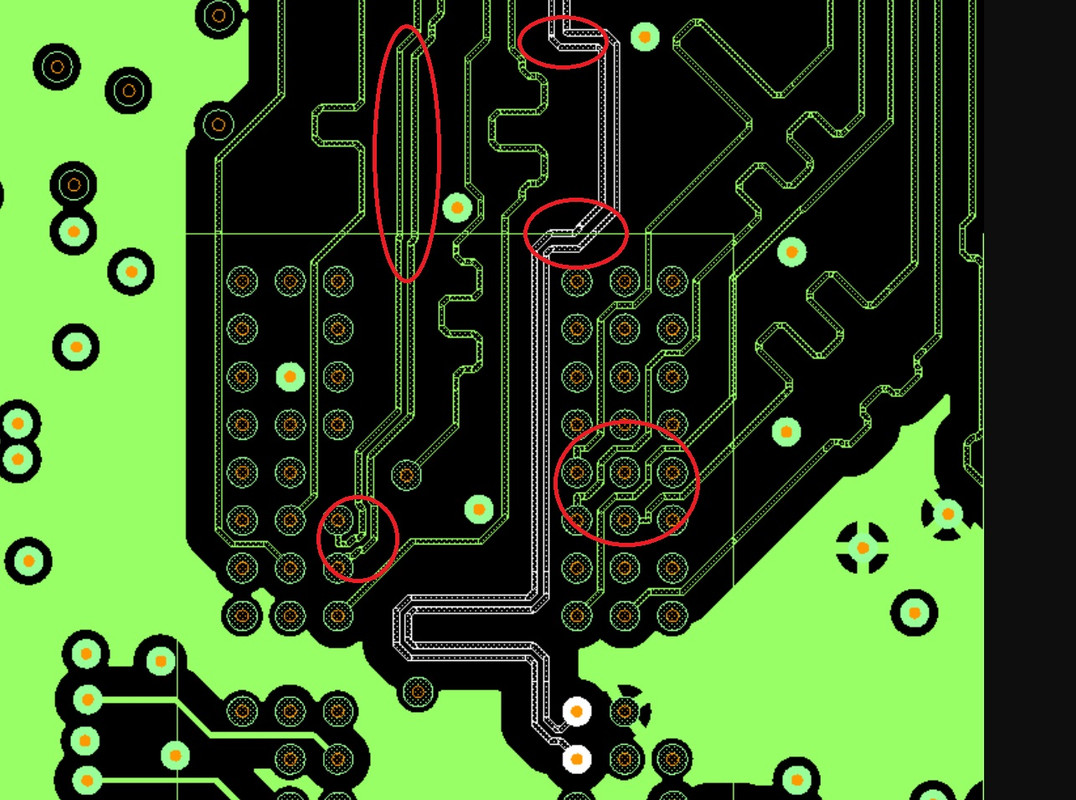

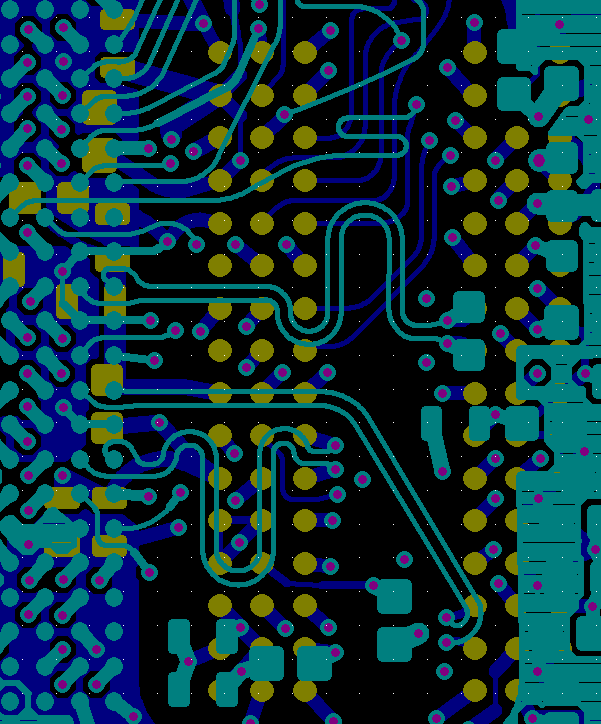

EvilWrecker, 1. Множество TL - это сегменты меандра. 2. Такт во всех слоях:

3. Что за термалы на переходных отверстия и почему это приводит к "победе"?

|

|

|

|

|

|

|

|

May 30 2018, 14:56 May 30 2018, 14:56

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата 1. Множество TL - это сегменты меандра. Да это и так ясно- но это глупость, т.к. у вас uniform transmission line(одно "целое") от виа до виа  Не считая моментов ниже  Цитата 2. Такт во всех слоях: Ужас. Но хотелось бы другого изображения- по типу с белой маской и всю цепь как в вашем предыдущем посте. Ну и уже чисто любопытство- а всю плату можете показать, хотя бы компоненты топ/бот? Сугубо личный интерес, узнать на что ушло в артиксе-7 16 слоев. Цитата 3. Что за термалы на переходных отверстия и почему это приводит к "победе"? Ну как что- термобарьеры. Их быть не должно вообще нигде ни на каких виа  Крутить выходы трасс в антипадах тоже совершенно не нужно. Вы всерьез спрашиваете почему или это шутка?

|

|

|

|

|

|

|

|

May 30 2018, 15:22 May 30 2018, 15:22

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

EvilWrecker, 1. Это замечание нужно адресовать в Mentor, а не мне. Я не управляю алгоритмами выгрузки в LineSim. 2. Не понял, какое ещё изображение нужно привести. Я показал все слои, где содержится такт. Верх/низ платы, если это поможет делу:

3. Термобарьеры на переходных отверстиях для улучшения паяемости (чтобы тепло не уходило в полигон). Что значит крутить трассы?

|

|

|

|

|

|

|

|

May 30 2018, 15:30 May 30 2018, 15:30

|

Местный

Группа: Свой

Сообщений: 290

Регистрация: 29-09-06

Из: Москва

Пользователь №: 20 800

|

Цитата(Stepanich @ May 30 2018, 18:22)  3. Термобарьеры на переходных отверстиях для улучшения паяемости (чтобы тепло не уходило в полигон). Что значит крутить трассы? Извините, не смог удержаться.  P.S.: Запасся попкорном.

|

|

|

|

|

|

|

|

May 30 2018, 15:35 May 30 2018, 15:35

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата 1. Это замечание нужно адресовать в Mentor, а не мне. Я не управляю алгоритмами выгрузки в LineSim. Нет, HyperLynx который вы используете это зрелый инструмент, который существует не один год и конкретно эта его часть работает вполне. С вероятностью 99% проблемы от ваших действий  Цитата 2. Не понял, какое ещё изображение нужно привести. Полная цепь клока вместе с опорным полигоном и терминацией- чтобы все вмещалось в одну картинку. То же самое со стробом. Цитата Верх/низ платы, если это поможет делу: В принципе с некоторыми издержками можно допустить 16 слоев, окей  Цитата 3. Термобарьеры на переходных отверстиях для улучшения паяемости (чтобы тепло не уходило в полигон). Никак они не помогут паяемости  А в таком дизайне их не должно быть в принципе, без каких-либо альтернатив и/или оговорок. Цитата Что значит крутить трассы? Это значит что вместо прямого вывода из пада/виа вы наращиваете сегменты прямо в анипаде, как бы "вокруг". Ну и пару слов за overshoot/pre-shoot- они случаются когда Zload>Zsource, что вполне соответствует вашим картинкам- притом есть ощущения, что в реале уход от целевого импеданса заметно больше, особенно после просмотра того же строба.

|

|

|

|

|

|

|

|

May 30 2018, 16:02 May 30 2018, 16:02

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата 1. Окно экcпорта в LineSim: Честно вам говорю- без понятия что вы там накрутили, но для uniform transmission line всегда получается одна TL, потому как это и есть ее представление  Вы определенно что-то делаете криво: гиперлинкса у меня под рукой нет- или смотрите методичку внимательно, или вебинары на сайте ментора самого, или спросите своего FAE. То что у вас изображено в модели линии это извращение. Цитата 2. Вывел вместе все те же слои. Разве стало яснее? Давайте в N-й раз повторю- мне не нужны все слои, вся разводка и пр. Нужна сугубо вся цепь клока и его опорный слой- и все. Чтобы было видно все между артиксом и ддр3. То же самое и со стробом  Цитата 3. Не понимаю негативного отношения к термобарьерам. Тема довольна избита: Мне эти темы читать неинтересно, хотя бы потому что ценного там очень мало- но вы судя по всему если не первый, то второй раз беретесь за такие дизайны, в частности за ддр3. Перед тем как делать подобные ошибки как у вас, стоит хотя бы погуглить- включая термалы, и не в контексте "проблем со сборкой" и прочих фикций, а именно с позиций SI/PI. Там и ясно станет что не так с термалами в хайспидном дизайне

|

|

|

|

|

|

|

|

May 30 2018, 16:24 May 30 2018, 16:24

|

Местный

Группа: Свой

Сообщений: 290

Регистрация: 29-09-06

Из: Москва

Пользователь №: 20 800

|

Цитата(Stepanich @ May 30 2018, 19:19)  2. Некачественная пайка, вызванная отводом тепла в полигон, - частая проблема. Я не могу игнорировать требования монтажного цеха. Если пайка не надёжна, то смысла в хорошем SI/PI Некачественная пайка чего? Компонентов? Тогда зачем вы делаете барьеры на переходных?

|

|

|

|

|

|

|

|

May 30 2018, 16:31 May 30 2018, 16:31

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Некачественная пайка чего? Компонентов? Тогда зачем вы делаете барьеры на переходных? Вопрос в точку- а термалы на виа это идиотизм крайней степени. Небось в дизайне самом еще геометрия термалов одинаковая для всех корпусов. Цитата Я же привёл всю цепь такта (CK) в сообщении 10: Вы наверное меня разыгрываете- в чем проблема сделать маскирование цепи и показать только ее на фоне полигона? Если и так проблема, то покажите хотя бы отдельно терминацию и участки под бга- ну а если и так проблема, то черт с ним, и так понятно все  Цитата Спасибо за замечание, но в данной теме мы обсуждаем цепь такта. Не за что- но это прямо относится к обсуждаемым цепям. Вы просто путаете понятия судя по всему: конечно хочется выдать комментарий про "монтажный цех", но видите, сдерживаюсь как могу

|

|

|

|

|

|

|

|

May 30 2018, 17:58 May 30 2018, 17:58

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(EvilWrecker @ May 30 2018, 19:02)  Честно вам говорю- без понятия что вы там накрутили, но для uniform transmission line всегда получается одна TL, потому как это и есть ее представление  Вы определенно что-то делаете криво: гиперлинкса у меня под рукой нет- или смотрите методичку внимательно, или вебинары на сайте ментора самого, или спросите своего FAE. То что у вас изображено в модели линии это извращение. 1. Включено экспортировать связанные сегменты, поэтому их так много. 2. Проблема не в трассировке. Можно удалить все сегменты и оставить только два, проблема все равно не исчезнет и она никак не зависит ни от длины линий, ни даже от их разницы. Проблема в том, что наклон кривой по переднему фронту и по заднему разный. Соответственно точка их пересечения всегда сдвигается далеко от средней точки (VDD/2). Все это заданно в модели от хилых. На рисунке

можете увидеть разницу в расположении этой точки пересечения фронтов для Typ и Fast. Для значений Typ все еще в допуске, для Fast ушла сильно вверх. Соответственно надо каким-то образом замедлить передний фронт или ускорить задний.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

May 30 2018, 18:12 May 30 2018, 18:12

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата 1. Включено экспортировать связанные сегменты, поэтому их так много. Это которая "export coupled segments"? Цитата 2. Проблема не в трассировке. Можно удалить все сегменты и оставить только два, проблема все равно не исчезнет и она никак не зависит ни от длины линий, ни даже от их разницы. Проблема в том, что наклон кривой по переднему фронту и по заднему разный. Соответственно точка их пересечения всегда сдвигается далеко от средней точки (VDD/2). Я может что-то в ветке пропустил, но у вас совершенно другая модель линии(в частности без виа)- особенно неясно почему нет TL между ддр3 и терминаторами, зато есть в самой терминации. Overshoot/pre-shoot как у ТС у вас нет, параметры TL между контролером и ддр3 разобрать нереально, но похоже что они одинаковые- что моделируется в этом сетапе?  Цитата Соответственно надо каким-то образом замедлить передний фронт или ускорить задний. Как вы себе это представляете? Цитата EvilWrecker, Карлсон, я не сразу понял, что вы говорите о поясках (annual ring) в переходных отверстиях, а не о термобарьерах. В таком случае это изменить нельзя, т. к. плата делается по классу IPC-3: Нет, речь не об annular ring а о способе подключения виа к полигону- у вас оно не прямое, что глубоко ошибочно

|

|

|

|

|

|

|

|

May 30 2018, 19:59 May 30 2018, 19:59

|

Местный

Группа: Свой

Сообщений: 290

Регистрация: 29-09-06

Из: Москва

Пользователь №: 20 800

|

Цитата(Stepanich @ May 30 2018, 21:10)  Карлсон, я не сразу понял, что вы говорите о поясках (annual ring) в переходных отверстиях, а не о термобарьерах. Бггг. Вы издеваетесь что ли? Смотрим внимательно: Annular ring  Thermal relief  И вот еще  Улавливаете разницу в терминологии? Если нет, то почитайте хотя бы вот это.

|

|

|

|

|

|

|

|

May 30 2018, 20:24 May 30 2018, 20:24

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Карлсон, в терминах приложенной вами статьи: Annular ring - гарантийный поясок; Air gap - термический барьер. В сообщениях 9 и 11 EvilWrecker использует термины "Термалы на виа", и "термобарьеры" которые я воспринимаю как Air gap - термический барьер. Не понимаю, о какой разнице в терминологии идёт речь.

Если суть замечаний - в наличии термического барьера, то это изменить нельзя, т. к. есть требования на качество пайки.

Если суть замечаний - в наличии гарантийных поясков в слоях, где нет подключения к полигонам или проводникам, то это изменить нельзя, т. к. это требование стандарта IPC-3 (см. сообщение 21). Кроме того, их наличие не влияет на описанную проблему с цепью CK. Если есть сомнения, то можно выполнить моделирование ЦС этой цепи с переходными отверстиями без гарантийных поясков или вообще слепыми. Затем сравнить две осциллограммы.

|

|

|

|

|

|

|

|

May 30 2018, 20:29 May 30 2018, 20:29

|

Участник

Группа: Участник

Сообщений: 37

Регистрация: 5-09-16

Пользователь №: 93 222

|

Цитата(Stepanich @ May 30 2018, 23:24)  Если суть замечаний - в наличии термического барьера, то это изменить нельзя, т. к. есть требования на качество пайки. А что обычно паяется к переходным отверстиям?

|

|

|

|

|

|

|

|

May 30 2018, 20:53 May 30 2018, 20:53

|

Местный

Группа: Свой

Сообщений: 290

Регистрация: 29-09-06

Из: Москва

Пользователь №: 20 800

|

Цитата(Stepanich @ May 30 2018, 23:39)  к переходным отверстиям подключены проводники от контактов элементов (в нашем случае выводы BGA) Т.е. вы полагаете, что косточек от площадок до переходных недостаточно для правильной пайки?

|

|

|

|

|

|

|

|

May 30 2018, 21:31 May 30 2018, 21:31

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

QUOTE (Stepanich @ May 31 2018, 00:13)  Карлсон, полагаю (и знаю по различным проектам), что влияние термобарьеров очень сильно зависит от ряда факторов: толщины меди, размера и количества подключённых полигонов, количества слоёв, профиля пайки, способа пайки (конвекция или парофазная пайка) и прочего. У данного проекта есть требования. Одно из этих требований - наличие термобарьеров. Нельзя отступить от данного требования.

Предлагаю закрыть вопрос термобарьеров, т. к. их исключение не поможет решить исходную проблему с цепью СК. Упорство в ошибках с термобарьерами, доказывает отсутствие понимания вами их предназначения, да и образования по теме разводки плат. Требования монтажного цеха, без понимания сути проблемы к проектировщику, это "ржачно". Это как уборщица заставит ген директора делать то что ей нужно на предприятии. Страшный кошмар. Данные термобарьеры не уместны тут по причинам электрических сигналов, поскольку ухудшают ЭМИ. С отводом тепла никак не связаны, поскольку в термопечи по профилю все нагреается равно-температурно. Придуманы термобарьеры в основном для пайки выводных компонентов при ручном монтаже, либо для пропайки переходников открытых от маски. Вот посмотрите в томже гипертерме, какое это зло для путей тока и распределения температуры. Для вашего этого проекта, может тогда и откажетесь. Еще как вариант посмотрите в инете кучи плат аналогичных, не увидите там термобарьеров как у вас. ------ проблема с цепью СК. 1) неверный, ошибочный подвод диф пары к переходникам с обоих сторон. Нужно исправить. 2) не соблюдено правило 3W на некоторых участках. Нужно исправить, место есть. 3) проверить GND слои ниже выше над этой цепью. Проверить их целостность, сделать сшивку переходниками GND в соответствующих местах.

|

|

|

|

|

|

|

|

May 31 2018, 04:03 May 31 2018, 04:03

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Сейчас проблема именно в модели и именно с сигналом СК:

1. Фронты спада длиннее фронтов нарастания.

2. Изменение схемы терминации цепи СК дало положительный, но недостаточный эффект . Есть конечно немало вопросов с оглядкой на эту тему, где есть уже ряд ваших рассуждения касаемо разводки и наличия моделей к артиксу, но это пока/уже оставим. Тут все гораздо проще чем кажется- нужно просто начать проектировать и разводить не через задницу, а хотя бы нормально  Цитата Предлагаю закрыть вопрос термобарьеров, т. к. их исключение не поможет решить исходную проблему с цепью СК. Вы можете сколько угодно фантазировать на тему отсутствия влияния термалов в виа в хайспидных дизайнах, но на всякий случай напоминаю что у вас прежде всего кривая, ущербная разводка сигналов.  Опять же, насколько можно понять вы не удаляете неиспользуемые пады, стало быть проблема многократного antipad void crossing имеет место быть- это хорошо видно по вашим картинкам. Ну и учитывая кучу изломов, прямых углов, накрутку в антипадах, разный зазор между плечами диффпар при одинаковой их ширине и сильной связи в самой паре и еще кое-чего до кучи как минимум ясно две вещи: - вы "моделируете" что угодно, кроме своего дизайна, т.к. у вас при таких вводных вообще ни разу не uniform transmission line, сетап неверный. - вы упорно игнорируете целостность сигнала в рамках одного набора как такового. Поэтому обсуждать тут особенно нечего потому как в самом худшем и неочевидном случае представляется логичным сперва отлечивать все найденные проблемы какие есть в дизайне, пусть вам и ошибочно кажется что они якобы не относятся к "генеральной линии". Говоря проще, вы кладете болт на свой дизайн а потом втаптываете его в землю

|

|

|

|

|

|

|

|

May 31 2018, 07:54 May 31 2018, 07:54

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

QUOTE (Stepanich @ May 31 2018, 00:46)  Aner, спасибо за ответ. Мы обязательно поставим на место всех уборщиц и монтажников. Вы же не будете возражать, что наличие термобарьеров никак не сказывается на асимметрии сигнала СК? Ну хотя бы в модели?

Сейчас проблема именно в модели и именно с сигналом СК:

1. Фронты спада длиннее фронтов нарастания.

2. Изменение схемы терминации цепи СК дало положительный, но недостаточный эффект. Промоделируйте в гиперлинксе наличие термобарьеров увидите как скажется на асимметрии сигнала СК. Ну вашим монтажникам под маской эти термобарьеры ничего не дадут. То что термобарьер навредит это точно. Как рассуждаю с точки зрения спектрального анализа на разные скорости нарастания, спада ваших фронтов. У вас в спектре появляются чётные N-ные гармоники. Их происхождение от неравномерного волнового по диф паре, ее перегибам, окружению, переходам, земляным переходникам по ходу трассы. Все можно исправить, гиперлинкс покажет.

|

|

|

|

|

|

|

|

May 31 2018, 10:45 May 31 2018, 10:45

|

Знающий

Группа: Свой

Сообщений: 825

Регистрация: 28-11-07

Из: г.Винница, Украина

Пользователь №: 32 762

|

Цитата(Stepanich @ May 30 2018, 23:24)  Если суть замечаний - в наличии термического барьера, то это изменить нельзя, т. к. есть требования на качество пайки. Нет таких требований ни в одном стандарте. Никак термалы на переходных не скажутся на паяемость BGA. Даже теоретически. Тем более на плате, которая имеет 16 слоев, из которых половина, наверняка - сплошная медь. Вы хоть представляете какая у такой платы "тепловая масса"? Сколько тепла нужно, что бы прогреть такую плату и она нормалькно спаялась? Каким образом те нещастные термалы на переходных как-то повлияют на качество пайки BGA? Смотрите в суть явлений и не обращайте внимание на маловразумительные требования... P.S. Вы попробуйте помоделировать влияние термалов на пути обратных токов в хайспид дизайне - будете удивлены. Цитата(Stepanich @ May 30 2018, 23:24)  Если суть замечаний - в наличии гарантийных поясков в слоях, где нет подключения к полигонам или проводникам, то это изменить нельзя, т. к. это требование стандарта IPC-3 (см. сообщение 21). Кроме того, их наличие не влияет на описанную проблему с цепью CK. Еще как можно изменить. На внутренних слоях отсутствие гарантийных поясков для преходных на слое где нет подключения - норма. Читайте стандарт IPC-A-600, IPC-6011, IPC-6012, например, и связанные с ними. Особенно те стандарты, которые относятися к проектированию скоротных плат . И это не зависит от класса надежности платы. Любой пятак на переходном - увеличение его паразитной емкости, увеличение влияние на трассу, которая возле этого пятака проходит на малом расстоянии... А наличие дополнительных емкостей, влияющих на импеданс линии - это как раз путь к уменьшению крутизны сигналов. Кроме того, открою вам "Страшную тайну" - многие производители печатных плат по умолчанию убирают пятаки на внутренних слоях где нет подключения к переходным отверстиям. Если, конечно, явно не запретить им этого. Для того в САМ-редакторах и существуют инструменты, позволяющие делать подобные манипуляции с дизайном. Цитата(Stepanich @ May 30 2018, 23:39)  Если переходное отверстие, к которому подключён контакт, соединено с массивной областью меди (полигоном), то при оплавлении паяльной пасты тепло может от контакта "перейти" к полигону, что снизит воздействующую на пасту температуру и не позволит получить надёжное паяное соединение. Для снижения риска этого эффекта добавляют термический барьер. Наличие термического барьера в данном случае - требование монтажного цеха, и отступать от него нельзя. Гнать ссаными тряпками техногов, дающих подобные советы. Бред полный. А как же переходные непосредственно в паде, переходные для отвода тепла от "пуза" различных LCC, QFN, от площадок LGA и прочих D2PAK-ов? Оно же местами работать не будет, от слова вообще, если тармалов на такие переходные накидать... ИМХО, подобные советы могут давать только монтажники, которые сами не пониманимают техпроцесса пайки, начитались где то мануалов 20-летней давности и патаются переложить все возможные проблемы на конструктора, создавая тому лишние сложности.

--------------------

Тезис первый: Не ошибается лишь тот, кто ничего не делает.

Тезис второй: Опыт - великое дело, его не пропьёшь :).

|

|

|

|

|

|

|

|

May 31 2018, 12:41 May 31 2018, 12:41

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

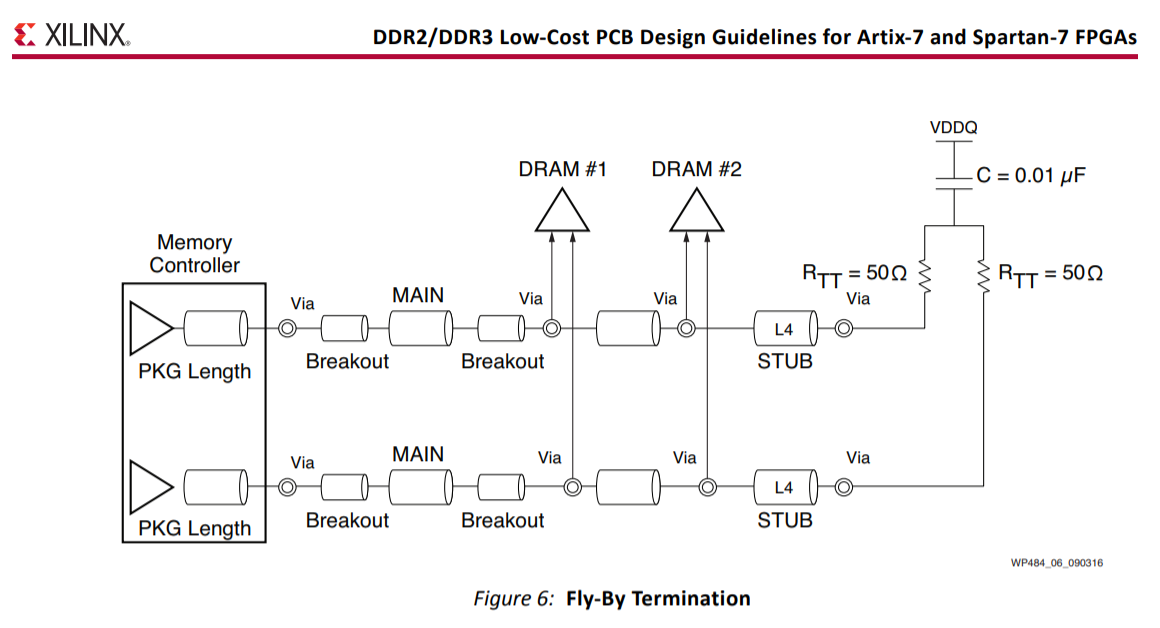

7 Series FPGAs SelectIO Resources User GuideThe memory interface related I/O standards such as SSTL and HSTL now support the SLEW attribute, and are selectable between both FAST and SLOW edge rates. The default SLEW for all I/O standards is SLOW, which has been the case for all I/O standards that supported the SLEW attribute in all previous FPGA families (namely LVCMOS and LVTTL). However, because this attribute is a new addition to the memory interface standards, if left unchanged (not specified in the RTL, UCF file, or I/O planning software), the default slew rates for these for these standards will result in much slower slew rates than in previous families. To achieve similar slew rates as in previous families, new designs now require the SLEW attribute to be specified and set

to FAST. Убедитесь что у вас не выбран reduced-strength driver - DIFF_SSTL15_R. Насколько можно понять по скринам, у вас для каждой микросхемы памяти отдельная шина адреса. Это вам действительно необходимо? Если нет - лучше используйте fly-by топологию.

Разрывать так плейны очень плохо. В Editor Control -> Tunning Patterns устанавите Miter ratio. То как вы подключаете low ESL кондеры, у вас похоже стоят 0306, нивелирует их характеристики. Да тут и не нужны 0306. Хотите понтов - ставте уже тогда NFM ы вдобавок к основным 0402. Только правильно их подключите. Да и так трассировать, в 16 слоях... Мой вам совет - откройте референс боард Кслаинкса и посмотрите как люди трассируют, тот же флай бай.

|

|

|

|

|

|

|

|

May 31 2018, 13:20 May 31 2018, 13:20

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(EvilWrecker @ May 30 2018, 21:12)  Это которая "export coupled segments"? Да. Цитата(EvilWrecker @ May 30 2018, 21:12)  Я может что-то в ветке пропустил, но у вас совершенно другая модель линии(в частности без виа)- особенно неясно почему нет TL между ддр3 и терминаторами, зато есть в самой терминации. Overshoot/pre-shoot как у ТС у вас нет, параметры TL между контролером и ддр3 разобрать нереально, но похоже что они одинаковые- что моделируется в этом сетапе?  Перечитайте мою фразу еще раз. Я удалил все лишние линии между передатчиком и приемником, чтобы показать что и в идеальном случае проблема останется. Цитата(EvilWrecker @ May 30 2018, 21:12)  Как вы себе это представляете? Например вот так

Играя номиналами резисторов можно управлять точкой пересечения фронтов.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

May 31 2018, 13:31 May 31 2018, 13:31

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Да. Понятно, спасибо- тогда позвольте уточняющий вопрос: это единственная галка которая управляет механизмом разбивки? О чем речь: соединение TL "бесшовное"в показанном ТС случае, но очевидно что при прямых(а тем более острых) углах, накрутке в антипаде и пр. соединение бесшовным быть не должно- т.е. в лучшем случае само число TL не будет равно числу сегментов трасс. Как происходит разделение? Цитата Перечитайте мою фразу еще раз. Я удалил все лишние линии между передатчиком и приемником, чтобы показать что и в идеальном случае проблема останется. Я понимаю о чем вы говорите  Мой посыл заключается в том, что не нужно лечить в одном месте- вот вы пишите: Цитата Например вот так Играя номиналами резисторов можно управлять точкой пересечения фронтов. можете гарантировать такой же эффект со стабильным повторением в оригинальной плате ТС- вестимо со всеми озвученными ранее проблемами? Это все хорошо работает, когда в остальных местах "проблем нет"  . Плюс overshoot у вас также остается(слегка переделанный проект ТС?)

|

|

|

|

|

|

|

|

May 31 2018, 14:02 May 31 2018, 14:02

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Он вас спрашивал только о том как решить проблему Vix. А вы вместо предложения решения уже 3 страницы обсуждаете его топологию. А что тут неясного? По умолчанию контроллер генерирует условно "нормальный" сигнал, ведь он сам по себе JEDEC- compliant, вы помните?  Стало быть, проблема как минимум в интерконнектах- минимум, потому что термалы в reutrn path дают массу неочевидных проблем, и это не касаясь темы PI. Что спрашивали, то и ответили  Цитата По поводу предложенной мной схемы согласования есть какие-то конкретные мысли? Желательно без словоблудия. Кроме факта того что она никоим образом не связана с платой ТС- никаких  Терминация клока сама по себе должна работать без всяких ухищрений в виде дополнительных согласований, все проблемы решаются или в интерконнектах или в настройках контроллера. Ваша модель имеет сугубо умозрительную ценность.

|

|

|

|

|

|

|

|

May 31 2018, 14:14 May 31 2018, 14:14

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

вот еще, в коллекцию. "Termination to GND is recommended for the clock signals to provide a good path for common mode noise." Не понимаю я смысл. В IBIS есть возможность выбора - SLOW, FAST. Ксайлинкс пишет что необходимо установить FAST. Так зачем в Hyperlynx менять? Ведь по установке этих галочек, Hyperlynx выбирает соответствующий режим в IBIS. Но мы же его сами должны установить DIFF_SSTL15_F(AST)_HR

|

|

|

|

|

|

|

|

May 31 2018, 14:59 May 31 2018, 14:59

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата "Termination to GND is recommended for the clock signals to provide a good path for common mode noise." Есть неплохие презентации( 1, 2), в которой перечислены причины возникновения CM noise в диффпаре(для тех кто не знает  )- так вот суть в том, что если в хайспидах внезапно в диффпаре много CM noise, то это означает что либо это не вполне диффпара, либо она говно  Цитата Так логичнее исправлять источник проблемы, а не бороться с последствиями. Именно.

|

|

|

|

|

|

|

|

May 31 2018, 15:16 May 31 2018, 15:16

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Всем доброго дня. 1. Ошибка с различным расстоянием между проводниками устранена.

Выполнено сравнительное моделирование "ДО" и "ПОСЛЕ".

Бирюзовый и фиолетовый - "до". Красный и зелёный - "после". Разница практически отсутствует. 2. IBIS модель драйвера: SSTL15_F_HR (прикладываю):  SSTL15_F_HR.txt

SSTL15_F_HR.txt ( 38.17 килобайт )

Кол-во скачиваний: 163. Посадочное место под конденсаторы LLL153C70G474ME17:

|

|

|

|

|

|

|

|

May 31 2018, 15:48 May 31 2018, 15:48

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Выполнено сравнительное моделирование "ДО" и "ПОСЛЕ". По правде говоря учитывая все ваши промахи до этого видится затруднительным верить результатам моделирования под вашим авторством- есть стойкое мнение что вы это делаете не лучше чем разводите  С "моделью" ситуация аналогичная. К слову еще раз про терминацию- хилые тоже недалеко ушли от стандартного пути   Но вот что интересно стало-насколько понять, у вас ниже артикса 2 микрульки ддр3: они же на разные контроллеры заведены? Ну так, на всякий  Цитата Посадочное место под конденсаторы LLL153C70G474ME17 И что вы хотите этим сказать? В документе даны диапазоны, а у вас конкретные фиксированные числа- вот их и назовите.

|

|

|

|

|

|

|

|

May 31 2018, 15:51 May 31 2018, 15:51

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(Corvus @ May 31 2018, 17:29)  Так логичнее исправлять источник проблемы, а не бороться с последствиями. Вот вам эквивалентная схема

идеальной "разводки" - передатчик и приемник соединены двумя диф. трассами и напрямую подключена развязка, предложенная в самом начале знатоками. Попробуйте теперь решить проблему Vix всеми известными вам способами. И объясните пожалуйста, в чем здесь источник проблемы? Модель передатчика выложена ТС, модель памяти найти не проблема (имя указано на схеме), номера пинов указаны также.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

May 31 2018, 17:03 May 31 2018, 17:03

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

Цитата(Stepanich @ May 31 2018, 18:16)  2. IBIS модель драйвера: SSTL15_F_HR (прикладываю): Не подключилась ваша модель. У меня вышло вроде бы вложиться - Slow 868mV, Fast - 705mV.

Скачал IBIS c сайта. В проекте OBUFDS_inst : OBUFDS generic map ( IOSTANDARD => "DIFF_SSTL15", SLEW => "FAST") port map ( O => DDR_CLK_p, OB => DDR_CLK_n, I => clk_in ); В Implemented Design экспортировал, указав Updated generic IBIS and Updated parasitics package. Хотя модели 2013 года. Ну и Вивадо у меня 2015.4, тот который с Артиксом ставился. С кондером Ccomp - Fast 840mV, Slow на том же уровне.  CLk_DDR.txt

CLk_DDR.txt ( 231.8 килобайт )

Кол-во скачиваний: 63Signal - DDR_CLK

|

|

|

|

|

|

|

|

May 31 2018, 17:25 May 31 2018, 17:25

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Вполне возможно. Но ее не я выбирал, а ТС. Именно об этом я и написал пару постов назад  Цитата У меня вышло вроде бы вложиться К вашей картинке по правде говоря тоже вопросы есть  - но скажите, можете ли показать то же самое но с TL 50 Ом(плюс минус 2-3Ом) на основном пути клока? Причем так чтобы было видно целый период.

|

|

|

|

|

|

|

|

May 31 2018, 18:05 May 31 2018, 18:05

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(Volkov @ May 31 2018, 20:03)  Не подключилась ваша модель.

У меня вышло вроде бы вложиться - Slow 868mV, Fast - 705mV.

В проекте

OBUFDS_inst : OBUFDS

generic map (

IOSTANDARD => "DIFF_SSTL15",

SLEW => "FAST")

port map (

O => DDR_CLK_p,

OB => DDR_CLK_n,

I => clk_in

);

В Implemented Design экспортировал, указав Updated generic IBIS and Updated parasitics package. Хотя модели 2013 года. Ну и Вивадо у меня 2015.4, тот который с Артиксом ставился.

С кондером Ccomp - Fast 840mV, Slow на том же уровне.

Signal - DDR_CLK Параметры модели отличаются, хотя и название одно и тоже. Вот результаты с вашей и с той моделью что дали мне.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

May 31 2018, 18:08 May 31 2018, 18:08

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

Вот что. С 50 Ом трассой, и терминацией 50 Ом + Джиттер.

С 40 Ом трассой, и терминацией 40 Ом + Джиттер.

С 40 Ом трассой, и терминацией 40 Ом + Сcomp 3 pF + Джиттер.

|

|

|

|

|

|

|

|

May 31 2018, 18:18 May 31 2018, 18:18

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Вот результаты с вашей и с той моделью что дали мне. Для большей читаемости можно показать то же самое, но не используя один и тот же цвет для разных результатов? Цитата Вот что. Здесь конечно сразу будут вопросы о том как вы задали джиттер(как мне помнится в гиперлинксе их несколько типов с настройкой магнитуды и пр), но вы можете показать весь сигнал? Не буду скрывать, хочу в том числе посмотреть что будет с искажением  Ну и раз стали использовать 40Ом, то очевидно имеет смысл прогнать отдельно такой вариант с измененными значениями терминирующих резисторов.

|

|

|

|

|

|

|

|

May 31 2018, 18:46 May 31 2018, 18:46

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Volkov, спасибо за участие. 1. Две микросхемы памяти имеют независимые шины адреса намеренно. Обе микросхемы в связке работать не должны. В плате реализовано резервирование памяти. 2. Не понимаю, почему у вас модель не подключилась. Какая ошибка? Напоминаю, что проблема с величиной Vix только в режиме Fast. Ниже привожу рисунки для режима typical:

Интересно, как вам удалось (пост 48) улучшить результат почти на 40% (162 мВ против 263 мВ в посте 6).

|

|

|

|

|

|

|

|

May 31 2018, 20:23 May 31 2018, 20:23

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

Цитата(Stepanich @ May 31 2018, 21:46)  Интересно, как вам удалось (пост 48) улучшить результат почти на 40% (162 мВ против 263 мВ в посте 6). Не знаю. Похоже ваша модель - это SSTL15_F_HR. А в моей DIFF_SSTL15_F_HR. С джиттером долго разбираться, но похоже 1 UI слишком оптимистично. На выходе MMCM будет минимум 75 ps - 3%/. По поводу конденсатора - то в JEDEC референсах он стоит на планках возле разъема. В Memory Down - нет требований по длине перед ним, но есть минимум Main Route + Neck-Down 500 mil после него. чем длиннее трасса перед ним - тем сильнее он валит фронт.

|

|

|

|

|

|

|

|

Jun 1 2018, 06:49 Jun 1 2018, 06:49

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(Volkov @ May 31 2018, 23:23)  Не знаю. Похоже ваша модель - это SSTL15_F_HR. А в моей DIFF_SSTL15_F_HR. В вашем файле модели нет секции [Package Model] соответственно и нет доп. паразитных параметров которые должны были прописаться из файла ffg1156_7a200t.pkg, а они то как раз и проводят к сдвигу фронтов на 150ps и повышению точки пересечения на 22mV, и выходу за пределы допуска Vix.

В прочем в файле ffg1156_7a200t.pkg написано Код The data in this model has been generated with the utmost care and is believed to be accurate, although accuracy cannot be guaranteed. This model has not been correlated with lab measurements. . Т.е. насколько можно доверять этим данным и их учитывать непонятно.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

Jun 1 2018, 07:25 Jun 1 2018, 07:25

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата В вашем файле модели нет секции

[Package Model]

соответственно и нет доп. паразитных параметров которые должны были прописаться из файла ffg1156_7a200t.pkg

а они как раз и проводят к сдвигу фронтов на 150ps и повышению точки пересечения на 22mV, и выходу за пределы допуска Vix. Ну хоть кто-то это сказал наконец  -дык, у хилых есть отдельные пункты на эту тему( 1, 2) а также строчки в документах  Т.е. раз за разом тема возвращается к кривости сетапа  Цитата Т.е. насколько можно доверять этим данным и их учитывать непонятно. А больше и неоткуда взять эти данные  - ну только если не запустить экстракцию параметров из всей конструкции(die+package) в HFSS и оттуда уже получать информацию, но этот способ очевидно не подойдет. Еще пару слов за сетап: представляется мягко говоря логичным прогнать сначала модель при идеальном интерконнекте, вестимо чтобы оценить не только ее корректность, но и работоспособность как таковую- на том же форуме хилых есть темы от людей у которых модели не взлетели. Далее, как только понятно что все ок, уже можно искать "пределы работоспособности", уродовать связи, играть с таймингами и пр.- тут же столько возни, а все напрасно, потому как с самого начала все сделано через задницу

|

|

|

|

|

|

|

|

Jun 1 2018, 15:30 Jun 1 2018, 15:30

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

Да, действитель не добавились. Но тут, похоже, не только паразиты. Если менять длину линии, то можно видеть максимумы и минимумы VIX. При 1.6 - 930мВ, при 2.05 - 878мВ

Похоже, что на драйвер влияет отраженный сигнал. Насколько это точно просчитывается, и можно ли таким образом подогнать длину линии, вот это интересно.

|

|

|

|

|

|

|

|

Jun 1 2018, 16:00 Jun 1 2018, 16:00

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

Другая модель. Длина основного сегмента - 2.9 in.

Длина основного сегмента - 3.1 in.

|

|

|

|

|

|

|

|

Jun 1 2018, 16:04 Jun 1 2018, 16:04

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Volkov, попробовал две различные длины основного участка: исходную 1.55 дюйма и увеличенную до 10 дюймов. Точка пересечения приблизилась к идеалу на 41 мВ:

Времена: Исходная 1.55 дюйма: Avg fall time: 120.780 ps Min fall time: 120.780 ps High voltage: 1.15 V Max fall time: 120.780 ps Low voltage: 318.4 mV Avg rise time: 100.318 ps Min rise time: 100.318 ps Low voltage: 389.2 mV Max rise time: 100.318 ps High voltage: 1.17 V Увеличенная до 10 дюймов: Avg fall time: 90.678 ps Min fall time: 90.678 ps High voltage: 1.24 V Max fall time: 90.678 ps Low voltage: 760.5 mV Avg rise time: 92.021 ps Min rise time: 92.021 ps Low voltage: 330.9 mV Max rise time: 92.021 ps High voltage: 868.5 mV

|

|

|

|

|

|

|

|

Jun 2 2018, 08:10 Jun 2 2018, 08:10

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(Volkov @ Jun 1 2018, 18:30)  Похоже, что на драйвер влияет отраженный сигнал. Насколько это точно просчитывается, и можно ли таким образом подогнать длину линии, вот это интересно. Запускаете Sweep и смотрите. Например изменение длины от 2 до 20см с шагом 1см - Vix постепенно опускается на 29mV:

Изменение импеданса линии естественно влияет на форму сигнала, но не на точку Vix.

40 - желтый 50 - зеленый 60 - красный ширина линии 100мкм, зазор 100мкм, длина 3см Ну и изменение формы при изменении длины

2-8-14-20см зеленый-красный-желтый-голубой

2-4-6-8-10см Т.е. при 8см имеем практически идеальный сигнал.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

Jun 2 2018, 12:36 Jun 2 2018, 12:36

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

Цитата(EvilWrecker @ Jun 1 2018, 21:14)  "Идеально"- это как на вашей прошлой картинке? Лучше чем 50 и 50?  Это как на картинке слева - намного лучше. А вот справа - трасса на 0.4 дюйма длиннее. При тех же импедансах - 40 /60.

|

|

|

|

|

|

|

|

Jun 2 2018, 14:21 Jun 2 2018, 14:21

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

Цитата(EvilWrecker @ Jun 2 2018, 16:28)  Меня конечно веселят ваши уходы от прямого ответа  (в частности от вопроса касаемо происхождения TL в 40 и 60 Ом), однако тут нельзя не отметить что эта картинка слева идеалом ни разу не является  А почему бы вам не ответить, на свой же вопрос. Где будет более открытый eye, а где наименее, если 50/50 ? И почему так будет происходить. Вы же как бы это знаете, так просветили бы.  Цитата(EvilWrecker @ Jun 2 2018, 16:28)  идеалом ни разу не является  Меня устраивает, даже длину с меньшим резонансом подогнал. Если это резонанс, хотя что же, если не оно.

|

|

|

|

|

|

|

|

Jun 2 2018, 14:54 Jun 2 2018, 14:54

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата А почему бы вам не ответить, на свой же вопрос. Вы знаете, читая строчки вроде этой: Цитата Меня устраивает, даже длину с меньшим резонансом подогнал. Если это резонанс, хотя что же, если не оно. а также припоминая ваши ответы из других тем, должен таки согласиться с вами в том, что ответ на свой собственный вопрос мне самому все же известен и вполне себе давно  Что же касается другой части, а именно: Цитата так просветили бы. Просветительской деятельностью к сожалению не занимаюсь, для меня электроникс является по большей части смесью пикабу с уродру- уж такие темы с таким контентом и подавно

|

|

|

|

|

|

|

|

Jun 4 2018, 14:39 Jun 4 2018, 14:39

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

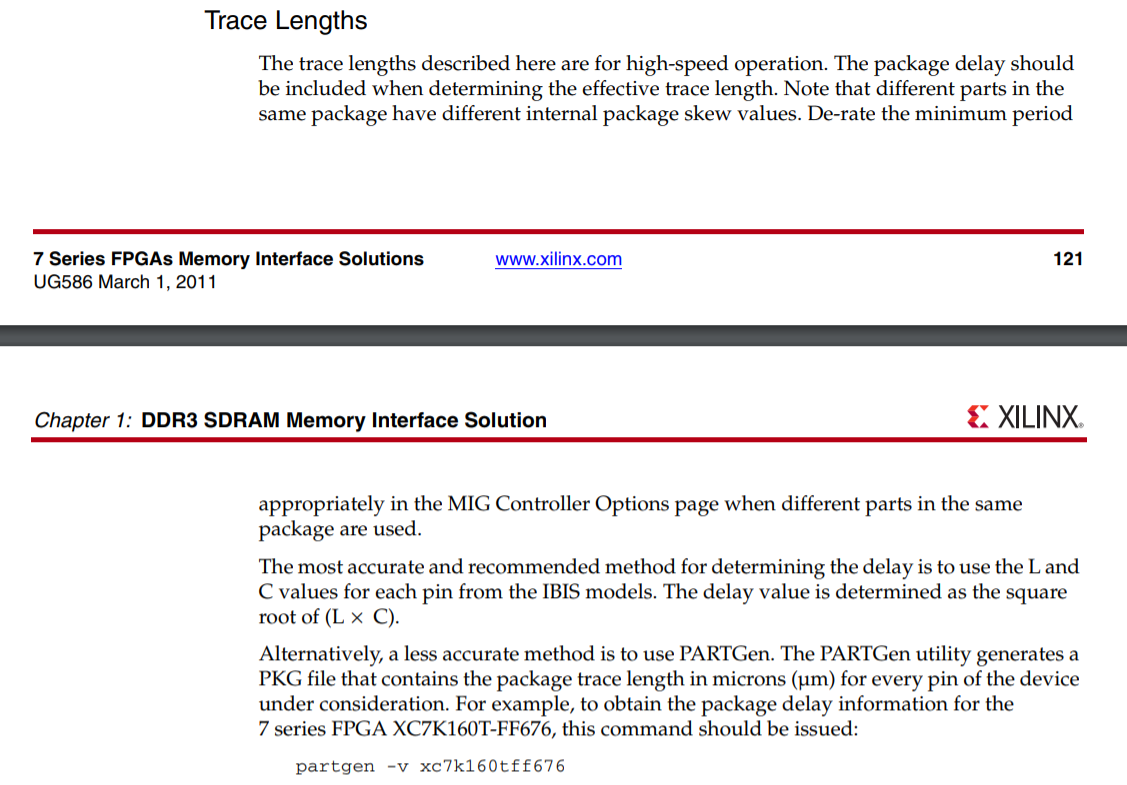

Volkov или другие специалисты, вы не подскажете с учётом влияний паразитностей корпуса на задержку?

Необходимо получить данные по задержкам внутри корпуса. Для ПЛИС (xc7a200tffg1156-2) всё просто: есть данные, выгруженные из Vivado. Например, для AL34, задержка составляет от 164,101 до 165,751 пс. Проверяем по IBIS (берём данные из Inductance и Capacitance Matrix): корень(7,22116е-11*3,76679е-12) = 164,92 пс.

Для памяти MT41J128M16JT есть как Inductance и Capacitance Matrix, так и значения в начале модели, причём эти данные не совпадают. Например, для вывода A1 индуктивность в начале указана 1,755 нГн, а в разделе Inductance Matrix 2,28 нГн. Какое значение брать?

Спасибо.

|

|

|

|

|

|

|

|

Jun 4 2018, 19:11 Jun 4 2018, 19:11

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

Изучите JEDEC STANDARD для вашей DDR3L SDRAM, поскольку она соответствует своему стандарту. Задержки там все приведены к "нулю" внутри микросхемы. Можете убедиться, перевернув и посмотрев вашу DDR3L SDRAM под микроскопом, ту многослойку с BGA шариками. Там видны меандры, трамбоны до нужных площадок, шаров BGA. Зачем вам что-то еще брать? Будет другой производитель DDR3L с другими параметрами, но все допуски и разбросы "нуля"оговорены. Думаю вам нужно заниматься другой стороной, вашей ПЛИС, задержкой внутри корпуса и трассой до вашей памяти только. Тем более что скорости у вас "никакие", допуски "огромные".

И еще поймите, что внутри всех DDR2/3/4/5 находится сложный умный логический автомат по подстройки сотни параметров по частотам, времянкам, уровням. Который сильно облегчает жизнь всем вашим точным подгонкам.

|

|

|

|

|

|

|

|

Jun 4 2018, 20:16 Jun 4 2018, 20:16

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

QUOTE (Stepanich @ Jun 4 2018, 22:37)  Aner, спасибо. То есть правило такое: выравниваем трассы только с учётом задержек внутри ПЛИС, а задержки внутри корпуса памяти не учитываем, т. к. они скомпенсированы производителем?

Ещё вопрос в тему: при разводке PCI Express x4 gen. 2 также нужно учитывать задержки внутри корпуса ПЛИС (Artix-7), или они уже скомпенсированы производителем? Еще раз изучайте стандарты того что применяете, на подсказках далеко не уедете! ... задержки внутри корпуса памяти не учитываем, т. к. они скомпенсированы и соответствуют стандартам! Задержки внутри корпуса ПЛИС не могут быть скомпенсированы которые даны пользователю для использование в различных проектах, разных конфигурациях; IP блоки их реализации могут быть исключением, также аппаратный интерфейс DDR, но это все описано и даны подробности в AN. Думаю для PCI Express x4 gen. 2 нужно учитывать задержки внутри корпуса ПЛИС (Artix-7) если в выбранной вами реализации IP Core не поддержана реализация автомата компенсации.

|

|

|

|

|

|

|

|

Jun 4 2018, 20:22 Jun 4 2018, 20:22

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

У Xilinx даже аппаратный контроллер в Zynq требует учёта задержек внутри корпуса; вот тема с их форума. По PCIe напишу здесь, когда выясню.

|

|

|

|

|

|

|

|

Jun 4 2018, 20:43 Jun 4 2018, 20:43

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

Там же вот ответ по Цинку: ... open a synthesized design ... ...The easiest way to export the pin flight time information is to open a synthesized design and in either the IO Ports or Package Pins view right click in the area, select "Export I/O Ports", select CSV, and then press OK. When you open the CSV file you'll see the PS memory interface pins in the "Site Type" column starting with "PS_". QUOTE (Stepanich @ Jun 4 2018, 23:36)  Aner, понятно. Сейчас говорим про Артикс.

Наверное, поэтому для Артикса рекомендуется задерживать такт относительно строба на 150 пс и более (при допустимой задержке от 0 пс) - так проще выбрать задержку с фиксированными дискретами. Непонял, вы что только плату разводите? А сам проект на Артиксе кто-то другой делает?

|

|

|

|

|

|

|

|

Jun 4 2018, 20:59 Jun 4 2018, 20:59

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

QUOTE (Stepanich @ Jun 4 2018, 23:51)  Aner, несоответствие стандарту по уровню пересечения дифф. сигнала СК. Сейчас симуляция, разумеется. Причин может быть много, разных и неожиданных. Больше походит на влияние окружения, плохой земли, ... может не на самой трассе а на питание LVDS драйверов. Если много слоев, пробуйте перенести в другой слой этот CK (обязательно между земляными) может будет зацепка и найдете влияние. Еще пробуйте ваш меандры перевести в трамбоны, причем только на одной стороне линии, не так как сейчас на вашей каринке. Мой пример для CK.

|

|

|

|

|

|

|

|

Jun 5 2018, 18:17 Jun 5 2018, 18:17

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Товарищи, всем спасибо за ответы. На форуме Xilinx ответили про PCI Express: данные задержек применять надо.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|