| |

Altera USB программатор дайте схему Altera USB программатор дайте схему |

|

|

3 страниц  1 2 3 >

1 2 3 >

|

|

Ответов

(1 - 33)

|

|

Feb 15 2009, 13:22 Feb 15 2009, 13:22

|

Местный

Группа: Свой

Сообщений: 371

Регистрация: 24-07-05

Из: Москва

Пользователь №: 7 056

|

Цитата(_Ivan_33 @ Feb 14 2009, 18:41)  поделитесь пожалуйста схемой программатора ALtera под USB, а то лпт сожжен...

и платки тестовой какой-нить под epm7128 ни у кого не находилось??? Вот еще мой вариант программатора: http://www.mcu-cpld.narod.ru/Altera/USB-blaster.html

|

|

|

|

|

|

|

|

Feb 18 2009, 10:11 Feb 18 2009, 10:11

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

Цитата(_Ivan_33 @ Feb 14 2009, 18:41)  поделитесь пожалуйста схемой программатора ALtera под USB, а то лпт сожжен...

и платки тестовой какой-нить под epm7128 ни у кого не находилось??? Вот еще подборка, когда-то сам собирал - схема, заливка в epm и ftdi.

|

|

|

|

|

|

|

|

Mar 4 2009, 17:01 Mar 4 2009, 17:01

|

Частый гость

Группа: Свой

Сообщений: 76

Регистрация: 6-03-05

Из: Новосибирск

Пользователь №: 3 121

|

Цитата(RYury @ Feb 18 2009, 16:11)  Вот еще подборка, когда-то сам собирал - схема, заливка в epm и ftdi. Хочу повторить. Правильно ли я понял, что прошивка altera.ept прошивается в еепромку с помощью какой-то фтдишной утилиты? Что-то с маху на их сайте не нашел описание сего процесса, подскажите что и как делается.

|

|

|

|

|

|

|

|

Mar 5 2009, 12:44 Mar 5 2009, 12:44

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

Цитата(studert @ Mar 4 2009, 20:01)  Правильно ли я понял, что прошивка altera.ept прошивается в еепромку с помощью какой-то фтдишной утилиты? altera.ept шьется в ftdi микросхему c помощью программы MProg. Драйвера и MProg для ftdi можно взять на www.efo.ru Драйвера - ftp://ftp.efo.ru/pub/ftdichip/Drivers/com...M%202.02.04.exeУтилита - ftp://ftp.efo.ru/pub/ftdichip/Utils/MProg3.5.zipВ Altera (max3064 или max7064 или другие) шьется проект из папки cpld или переработанный des00 в одноименном каталоге.

|

|

|

|

|

|

|

|

Mar 5 2009, 13:30 Mar 5 2009, 13:30

|

Частый гость

Группа: Свой

Сообщений: 76

Регистрация: 6-03-05

Из: Новосибирск

Пользователь №: 3 121

|

Цитата(RYury @ Mar 5 2009, 18:44)  altera.ept шьется в ftdi микросхему c помощью программы MProg. Драйвера и MProg для ftdi можно взять на www.efo.ru Драйвера - ftp://ftp.efo.ru/pub/ftdichip/Drivers/com...M%202.02.04.exeУтилита - ftp://ftp.efo.ru/pub/ftdichip/Utils/MProg3.5.zipВ Altera (max3064 или max7064 или другие) шьется проект из папки cpld или переработанный des00 в одноименном каталоге. Спасибо. Вроде теперь все стало понятно, как сделают плату попробую повторить.

|

|

|

|

|

|

|

|

Mar 11 2009, 10:01 Mar 11 2009, 10:01

|

Участник

Группа: Новичок

Сообщений: 68

Регистрация: 2-03-07

Пользователь №: 25 817

|

Может оффтоп. А схемку USB-программатора для Xilinx никто не встречал? Ссылочкой не поделитесь?

Сообщение отредактировал Waldemarius - Mar 11 2009, 10:02

|

|

|

|

|

|

|

|

Mar 11 2009, 10:53 Mar 11 2009, 10:53

|

Частый гость

Группа: Свой

Сообщений: 199

Регистрация: 29-07-08

Из: Серпухов

Пользователь №: 39 283

|

Цитата(Waldemarius @ Mar 11 2009, 13:01)  Может оффтоп. А схемку USB-программатора для Xilinx никто не встречал? Ссылочкой не поделитесь? Сделал товарищ АДИКМ есть гербера . Смотри USB-to-JTAG шнурок для XILINX

|

|

|

|

|

|

|

|

Apr 3 2009, 05:02 Apr 3 2009, 05:02

|

Частый гость

Группа: Свой

Сообщений: 76

Регистрация: 6-03-05

Из: Новосибирск

Пользователь №: 3 121

|

Цитата(RYury @ Feb 18 2009, 17:11)  Вот еще подборка, когда-то сам собирал - схема, заливка в epm и ftdi. Собрал устройство по схеме из архива (упразднив SN65220 и раскидав ножки плис в другом порядке, для удобства разводки), но работает только jtag режим, пробовал обе прошивки. Это ограничение данного проекта или я что-то сделал не так? В режиме Active serial пишет Error: Can't recognize silicon ID for device 1. Ниже прилагаю схему и архив всего пректа для Altium designer, может еще кому пригодится.

Эскизы прикрепленных изображений

|

|

|

|

|

|

|

|

Apr 3 2009, 09:21 Apr 3 2009, 09:21

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

to Studert должен работать AS режим. На схеме(картинка) не видно - куда подключены остальные пмны кроме jtag. Вот назначения всех пинов (взято из верилог кода des00): input wire B_TDO; // JTAG input: TDO, AS/PS input: CONF_DONE input wire B_ASDO; // AS input: DATAOUT, PS input: nSTATUS output logic B_TCK; // JTAG output: TCK to chain, AS/PS DCLK output logic B_TMS; // JTAG output: TMS to chain, AS/PS nCONFIG output logic B_NCE; // AS output: nCE output logic B_NCS; // AS output: nCS output logic B_TDI; // JTAG output: TDI to chain, AS: ASDI, PS: DATA0 output logic B_OE; // LED output/output driver enable И кусок схемы

Эскизы прикрепленных изображений

|

|

|

|

|

|

|

|

May 27 2009, 11:43 May 27 2009, 11:43

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

Цитата(призрак @ May 27 2009, 14:27)  Error: Design requires 8 output enable signals, but the device can contain only 6 output enable signals проект умещается в чипы начиная от max3064, крисстал верно выбрали?

|

|

|

|

|

|

|

|

May 29 2009, 09:53 May 29 2009, 09:53

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

Цитата(призрак @ May 29 2009, 08:55)  И такой вопрос - если я буду использовать FT245К - это повлияет на файл прошивки? Наверное имелось ввиду FT245R. Файл прошивки тот же и для FT245BM и для FT245R. PS: Попробовал скомпилить, для этого скачал usb_blaster.rar, в папке des00 выбрал файл mjtag_logic.v, выбрал чип EPM3064ATC44-10, в Settings установил галку SystemVerilog-2005. Компиляция (Quartus90_SP1) прошла успешно.

|

|

|

|

|

|

|

|

May 29 2009, 12:11 May 29 2009, 12:11

|

Местный

Группа: Свой

Сообщений: 216

Регистрация: 12-12-06

Из: Москва

Пользователь №: 23 439

|

Для 7064 выдала : Error: Design requires 8 output enable signals, but the device can contain only 6 output enable signals Error: Can't find fit Error: Quartus II Fitter was unsuccessful. 2 errors, 0 warnings Error: Peak virtual memory: 163 megabytes Error: Processing ended: Fri May 29 16:00:10 2009 Error: Elapsed time: 00:00:03 Error: Total CPU time (on all processors): 00:00:01 Error: Quartus II Full Compilation was unsuccessful. 4 errors, 1 warning Заменил как ты писал на EPM3064ATC44-10 и поставил галку, выдала следующее: Error: I/O standard TTL is not supported for selected device family Error: Quartus II Fitter was unsuccessful. 1 error, 0 warnings Error: Peak virtual memory: 162 megabytes Error: Processing ended: Fri May 29 16:02:39 2009 Error: Elapsed time: 00:00:03 Error: Total CPU time (on all processors): 00:00:01 Error: Quartus II Full Compilation was unsuccessful. 3 errors, 1 warning Теперь по ножкам - в тексте : CLK : IN STD_LOGIC; -- external 24/25 MHz oscillator nRXF : IN STD_LOGIC; -- FT245BM nRXF nTXE : IN STD_LOGIC; -- FT245BM nTXE B_TDO : IN STD_LOGIC; -- JTAG input: TDO, AS/PS input: CONF_DONE B_ASDO : IN STD_LOGIC; -- AS input: DATAOUT, PS input: nSTATUS  B_TCK : BUFFER STD_LOGIC; -- JTAG output: TCK to chain, AS/PS DCLK B_TMS : BUFFER STD_LOGIC; -- JTAG output: TMS to chain, AS/PS nCONFIG B_NCE : BUFFER STD_LOGIC; -- AS output: nCE  B_NCS : BUFFER STD_LOGIC; -- AS output: nCS  B_TDI : BUFFER STD_LOGIC; -- JTAG output: TDI to chain, AS: ASDI, PS: DATA0 B_OE : BUFFER STD_LOGIC; -- LED output/output driver enable nRD : OUT STD_LOGIC; -- FT245BM nRD WR : OUT STD_LOGIC; -- FT245BM WR D : INOUT STD_LOGIC_VECTOR(7 downto 0) -- FT245BM D[7..0] Как то со схемой не стыкуется(

|

|

|

|

|

|

|

|

May 29 2009, 15:32 May 29 2009, 15:32

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

вы не из той папки берете файл. Возьмите из папки des00 файл mjtag_logic.v (язык SystemVerilog). Этот файл компилится нормально. Хотя и файл jtag_logic.vhd (язык VHDL) из папки cpld компилится нормально начиная с семейства MAXII, я думаю что это глюки квартусовского VHDL компилятора, т.к. файл mjtag_logic.v это переработанный des`ом исходный файл jtag_logic.vhd, за что ему спасибо. Цитата(призрак @ May 29 2009, 16:11)  Теперь по ножкам - в тексте : ... всё там правильно, дополнительные ноги для режимов AS mode и PS mode, а не только для JTAG. Цитата(призрак @ May 29 2009, 16:11)  Как то со схемой не стыкуется... в схеме нарисован только JTAG, а если хочется AS mode и PS mode необходимо подключить соответствующие сигналы на разъем. Кусок схемы подключения приведен в этой теме в предыдущих постах, пролистайте назад и увидите.

|

|

|

|

|

|

|

|

Jun 1 2009, 13:41 Jun 1 2009, 13:41

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

Цитата(rv3dll(lex) @ Jun 1 2009, 08:55)  а как нибудь попроще можно. чтобы спаять, прошить и заработало? единственное -> jtag для целевой платы c 3.3V(5V) уровнями, для меньших напряжений необходимо ставить преобразователи уровней

|

|

|

|

|

|

|

|

Jul 10 2009, 05:57 Jul 10 2009, 05:57

|

Группа: Участник

Сообщений: 4

Регистрация: 18-10-05

Пользователь №: 9 771

|

Стараюсь повторить схемы, возникли пара вопросов. 1. в разных источниках указаны разные кварцы, 24 - 48 - 60МГц. Чем определяется? Под рукой есть резонатор 24.576 и генератор 60. Ещё подмывает поэкспериментировать с некварцованным генератором внутри плис на трёх закольцованных инверторах с задержкой. Но для этого надо понять роль сигнала clk и требования к нему. 2.два триггера после входа клока просто делят на 4 входной сигнал? Получается 15МГц про 60 входных. Схема строго на 60 или на 48 такая же? Просто на готовой плате генератора нет, но есть отвод от 6МГц кварца, если умножить - получится 12... Сколько в этой схеме допустимый нижний предел? Разобрал альтеровский оригинал - там 24 стоит

Сообщение отредактировал AlexKooper - Jul 10 2009, 06:31

|

|

|

|

|

|

|

|

Jul 10 2009, 16:46 Jul 10 2009, 16:46

|

Знающий

Группа: Свой

Сообщений: 716

Регистрация: 27-05-05

Из: Kyiv

Пользователь №: 5 454

|

Цитата(AlexKooper @ Jul 10 2009, 08:57)  Стараюсь повторить схемы, возникли пара вопросов.

1. в разных источниках указаны разные кварцы, 24 - 48 - 60МГц. Чем определяется? Под рукой есть резонатор 24.576 и генератор 60. Ещё подмывает поэкспериментировать с некварцованным генератором внутри плис на трёх закольцованных инверторах с задержкой. Но для этого надо понять роль сигнала clk и требования к нему.

2.два триггера после входа клока просто делят на 4 входной сигнал? Получается 15МГц про 60 входных. Схема строго на 60 или на 48 такая же? Просто на готовой плате генератора нет, но есть отвод от 6МГц кварца, если умножить - получится 12... Сколько в этой схеме допустимый нижний предел?

Разобрал альтеровский оригинал - там 24 стоит Есть ограничение по тактовой "сверху". Мост USB имеет требования по длительности сигналов управления и пауз между ними. Схема полностью синхронная и можно тактировать с любой малой частотой. Я с кварца моста USB (6 мГц)заводил.

|

|

|

|

|

|

|

|

Jul 10 2009, 21:10 Jul 10 2009, 21:10

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

Цитата(AlexKooper @ Jul 10 2009, 09:57)  1. в разных источниках указаны разные кварцы, 24 - 48 - 60МГц. Чем определяется? Определяется тем, что имеем под рукой. Был генератор на 60МГц, поделил на 2 - схема не работает, поделил еще на 2 (15МГц) - работает, так и оставил.

|

|

|

|

|

|

|

|

Jul 13 2009, 09:30 Jul 13 2009, 09:30

|

Группа: Участник

Сообщений: 4

Регистрация: 18-10-05

Пользователь №: 9 771

|

ОК, схема с 6МГц заработала. Плата от misyachniy, прошивка от altera_usb_blaster.rar переработанная (переназначены пины и убран делитель на триггерах чтоб работало от 6МГц) epm3064atc100 читается/программируется. циклон 3 пока боюсь пробовать, слишком дорогая опытная плата  Прошивка от misyachniy не работала не знаю почему, симптомы совпадают с описанными на сайте http://misyachniy.embedders.org/usbblaster/usbblaster.html : "Quartus при вызове программатора стал долго думать." "Quartus 4.2 признал как родной и дает нажать клавишу программировать"

|

|

|

|

|

|

|

|

Aug 24 2009, 09:03 Aug 24 2009, 09:03

|

Участник

Группа: Свой

Сообщений: 70

Регистрация: 4-12-06

Из: Окно Петра в Европу

Пользователь №: 23 119

|

Цитата(_Anatoliy @ Aug 24 2009, 11:09)  А команду верификации он поддерживает? галка Verify тоже работает

|

|

|

|

|

|

|

|

Aug 30 2009, 06:49 Aug 30 2009, 06:49

|

Участник

Группа: Свой

Сообщений: 42

Регистрация: 18-07-06

Из: Germany

Пользователь №: 18 908

|

Цитата(_Anatoliy @ Aug 24 2009, 10:09)  А команду верификации он поддерживает? quartus usnajot OK a yesli Actel SVF v JAM to quartus_jli is mozhno Actel FPGA sachit  A3P060 - programmint time: 1 min 15 sek a swojei programmoi AT45DB161D pishu blank check: 3 sek read: 17 sek program/erase: 1 min 7 sek konecho ispolsavat actel chtob delat usb blaster  ah, AT45DB161 sachju dlja togo schtob s Silicon Blue FPGA rabotat ich rodnaja programma ni kak ne rabotaet Antti

Эскизы прикрепленных изображений

|

|

|

|

|

|

|

|

Oct 28 2010, 00:02 Oct 28 2010, 00:02

|

Участник

Группа: Участник

Сообщений: 34

Регистрация: 12-10-05

Из: Харьков

Пользователь №: 9 544

|

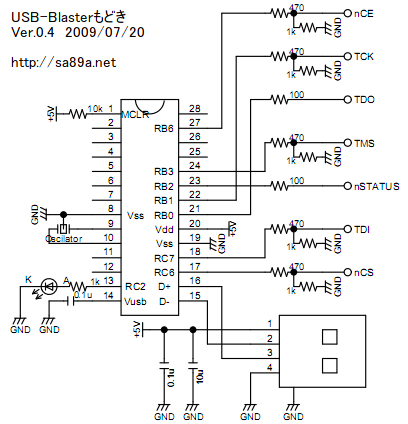

Нарыл на просторах инета ещё одну схемку altera usb blaster, на PIC18F2550 контроллере. Исходники и готовая прошивка для пика на сайте автора: http://sa89a.net/mp.cgi/ele/ub.htmВроде даже lattice умеет шить. Правда сайт на японском

|

|

|

|

|

|

2 чел. читают эту тему (гостей: 2, скрытых пользователей: 0)

Пользователей: 0

|

|

|