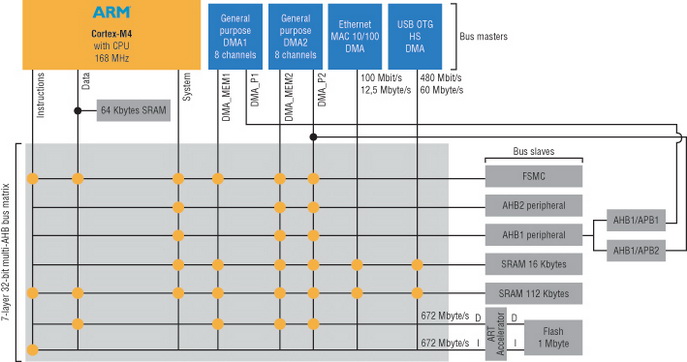

В кортексах для распараллеливания помогает матрица шин. Обратите внимание так же на разбиение SRAM на 2 и более блоков в современных MCU. Так же бывает память на ядре, так же код может крутиться в кэше большую часть времени (если кэш есть конечно). Если же и ДМА и процессор работают с одной шиной, то они ее делят, для STM32 в частности на сколько я помню по карусельному типу, конечно портят картину циклы переключения между мастерами, но есть такие примочки как burst передачи, когда гарантируется большая пропускная способность.

Поэтому не ленивые программисты смотрят сперва в reference manual и распределяют грамотно буферы и т п. Ну а все остальные программисты занимаются этим распределением когда не хватает ресурсов, я ближе ко вторым)))