| |

Передатчик CSI-2 на CycloneIII Передатчик CSI-2 на CycloneIII, Error: Pin "ХХХ" requires a pseudo-differential I/O assignment |

|

|

|

|

Apr 19 2018, 11:15 Apr 19 2018, 11:15

|

Группа: Участник

Сообщений: 12

Регистрация: 16-02-13

Из: Ленинградушка

Пользователь №: 75 653

|

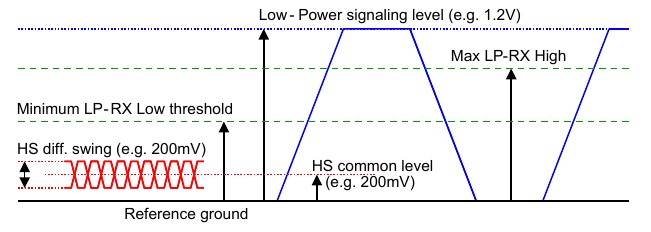

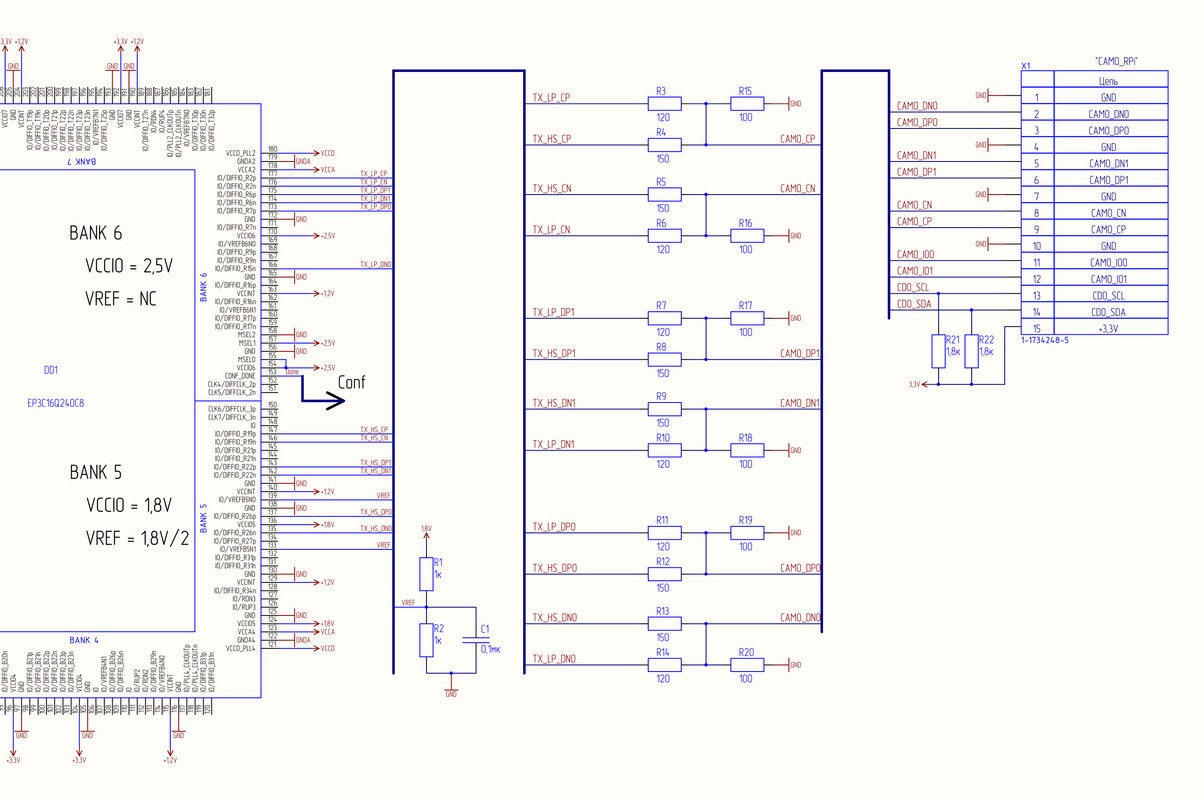

Добрый день. Пытаемся реализовать преобразователь HD-SDI видео в формат MIPI CSI-2. Схема проста: SDI проходит эквалайзер, реклокер и десериализотор, затем в виде 20-разрядного параллельного потока поступает в ПЛИС (EP3C16Q240C8), которая должна его должным образом обработать и в виде CSI-2 выдать наружу, чтобы затем подцепить Raspberry. Интерфейс CSI-2 оказался весьма непростым, его физический уровень представляет собой сочетание дифференциального тактового сигнала и от 1 до N двухуровневых дифференциальных пар, работающих в низкоскоростном служебном (LP, low power) и высокоскоростном (HS, high speed, для передачи данных) режимах:  Как реализовать такой режим подсмотрели в отладочной плате 10m50 eval board от той же Altera. С единственным отличием - там используется другое семейство ПЛИС, MAX10 (10M50DAF484C6GES). Нами были выбраны соответствующие диф пары и режимы работы выходных ног ПЛИС:  CODE set_location_assignment PIN_146 -to TX_HS_CN

set_location_assignment PIN_147 -to TX_HS_CP

set_location_assignment PIN_135 -to TX_HS_DN0

set_location_assignment PIN_142 -to TX_HS_DN1

set_location_assignment PIN_137 -to TX_HS_DP0

set_location_assignment PIN_143 -to TX_HS_DP1

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_CN

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_CP

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DN0

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DN1

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DP0

set_instance_assignment -name IO_STANDARD "1.8-V HSTL CLASS I" -to TX_HS_DP1 Таким образом на физическом уровне мы выдержали все рекомендации, которые удалось найти. Далее создали простой тестовый проект в Quartus9.1 для передатчика данных по SCI-2. На данном этапе нам необходимо убедиться, что выбранные нами порты ПЛИС поддерживают требуемые стандарты, и что фиттер всё сможет развести хотя бы в таком примитивном виде. Не хотелось бы попадать в ситуацию, когда печатные платы уже произведены, и только потом обнаружить, что развели их неправильно. Quartus выдал следующий варнинг: Error: Pin "TX_HS_CP" requires a pseudo-differential I/O assignment.

Error: Can't fit design in deviceВ Assignment Editor не удалось найти подходящий настроек, чтобы убрать данную ошибку. Да и не понятно откуда ей взяться, ведь всё повторили по примеру вышеуказанной эволюшен боард. Кто-нибудь сталкивался с подобным? Что можете посоветовать попробовать?

|

|

|

|

|

|

|

|

Ответов

|

|

Apr 24 2018, 07:55 Apr 24 2018, 07:55

|

Группа: Участник

Сообщений: 12

Регистрация: 16-02-13

Из: Ленинградушка

Пользователь №: 75 653

|

Получается так, что если убрать функцию ALTLVDS, то появляется возможность управлять выводами по отдельности (в стандарте 1.8-V HSTL Class I).

А с ней - не хочет хоть ты убейся.

Существует ли какой-нибудь ещё способ засерилизовать параллельный поток данных, чтоб несколько сот Мбит потянуло?

|

|

|

|

|

|

|

|

Apr 24 2018, 08:04 Apr 24 2018, 08:04

|

В поисках себя...

Группа: Свой

Сообщений: 729

Регистрация: 11-06-13

Из: Санкт-Петербург

Пользователь №: 77 140

|

Цитата(Max42 @ Apr 24 2018, 10:55)  Получается так, что если убрать функцию ALTLVDS, то появляется возможность управлять выводами по отдельности (в стандарте 1.8-V HSTL Class I).

А с ней - не хочет хоть ты убейся.

Существует ли какой-нибудь ещё способ засерилизовать параллельный поток данных, чтоб несколько сот Мбит потянуло? LVDS приемник я писал свой. Максимум по спецификации на чип вытягивал. Не думаю, что нельзя написать свой передатчик. P.S. Главное, чтобы выходы с DDR регистров можно было назначить на соответствующий стандарт.

|

|

|

|

|

|

Сообщений в этой теме

Max42 Передатчик CSI-2 на CycloneIII Apr 19 2018, 11:15 Max42 Передатчик CSI-2 на CycloneIII Apr 19 2018, 11:15  Realking https://www.altera.com/support/support-reso...0320... Apr 19 2018, 12:22 Realking https://www.altera.com/support/support-reso...0320... Apr 19 2018, 12:22   Max42 Цитата(Realking @ Apr 19 2018, 15:22) htt... Apr 19 2018, 12:37 Max42 Цитата(Realking @ Apr 19 2018, 15:22) htt... Apr 19 2018, 12:37    Realking Цитата(Max42 @ Apr 19 2018, 15:37) Написа... Apr 19 2018, 13:23 Realking Цитата(Max42 @ Apr 19 2018, 15:37) Написа... Apr 19 2018, 13:23     Max42 Цитата(Realking @ Apr 19 2018, 16:23) код... Apr 19 2018, 14:13 Max42 Цитата(Realking @ Apr 19 2018, 16:23) код... Apr 19 2018, 14:13      AVR Цитата(Max42 @ Apr 19 2018, 17:13) Кода н... Apr 19 2018, 14:23 AVR Цитата(Max42 @ Apr 19 2018, 17:13) Кода н... Apr 19 2018, 14:23       Max42 Цитата(AVR @ Apr 19 2018, 17:23) Зачем на... Apr 19 2018, 14:36 Max42 Цитата(AVR @ Apr 19 2018, 17:23) Зачем на... Apr 19 2018, 14:36        Realking Цитата(Max42 @ Apr 19 2018, 17:36) Буфер ... Apr 20 2018, 04:50 Realking Цитата(Max42 @ Apr 19 2018, 17:36) Буфер ... Apr 20 2018, 04:50      XVR Цитата(Max42 @ Apr 19 2018, 17:13) А как ... Apr 20 2018, 05:50 XVR Цитата(Max42 @ Apr 19 2018, 17:13) А как ... Apr 20 2018, 05:50       AVR Цитата(XVR @ Apr 20 2018, 08:50) Скачайте... Apr 22 2018, 13:51 AVR Цитата(XVR @ Apr 20 2018, 08:50) Скачайте... Apr 22 2018, 13:51       Max42 Цитата(XVR @ Apr 20 2018, 08:50) Скачайте... Apr 23 2018, 07:02 Max42 Цитата(XVR @ Apr 20 2018, 08:50) Скачайте... Apr 23 2018, 07:02  XVR Цитата(Max42 @ Apr 19 2018, 14:15) CODEse... Apr 19 2018, 13:51 XVR Цитата(Max42 @ Apr 19 2018, 14:15) CODEse... Apr 19 2018, 13:51  XVR Про дифференциальные HSTL можете забыть сразу:

Цит... Apr 23 2018, 14:23 XVR Про дифференциальные HSTL можете забыть сразу:

Цит... Apr 23 2018, 14:23   Max42 Цитата(XVR @ Apr 23 2018, 17:23) Про дифф... Apr 23 2018, 14:58 Max42 Цитата(XVR @ Apr 23 2018, 17:23) Про дифф... Apr 23 2018, 14:58       Flip-fl0p Цитата(AVR @ Apr 24 2018, 12:29) Ясно, по... Apr 24 2018, 09:40 Flip-fl0p Цитата(AVR @ Apr 24 2018, 12:29) Ясно, по... Apr 24 2018, 09:40

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|