| |

Непонятка с AD9272 Непонятка с AD9272, раздваивает биты |

|

|

|

|

Jun 4 2018, 06:04 Jun 4 2018, 06:04

|

Местный

Группа: Свой

Сообщений: 230

Регистрация: 2-06-05

Из: Днепропетровск

Пользователь №: 5 658

|

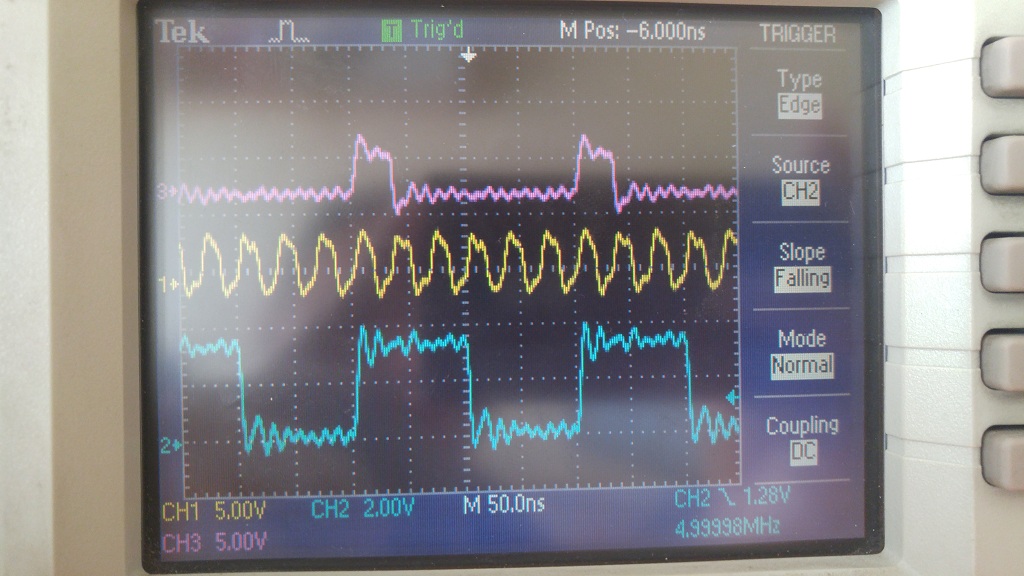

Всем привет. На ровном месте возникла непонятка с AD9272. Никогда с ней не работал. Сделал плату, подключил выходы к MAX10 по LVDS. Все тактируется , данные идут но когда начал разбирать, что же собственно идет, то выяснилось, что ВСЕ передаваемые биты удвоенны. Если включить тестовый режим ( в рег. 0x0d записать например 0х01) должно передаваться слово 0b100000000000, а в реальности передается 0b110000000000. Для всех остальных тестовых режимом то же самое. Сначала думал, что приемник LVDS выделывается... снизил частоту семплирования до минимума, что бы глянуть осциллографом, и таки да... передаваемый бит длиннее в два раз. Налазит и на фронт и на спад DCO. На картинке это видно. Розовое- битовый поток, желтый- DC и голубой- FC. Зависимости от частоты тактирования нет, принимаю одинаково что на 5МГц что на 50МГц. Все мысли, что были, закончились. Может кто либо сказать в чем дело?

|

|

|

|

|

|

|

|

Jun 4 2018, 08:53 Jun 4 2018, 08:53

|

Местный

Группа: Свой

Сообщений: 230

Регистрация: 2-06-05

Из: Днепропетровск

Пользователь №: 5 658

|

Цитата(MegaVolt @ Jun 4 2018, 11:32)  Не очень понятно как это удваивается. Кадровый клок то правильный. Значит если мы удвоим то половина данных не влезет.

Можете снять картинку для 1100 теста. И ещё парочку для ручного чтобы увидеть не один бит а хотя бы пару, патерны типа 01001... , 01101.., и пр... короче чтобы увидеть что отсекается и во что преобразовываются данные. Не очень удачно выразился... имеется ввиду что передается две единички подряд вместо одной. то есть вместо 100000000000 я вижу 110000000000 Более того, заметил еще одну странность, если в тестовым режиме передавать например 010000000000 то вообще передаются только нули. в общем, если единичка стоит в четной позиции, то передается как две единички, если в нечетной, то передаются нули... Четровщина какая то.

|

|

|

|

|

|

|

|

Jun 4 2018, 13:11 Jun 4 2018, 13:11

|

Местный

Группа: Свой

Сообщений: 230

Регистрация: 2-06-05

Из: Днепропетровск

Пользователь №: 5 658

|

Цитата(MegaVolt @ Jun 4 2018, 12:10)  Т.е. чётные биты передаются дважды а нечётные вообще не передаются... Такое ощущение что внутри микрухи не срабатывает что-то. Или какой то режим не довыбран. да, все выглядит именно так. В параметрах регистров которые описаны, ни чего похоэего нет. Все перерыл....мистика какая то. Отзовитесь, кто работал с ней....Требуется ли ей какая то специальная настройка отличная от дефолтной?

|

|

|

|

|

|

|

|

Jun 4 2018, 13:26 Jun 4 2018, 13:26

|

Местный

Группа: Свой

Сообщений: 230

Регистрация: 2-06-05

Из: Днепропетровск

Пользователь №: 5 658

|

Цитата(MegaVolt @ Jun 4 2018, 16:21)  Так а что форум от аналоговых девиц говорит? О таком эффекте ни слова. Сам еще не задавал вопрос. Поспрашиваю и там конечно.

|

|

|

|

|

|

|

|

Jun 4 2018, 15:43 Jun 4 2018, 15:43

|

Местный

Группа: Свой

Сообщений: 230

Регистрация: 2-06-05

Из: Днепропетровск

Пользователь №: 5 658

|

Цитата(_pv @ Jun 4 2018, 17:40)  длительность бита правильная, просто похоже данные захватываются по положительному фронту, а не по отрицательному, т.е. одновременно с тем как данные выставляет АЦП хм...так в этом ацп ddr , так что захват и по фронту и по по спаду. Вот как раз два бита и получаются.

|

|

|

|

|

|

|

|

Jun 5 2018, 10:58 Jun 5 2018, 10:58

|

Местный

Группа: Свой

Сообщений: 230

Регистрация: 2-06-05

Из: Днепропетровск

Пользователь №: 5 658

|

Цитата(_pv @ Jun 5 2018, 09:48)  да действительно,

там есть какой-то низкоскоростной режим, который что-то с pll делает, для работы на совсем низкой частоте. попробуйте его включить/выключить.

ну и другие паттерны чтобы убедиться что он действительно на вдвое меньшей частоте данные выдвигает и четные биты съедает. Что то не нашел я такого режима, просто написано, что ниже 10мгц не работает, на самом деле работает до 5ти мгц, ниже уже все срывается и тактирования нет. На картинке, как раз представлена работа на 5мгц. На 10ть тоже самое, выше уже осциллограф плохо видит. Но приемник lvds принимает одинаково два бита, так как видно на картинке, на любой частоте от 5ти до 50ти. И как я уже и писал эффект еще более странный, если бит стоит в четной позиции, то передается два раза, если в нечетной то вообще нет ни чего. Судя по всему на работает стробирование по спаду DC. P.S/ Пардон, есть такой режим, но суть передачи от этого не меняется, просто разрешается работа на еще более низкой тактовой.

|

|

|

|

|

|

|

|

Jun 5 2018, 11:21 Jun 5 2018, 11:21

|

Местный

Группа: Свой

Сообщений: 230

Регистрация: 2-06-05

Из: Днепропетровск

Пользователь №: 5 658

|

Цитата(_pv @ Jun 5 2018, 14:11)  reg 21 Serial_control

Bit3 <10 MSPS,low encode rate mode

ну и разрядность тоже можно поменять в том же регистре и посмотреть какие тогда биты теряться будут. Да, я уже нашел это. Разрядность менял еще в самых первых экспериментах. Биты "теряются" точно по тому же самому закону. Чертовщина какая то...

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|