Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ KiCAD _ KiCad и High-Speed Design

Автор: dxp Apr 13 2017, 11:38

Всем привет!

Интересует вопрос: насколько реально в KiCad выполнять высокоскоростные платы - с DDR2/DDR3, гигабитными сериальными линками и т.п.? Прошу поделиться опытом - какие платы (из вышеперечисленных и вообще на эту тему) сделаны, какие проблемы и неудобства возникали?

В редакторе плат KiCad имеется возможность выравнивать длины дорожек "змейками". Пара вопросов на эту тему:

- длина задаётся, насколько знаю, в mil, а по-хорошему надо бы учитывать времена, т.е. не физическую длину, но электрическую. Как этот момент обходится? Или сугубо вручную?

- в сложных микросхемах типа быстрых процессоров и ПЛИС указываются задержки сигналов от точек на кристалле до выводов микросхемы. Имеется ли возможность это как-то учитывать в программе?

Ну, и последнее: существуют ли какие-либо пути экспортировать дизайн во внешние программы для анализа целостности сигналов, питаний - например, Hyperlynx?

Автор: jorikdima Apr 13 2017, 15:36

Тоже тема интересна.

Сам разве что могу удивиться даже отсутствию возможности делать проводники арками. Ну то есть не 45/90 градусов. Это правда для RF более важно, а не HiSpeed. Может его допилят лет через 5..... этот КиКад

Автор: Сергей Борщ Apr 13 2017, 17:36

Автор: break Apr 14 2017, 07:08

dxp

Я при разводке DVI И LVDS просто, по возможности, выравнивал длины проводников, как между дифлиниями, так и между проводниками в каждой дифпаре. Частоты, конечно, ниже, чем в DDR. "Змейки" оказались бесполезны, так как гнутся непредсказуемым образом, я про это уже писал.

И длина линий у меня в миллиметрах, а не милах. ![]()

Расчёт дифпар оказался удобнее в TXLine, чем во встроенном PCB-калькуляторе.

Автор: dxp Apr 14 2017, 07:50

И длина линий у меня в миллиметрах, а не милах.

Расчёт дифпар оказался удобнее в TXLine, чем во встроенном PCB-калькуляторе.

Спасибо за ответ!

Про длины - без разницы, в милах или мм, я имел в виду то, что скорость распространения сигнала сильно зависит от того, где проходит проводник: насколько помню, скорость распространения на внутренних и внешних слоях отличается чуть ли не раза в полтора.

Автор: faa Apr 14 2017, 10:01

Реально.

QDR-II, DDR3, MGT - уже не один проект сделан.

Если конкретные вопросы есть, то готов поотвечать.

[*]длина задаётся, насколько знаю, в mil, а по-хорошему надо бы учитывать времена, т.е. не физическую длину, но электрическую. Как этот момент обходится? Или сугубо вручную?

А какая разница - длина задана или время, все туда-сюда пересчитывается на раз?

Время распространения завсит от материала платы и качества (однородности) этого материала.

А если очень высокоскоростные или СВЧ, то и от качества материала проводника (скин-эффект и пр.), финишного покрытия (с никелем на СВЧ беда) и т.п.

Раньше (когда не было этой фичи с выравниванием) приходилось ровнять в полуручном режиме с помощью макросов. Для этого они (макросы) и были прикручены.

http://electronix.ru/redirect.php?https://www.youtube.com/watch?v=wbV77alUv_s, где я рассказывал про фишки KiCad (в т.ч и макросы) на конференции в Бауманке (еще в 2012 году).

Теперь выравнивает, почти красиво.

А макросы успешно в продакшене выпилены, остались только в ГОСТ-ветке.

Есть такое. Прикручено уже давно (2009-2010 год). Учитывается длина проводника в чипе, задается в посадочном месте..

С этим пока проблемы. Но разговоры были.

Хотя, (ИМХО), модельку в HL накидать можно и без выгрузки.

Ну и практический опыт тут тоже сильно помогает.

Автор: dxp Apr 14 2017, 12:57

QDR-II, DDR3, MGT - уже не один проект сделан.

Это радует.

Спасибо, буду иметь в виду.

Время распространения завсит от материала платы и качества (однородности) этого материала.

Ну, если есть переходы, например, с внешнего слоя на внутренние, т.е. часть пути сигналов идёт в одних условиях, а часть в других, то тут может поджидать засада - например, байт-лейн ведёте, один разряд "нырнул" на внутренний слой сразу, а другой немного дальше, из-за этого возникнет "разбег" по времени даже если физическую длину выровнять идеально.

Кстати, время распространения как оцениваете? В каком-то калькуляторе считаете?

http://electronix.ru/redirect.php?https://www.youtube.com/watch?v=wbV77alUv_s, где я рассказывал про фишки KiCad (в т.ч и макросы) на конференции в Бауманке (еще в 2012 году).

Теперь выравнивает, почти красиво.

А макросы успешно в продакшене выпилены, остались только в ГОСТ-ветке.

Да, это видео смотрел (даже два раза). А раз есть возможность рисовать "змейки", то насколько актуальны макросы (тоже не понимаю, зачем было убирать, если было и работало)?

Хотя, (ИМХО), модельку в HL накидать можно и без выгрузки.

Ну и практический опыт тут тоже сильно помогает.

А нельзя ли как-то ручном режиме, например, топологии слоёв экспортировать и импортировать в другую САПР, из которой есть экспорт в HL?

Автор: _Sergey_ Apr 14 2017, 13:04

Многовато, имхо, требований к бесплатной альтернативе.

Тоже думал над трансляцией в другие САПР. Как вариант, через гербера..

Автор: dxp Apr 14 2017, 14:30

Бесплатный, не значит, хуже. Вон gcc даст сто очков вперёд некоторым коммерческим.

Ну, и вот faa на практике доказывает. Правда, он эксперт в этой САПР.

Ну, и, собственно, это не требования, а вопросы к опытным кикадовцам.

Да, через гербера - вариант. Я подумывал, может через svg экспортировать, а в там вставлять. Но пока плотно не прорабатывал.

Автор: faa Apr 17 2017, 06:35

Условия надо "выравнивать", особенно для скоростных параллельных шин (например, байты в DDR3-DDR4, слова в QDR и т.п.).

MGT линии - это отдельная песня, тут "клаву" можно долго топтать.

А в общем примерно так:

"ныряем" сразу у пада;

переходов минимум и одинаково;

опорные слои правильно распределяем;

следим за неоднородностями, при острой необходимости "обратная сверловка" или глухие отверстия.

Но это уже теория и практика HD и HS дизайна.

Все прекрасно понимают, что идеальности в мире нет.

Поэтому везде есть допуски.

Для выравнивания в современных ПЛИС у каждой ноги ввода-вывода есть

линии задержки с неплохим разрешением как на ввод, так и на вывод.

Ну и принцип разумной необходимости и достаточности никто не отменял.

Для каждого материала ПП есть эти данные, смотреть в даташитах производителей.

В кикаде есть калькулятор.

Из бесплатных неплох сатурнПСБ.

Автор: dxp Apr 17 2017, 10:33

"ныряем" сразу у пада;

переходов минимум и одинаково;

опорные слои правильно распределяем;

Спасибо, примерно так и полагал, вы подтвердили.

Из бесплатных неплох сатурнПСБ.

А сатурн с под линукса пускали? У меня из-под wine что-то не захотел.

Автор: faa Apr 17 2017, 10:51

Под древней виндой в виртуалке.

Под вайном должен, но нужен вайн свежий.

У меня в дистре стоит 1.7.3 - под ним не едет, требует shcore.dll, а заморачиваться с этим нет желания.

Автор: mobidev Apr 25 2017, 20:06

Stubs & AcidTraps teardrop drc

http://electronix.ru/redirect.php?http://www.youtube.com/watch?v=uSUWkbdA2zM

Автор: Bender Jul 20 2017, 09:22

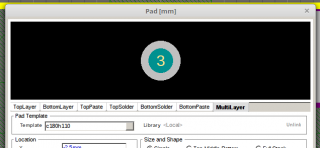

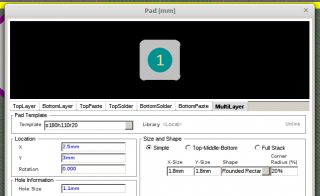

Коллеги, подскажите как в Кикаде сделать так, чтобы ширина поясков в КП на разных слоях меди была разного размера?

Хочется чтобы поясок был минимального размера, или вообще не было на том слое, где нет подключения к КП.

Или я хочу странного?

Автор: Сергей Борщ Jul 20 2017, 12:07

Такие странности в кикаде реализуются наложением друг на друга нескольких более простых КП с одинаковым номером. Увы.

Автор: op3op3 Jul 21 2017, 01:27

В альтиуме последних версий появилась возможность брать пады из библиотеки. Мне показалось это очень удобным и вижу два применения для этого: когда требуется какой-то прям особый пад прорисовать и когда нужно идентичные пады на плате привести к одному виду. То есть, библиотека падов должна быть доступна как для библиотеки модулей, так и для платы.

у альтиума удачно продумано формирование имени пада s180h110r20 квадратный 1,8, отверстие 1.1, скругление 20%

Хотелось бы библиотеку падов видеть в KiCAD-е с удобными инструментами использования, редактирования и применения )

Автор: break Aug 1 2017, 10:02

op3op3

В OrCAD Layout это было уже давно.

Русская версия Invision Power Board (http://www.invisionboard.com)

© Invision Power Services (http://www.invisionpower.com)