Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Altium Designer, DXP, Protel _ 2018 Вопросы начинающих

Автор: Sanchosd Jan 29 2018, 08:18

http://electronix.ru/redirect.php?https://blogs.mentor.com/tom-hausherr/blog/2010/09/22/pcb-design-perfection-starts-in-the-cad-library-part-2/

Там ЕМНИП 19 частей - очень хорошо изложена логика выбора сетки для размера площадок и их шага. И всей геометрии компонента.

Спасибо! Сейчас погляжу, что там такое!

ЗЫ: может пора ветку "Вопросы 2018 открывать", а то уже 94-я этой темы.

Пардон, если не в свое дело лезу)

Автор: Gluk Jan 29 2018, 10:28

Цвета в редакторе плат, тьфу блин!

Такое дело - настраиваем цвета и сетку на плате как-то (или оставляем по-умолчанию). Открываем чужой файл, при рисовании которого сетка была точками, а не линиями и цвет сетки какой-то угарный. Эти цвета сохраняются! Переходим в свой файл и цвет сетки и платы переключается на цвет из чужой платы! Это как-то лечится или страдать вечно? 16.1

Автор: Димон Безпарольный Jan 29 2018, 18:20

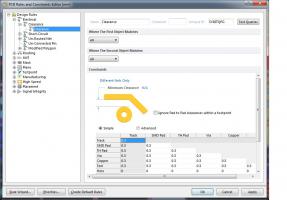

Как создать правило, чтобы на зазоры Board Outline Clearence не проверялись слои шелкографии?

Автор: Lehin_05 Jan 30 2018, 06:21

прописать в правиле BoardOutlineClearance: All Xor OnSilkscreen.

Тогда правило будет проверять все, кроме шелкографии.

Автор: Димон Безпарольный Jan 30 2018, 20:12

Тогда правило будет проверять все, кроме шелкографии.

Или так:

http://electronix.ru/redirect.php?https://postimages.org/

Автор: Димон Безпарольный Jan 31 2018, 17:43

Как правильно задавать области запрета прокладки дорожек у элементов в PCB библиотеки?

Автор: Владимир Jan 31 2018, 18:54

Объекты на слое KeepOut (Для всех слоев)

Объекты на слое со свойством KeepOut (Для данного слоя)

В последних версиях запреты настраиваются отдельно для Track И т.п.

Автор: Master_MW Feb 1 2018, 07:40

Доброго времени суток! Вопрос скорее всего в эту ветку.

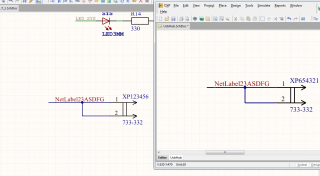

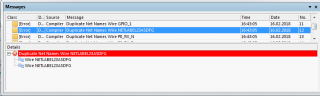

Суть проблемы в следующем: Открываю один из старых проектов (AD17) где нужно внести изменения , компилирую.

При компиляции выдает ошибку "Dublicate Net Names Wire _имя цепи_"

Имя цепи указано при помощи Net Label. Так, например Net Label CAN_H , стоит на двух листах (на разъеме и драйвере) . И ругается. Полная перерисовка не помогает. В чем может быть дело?

Автор: Владимир Feb 1 2018, 08:11

1 Ищите лишний пробел или написание СА рсскими(английскими). А проще Сопи пасте Netlabel

2 Если не помогает -- В настройках проекта ищите (скорее всего у вас все Global)

если иерархия -- там надо смотреть внимательней

Автор: Sanchosd Feb 1 2018, 08:23

Друзья, скажите. а кто-то использует SolidWorks Modeller для Альтия?

Если да, то где можно почитать как им пользоваться?

Автор: Master_MW Feb 1 2018, 08:26

Копипастинг не помогает. Неты все названы на английской раскладке и проблемы со всеми нет лейблами одной цепи, но расположенными на различных листах. Названия нет лейблов 100 процентов одинаковые на английской раскладке без пробелов

Может подскажете, что именно надо рыть в настройках?

Автор: Владимир Feb 1 2018, 11:03

Значит на линии взвимосвязи присутсвуют разноименные Netlabel

Ищите.

Автор: peshkoff Feb 1 2018, 12:34

Суть проблемы в следующем: Открываю один из старых проектов (AD17) где нужно внести изменения , компилирую.

При компиляции выдает ошибку "Dublicate Net Names Wire _имя цепи_"

Имя цепи указано при помощи Net Label. Так, например Net Label CAN_H , стоит на двух листах (на разъеме и драйвере) . И ругается. Полная перерисовка не помогает. В чем может быть дело?

зависит от типа проекта (иерархия/плоский и т.д.)

у вас есть порты на схеме?

Автор: Master_MW Feb 1 2018, 13:37

Ищите.

Да осмотрел все. Разноименности нет. Лан, буду копать, если выясню причину, отпишусь здесь.

у вас есть порты на схеме?

Портов на схеме нет. А как посмотреть какой именно тип проекта? Или это определяется только наличием на схеме sheet entry, sheet symbol и портов?

P.S. Поправка:

Косяк нашел на одном из 8-ми листов схемы закрался порт вне рабочей зоны листа схемы выкуривал через навигатор, из-за замылившихся глаз не сразу заметил. Отсюда и всплывали проблемы. Спасибо за помощь

Автор: peshkoff Feb 2 2018, 06:33

Портов на схеме нет. А как посмотреть какой именно тип проекта? Или это определяется только наличием на схеме sheet entry, sheet symbol и портов?

P.S. Поправка:

Косяк нашел на одном из 8-ми листов схемы закрался порт вне рабочей зоны листа схемы выкуривал через навигатор, из-за замылившихся глаз не сразу заметил. Отсюда и всплывали проблемы. Спасибо за помощь

Тип проекта настраивается в свойствах проекта Project\Options\Options

Если сами ничего не правили, то у вас, скорее всего, стоит автоматик

тогда альтиум считает, что проект плоский - флат, если нет портов.

если порты есть, то иерархия. в этом случае он цепи соединяет через порты и одинаковые нетлейблы на разных листах считаются разными цепями , если не соединены портами.

Автор: filmi Feb 2 2018, 06:44

Такое дело - настраиваем цвета и сетку на плате как-то (или оставляем по-умолчанию). Открываем чужой файл, при рисовании которого сетка была точками, а не линиями и цвет сетки какой-то угарный. Эти цвета сохраняются! Переходим в свой файл и цвет сетки и платы переключается на цвет из чужой платы! Это как-то лечится или страдать вечно? 16.1

Это наблюдается на всех релизах Альтиума. Ужас как бесит!

Автор: Hupyter Feb 2 2018, 07:21

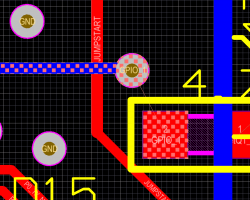

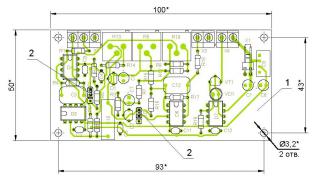

Развел вот платку

http://electronix.ru/redirect.php?https://postimages.org/

Тут по центру 2 крепежных отверстия диаметром 3.2 мм (не металлизированные).

Сделал гербер-файлы, и вот файл GTL (Top Layer) имеет такой вид:

http://electronix.ru/redirect.php?https://postimages.org/

И тут я че то засомневался, это вообще правильно? Слой Top Layer он ведь только для проводников, или нет?

Отверстия делал с помощью Place>Pad. Там в свойствах ставил диаметр 3.2, а еще в Size and Shape (размеры и форма) тоже 3.2мм

Автор: Владимир Feb 2 2018, 07:38

А зачем? Все что там указана-- это для меди. Понятно, что ее там не будет, так как там все высверливаться будет. Но чтоб даже мыслей не было-- делайте нулевыми. В любом случае меньше чем диаметр высверливания с учетом допуска

Автор: peshkoff Feb 2 2018, 07:42

Вот этот шейп и нарисован.

если вас он смущает, выставить в 0.

(но я бы здесь сделал метализированное отверстие с площадкой)

Автор: Hupyter Feb 2 2018, 08:16

если вас он смущает, выставить в 0.

(но я бы здесь сделал метализированное отверстие с площадкой)

А как это сделать? Я за AD сел 3 дня назад

Указать Hole 3.2mm, а Size and Shape 5.2mm? И на каком слое делать?

Автор: Владимир Feb 2 2018, 09:08

Автор: FFF Feb 2 2018, 12:51

Помогите. Как добавить составной компонент в DBlib (через excel файл) ?

P.S. Раньше пользовался интегрированными библиотеками, но что-то они у меня стали вылетать при добавении нового компонента. Создал DBlib через файл excel - все работает, только не могу составной компонент прописать.

Автор: Владимир Feb 2 2018, 13:11

Осталось понять, что имеется ввиду под составным компонетом

Автор: FFF Feb 2 2018, 13:19

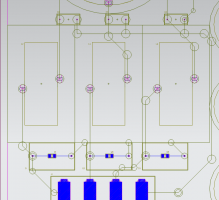

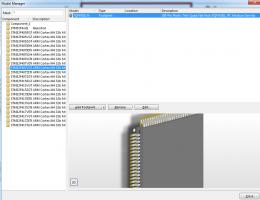

Это я вот про такую штуку :

http://electronix.ru/redirect.php?https://postimages.org/

Автор: musa Feb 2 2018, 13:34

Это как вы умудряетесь что то добавлять в интегрированную библиотеку. Они не для этого. И зачем вам это нужно

Автор: Владимир Feb 2 2018, 13:57

http://electronix.ru/redirect.php?https://postimages.org/

Причем здесь база.

Это в УГО создается.

К базе не имеет никакого отношения

Автор: FFF Feb 2 2018, 14:22

Это в УГО создается.

К базе не имеет никакого отношения

Все создано. Хочу сделать из sch и pcb Database library посредством excel файла.

Автор: Владимир Feb 2 2018, 14:24

Зачем?

в чем смысл?

Просто хочется?

Автор: FFF Feb 2 2018, 14:28

в чем смысл?

Просто хочется?

Удобно.

Автор: peshkoff Feb 2 2018, 15:05

это примерно 4 поколения назад.

xls->mdb->svndblib->vault->nexus

Выберите хотя бы .mdb

На екселе встрянете (большие объемы не переваривает)

Автор: Sanchosd Feb 2 2018, 15:26

P.S. Раньше пользовался интегрированными библиотеками, но что-то они у меня стали вылетать при добавении нового компонента. Создал DBlib через файл excel - все работает, только не могу составной компонент прописать.

мне кажется я знаю с чем вы столкнулись.

При "вытягивании" на Sch многоблочного компонента из библиотеки в виде базы данных(XLS или Accb), вы, в иблиотеке. в списке компонентов, видите только первую часть компонента. Вернее видите его описание, и УГО первой части.

Тащите на схему компонент(пускай это будет логическая МС из 4-х частей). У вас вытаскивается part 1. Дальше, зажимаете Shift, и тащите компонент в сторону. Только вместо компонента вылезет его вторая часть.

Не знаю. может где-то это прописано, но естественным путем хрен догадаешься.

Автор: Владимир Feb 2 2018, 15:27

Абсолютно никаких удобств применительно к одному проекту.

Удобства появляются в Vault (базе) создаваемых на предприятии, и не привязанных к проекту.

Автор: FFF Feb 2 2018, 17:14

При "вытягивании" на Sch многоблочного компонента из библиотеки в виде базы данных(XLS или Accb), вы, в иблиотеке. в списке компонентов, видите только первую часть компонента. Вернее видите его описание, и УГО первой части.

Тащите на схему компонент(пускай это будет логическая МС из 4-х частей). У вас вытаскивается part 1. Дальше, зажимаете Shift, и тащите компонент в сторону. Только вместо компонента вылезет его вторая часть.

Не знаю. может где-то это прописано, но естественным путем хрен догадаешься.

Спасибо, все получилось ! Ни в жизнь бы не догадался так сделать.

Автор: Владимир Feb 2 2018, 17:34

Чего там догадываться.

Заходим в свойства и меняем на нужный PART

Автор: FFF Feb 2 2018, 17:41

Заходим в свойства и меняем на нужный PART

Все гениальное просто. Спасибо, тоже работает. Только надо снять галку Locked.

Автор: Dmitry Dubrovenko Feb 3 2018, 10:50

А разве она должна быть установлена "по умолчанию"?

Автор: Владимир Feb 3 2018, 10:55

Обычно да.

В библиотеках, для Part которым разрешен Swap-- можно (нужно) снять.

Но на схемах, для избежания перетасовки при перенумерации лучше поставить, когда схема уже сделана

Автор: Sanchosd Feb 6 2018, 09:52

Друзья, я дико извиняюсь за занудливость, но может кто-то использует связку AD и SolidWorks посредством CircuitWorks.

Вопрос: при импорте в CircuitWorks, модели компонентов не передаются, и CircuitWorks вытягивает "кирпичи" вместо отображения нормальных моделей.

ЧЯДНТ?

Заранее спасибО!

Автор: Gluk Feb 6 2018, 10:23

Sanchosd, оно так и работает.

Для подключения нормальных моделей делается библиотека моделей в солиде и подключается к СёркитВорксу. Сам CW не перетаскивает модели из степов на плате.

Автор: Sanchosd Feb 6 2018, 17:48

Для подключения нормальных моделей делается библиотека моделей в солиде и подключается к СёркитВорксу. Сам CW не перетаскивает модели из степов на плате.

Обоже как-же это неудобно...но таки выход, да!!!

Спасибо за подсказку!

А Вы, каким путем перетаскиваете в мех.кад?

Автор: peshkoff Feb 7 2018, 05:51

Спасибо за подсказку!

А Вы, каким путем перетаскиваете в мех.кад?

что значит неудобно? это принцип CW.

Для него входящие данные - IDF, в нем нет 3Д, а только координаты компонентов.

По этим координатам он подставляет модели, что уже есть в SW.

Если у вас все есть, сохраните степ из альтиума, его и открывайте.

Автор: Gluk Feb 7 2018, 06:20

Так и перетаскиваем. В IDF координаты и прямоугольники компонентов. Если моделей нет, то он вытягивает из этих прямоугольников.

Со степом есть проблемы, например при округлении чисел в платах сложной формы, контур разваливается в Солиде.

Автор: Sanchosd Feb 7 2018, 09:16

Что-то изменил в плате, генеришь STEP, идешь в SW, открываешь STEP, распознаешь его, сохраняешь в виде Part. Открываешь сборку, получаешь окно с матюком, мол "файл тот, но не тот, использовать?". Говоришь- использовать. И бабах, вс привязки слетают. Приходится снова заходить в привязки и все их редактировать.

Что-то изменил в плате, генеришь STEP....

Но в цело я понял с CW, спасибо!

Еще такой вопрос, джентельмены.

Кто-то замечал, что при перетаскивании VIA, с подключенными трэками, АД отилично тягает за VIA трэки(вот если-бы он еще так и за компонентами их тягал, сохраняя углы 45 и 90гр.), но, бывает хочешь подвинуть VIA на 0,1, или 2 по 0,1. двигаешь, а VIA ну никак не хочет попадать куда ты ее пытаешься посадить. Прыгает все время в соседнее пересечене сетки. Сетка у меня всегда 0,1, привязка- 1шаг сетки. И в результате. если нужно передвинуть на 0,1, или 0,2, проще передвинуть отдельно VIA с зажатым Ctrl, а потом трэки подвести.

Это у меня руки кривые, или присутствует такая фича?

Автор: Spartak Feb 7 2018, 12:01

Что-то изменил в плате, генеришь STEP....

Но в цело я понял с CW, спасибо!

Еще такой вопрос, джентельмены.

Кто-то замечал, что при перетаскивании VIA, с подключенными трэками, АД отилично тягает за VIA трэки(вот если-бы он еще так и за компонентами их тягал, сохраняя углы 45 и 90гр.), но, бывает хочешь подвинуть VIA на 0,1, или 2 по 0,1. двигаешь, а VIA ну никак не хочет попадать куда ты ее пытаешься посадить. Прыгает все время в соседнее пересечене сетки. Сетка у меня всегда 0,1, привязка- 1шаг сетки. И в результате. если нужно передвинуть на 0,1, или 0,2, проще передвинуть отдельно VIA с зажатым Ctrl, а потом трэки подвести.

Это у меня руки кривые, или присутствует такая фича?

Генерите 3D в PARASOLID, результаты заметно лучше, чем при использовании STEP.

Автор: musa Feb 7 2018, 12:29

А если есть то как подцепить их к солиду и объяснить что чему соответствуют. Компоненты всеравно преимущественно в солиде рисуются так что как правило есть и то и другое.

Автор: Sanchosd Feb 7 2018, 14:26

Ща протестим! Спасибо тебе добр. человек!

Автор: RadiatoR Feb 9 2018, 06:20

Доброго всем дня!

Имеется компонент lm258, состоящий из 3 частей:

Составил схему:

При Tools -> Annotate -> Quietly у меня части компонента меняются местами:

Что за напасть? Как можно исправить?

Заранее спасибо

Автор: Владимир Feb 9 2018, 06:28

для не взаимно заменяемых Part следует установить флаг Lock Part

а еще лучше-- для всех

Автор: RadiatoR Feb 9 2018, 07:58

Это уже в самом листе схемы? Или есть настройка в самом компоненте?

Залочил на схеме. Все стало ок.

Спасибо!

Автор: Владимир Feb 9 2018, 08:35

В компоненте. (с моей точки зрения это правильно)

Но можно и в настройках аннотации

Автор: peshkoff Feb 9 2018, 09:16

Да... Это ж фишка альтиума! только в альтиуме гейты переименовываются в зависимости от положения.

Ноу хау так сказать...

Автор: vGera Feb 9 2018, 12:53

Или клиренс только для объектов OnCopper

Автор: Sanchosd Feb 9 2018, 13:15

Наткнулся на такой момент в 18-м.

Проект с Variants.

Для исполнения Х делаю замену компонента с номиналом 123 на компонент с номиналом 321, компилирую. Перехожу во вкладку скомпилированную, номинал поменялся, как и положено.

Но, у меня настроено, чтоб "подменные" компоненты, а точнее их номинал- красным цветом писались.

Во всех альтиях до 18-го все работало, а в 18-м цвет не меняется.

Специально проверил, настройка установлена "Modify Text and Font", выбран красный цвет.

Если компонент не ставится- у меня ставится красный крест. С этим все в порядке.

ЗЫ: запустил портабельный 17-й АД, для проверки. - все работает как и положено, подменный номинал прописан красным цветом.

Автор: vGera Feb 9 2018, 14:47

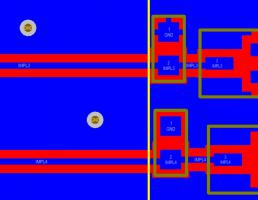

Вопрос от не совсем начинающего.

В AD 16 и ранее для удаления заливки полигона изо всех позитивных слоев было достаточно разместить cutout на слое keep-ot layer. Там же было логично рисовать и контур ПП, хотя в 16-й версии уже было правило board outline clearance и контур по сути был нужен для выгрузки в Герберы.

В AD17 разместить что-то руками на слое keep-out layer низзя. Можно place--keep-out--arc/fill/итд. И если в свойствах размещаемого сказано, что оно влияет на все сигнальные слои, объект сам прыгает на слой keep-out layer с доп. настройками на объекты какого типа он влияет. Лично я считаю это улучшайзингом там, где не надо (ну найти работу программистам и манагерам).

Фабула: разместить на слое keep-out layer объект Polygon Pour Cutout низзя. В его свойствах нет галок, на какие слои он работает. Итого... Что, теперь НЕЛЬЗЯ одним катаутом убрать заливку полигонов сразу изо всех слоев? Типичный пример зачем это надо - убрать заливку полигона в углу ПП, чтобы было так, как слева, а стало так, как справа?

Пока нашел решение только оградить места, откуда убирается полигон, линиями keep-out, которые влияют на все слои, примерно так:

Было красимше, ибо у polygon cutout линии не имеют толщины и ты просто рисовал, откуда выкинуть заливку.

Океееейййй... А теперь я хочу убрать полигоны всех слоев из места, куда входят и где идут дороги радиоканала какого-нибудь гигагерцового. Как рекомендуют всякие Тексасы. Линию как на рисунке сигнальная дорога пересечь не сможет. То есть придется копировать одинаковые кипауты на 2-4 слоя.

Автор: Владимир Feb 9 2018, 15:42

Противоречит этому

А еще что кроме этого нужно?

Специально открыл и разместил. Хотя я этот слой не использую для очистки полигонов на всех слоях

Можно. как и раньше. Расположите на Multi-layer

Автор: vGera Feb 9 2018, 16:30

Я имел ввиду, что нельзя указать напрямую, что я хочу поместить геометрический примитив на слое keep-out. Можно использовать отдельную команду размещения keep-out'а, и ЕСЛИ он действует на все слои, он САМ переносится системой на слой keep-out layer.

Окно свойств катаута (открыл табом при размещении катаута):

В инспекторе объектов - то же самое. Если открыть плату, где на слое уже лежит положенный туда руками катаут, слой есть в списке. Но создать новый такой же объект нельзя...

А вот за этот совет спасибо, помогает. Я как-то раньше для этого keep-out слой использовал.

Выходит так, как на очередной моей видеозарисовке (у меня рука набита такие делать по ряду причин, так что не удивляйтесь, я быстро их делаю):

Свойства объекта программы зависят от того, в какой версии программы в данном файле был создан этот объект. Если катаут сделан в AD16, в его свойствах есть возможность указать слой кип-аут (вернее, он уже указан), а если в AD17, для нового объекта - то уже нет. Старые можно копировать, слой сохраняется. Продолжаю изучать нюансы (хорошо что сейчас все проекты доделаны и время есть

Автор: Владимир Feb 9 2018, 17:46

Что-то длинным путем идете

Place/Polygon Pour CutOut

Между 16 и 17 изменили подход к KeepOut на других слоях.

Теперь это отдельный тип объектов

Place/KeepOut/...

Автор: vGera Feb 9 2018, 18:20

Я таким путем и иду, на клавиатуре p, cutout, жму tab и смотрю окно свойств размещаемого объекта.

В AD вообще самый короткий путь - через клавиатуру. T, g, a - перезалил полигоны и т.д. ![]()

Автор: Владимир Feb 9 2018, 19:11

С коротким никто не спорит.

Он только сложен для объяснения тем, кто не знает, не слышал, не использует, забыл.

Указание через выбор команд просто адекватен с точки зрения поиска команды на неизвестном поле.

Автор: Smen Feb 10 2018, 05:59

А вот подскажите, есть ли какой способ, при трассировки одной цепи, но двумя параллельными дорожками, контролировать зазор (т.е. создать правило) между этими дорожками?

Автор: juvf Feb 10 2018, 06:52

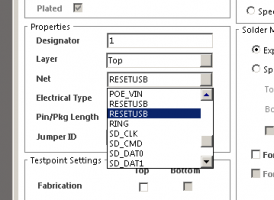

На разных листах схемы обозначил одну и туже цепь меткой ResetUsb, на PCB эти цепи разные. В свойствах КТ можно указать руками нужную ыеп, но там почему то две цепи с именем ResetUsb

Почему AD Сделал две разные цепи с одинаковым именем? Как их объединить?

Автор: Владимир Feb 10 2018, 08:14

Почему AD Сделал две разные цепи с одинаковым именем? Как их объединить?

проверяете все буквы и надчеркивания и пробелы

Зрительно могут совпадать -- реально нет

Автор: juvf Feb 10 2018, 08:39

Проверил на 100 раз. Более того.... Метку скопировал с одного листа, вставил в другой лист. в схемном редакторе можно цепи(порту) назначить имя выбрав из списка. в списке одно имя ResetUsb. В PCB редакторе в списке два имени.

ps Проект изночально сделан в Eagle. Потом встроенным в АД экспортером экспортирован в АД. Потом в АД добавил новый лист с схемой. Так вот в этом новом листе назначаю имена цепям как вол всем проекте.... часть цепей в PCB дублируется и не объеденяется. Такое чувство, как будь-то есть какойто класс цепей. И с одного листа схемы цепь входит в класс (пространство имён) (EAGLE->USBRESET), с ногово листа не входит в этот класс.

Автор: vGera Feb 10 2018, 08:46

Есть. Сделайте из одной - две цепи при помощи NetTie с двух сторон (если речь идёт о цепи с 2 узлами) и объедините их в дифференциальную пару директивой Differential Pair. Цепи должны иметь имя в виде одинаковой сроки, у одной в конце _N, у второй _P. Ну а потом правило для этой пары какое хотите.

Какой-то Кельвин коннекшен делаете?

Может быть, глюки с Net scope... Project options - Net identifier scope (как-то так, я по памяти) - Global место auto (based on project contents).

Автор: Владимир Feb 10 2018, 10:09

ps Проект изночально сделан в Eagle. Потом встроенным в АД экспортером экспортирован в АД. Потом в АД добавил новый лист с схемой. Так вот в этом новом листе назначаю имена цепям как вол всем проекте.... часть цепей в PCB дублируется и не объеденяется. Такое чувство, как будь-то есть какойто класс цепей. И с одного листа схемы цепь входит в класс (пространство имён) (EAGLE->USBRESET), с ногово листа не входит в этот класс.

Проверите настройки проекта:

иерархия

Назначение индивидуальных цепей на листе

Связи межлистовые.

Хотя скорее всего у вас можно все Global объявить

Это проще, но совсем не обязателно

Автор: Smen Feb 10 2018, 10:12

Про NetTie знаю и использую когда цепи явно разные (типа цифровой и аналоговой земли) там известно место, где они соединяются (там и ставлю перемычку NetTie).

Вопрос про случай, когда не совсем понятно, в каком месте цепь будет разветвляться.

Собственно вопрос наверное более теоретический. Т.е. так понимаю, что не разделив цепи, контроль расстояния между дорожками невозможен?

Насчёт диф пар не понял, зачем? Я имел ввиду "контролировать зазор", что б дорожки не слиплись.

Автор: Владимир Feb 10 2018, 10:34

Можно.

Уже пару лет как правила можно писать для Same Net

Автор: Smen Feb 10 2018, 10:46

А у меня 13-я версия...

Автор: vGera Feb 10 2018, 17:07

Насчёт диф пар не понял, зачем? Я имел ввиду "контролировать зазор", что б дорожки не слиплись.

Не разделив цепи вы не найдете правила, которое бы Вам диктовало необходимость контроля расстояния между дорожками.

А разделив цепи самый простой способ жестко зафиксировать взаимную геометрию цепей - это дифпара. Как-то так.

А разве суфиксы _N и _P не обязательны?

http://electronix.ru/redirect.php?http://www.altium.com/documentation/18.0/display/ADES/((Differential+Pair+Routing))_AD

Я всю жизнь только так пары и делаю, их в современных проектах обычно очень много (пар), не одна. Грубо говоря, а как еще AD поймет, какие из цепей с директивой Diff pair, коих, скажем, 20 штук, образую пары (10 штук?? Ведь директива дифпары это набор параметров с DifferentialPair=true, без дополнительных параметров. М.б. в 17 и 18 версии уже не так?

Ну... нужно рассматривать конкретный пример. Может быть, Вам вообще полезны xSignals, когда контролируется топология цепи и длины ее сегментов. Без конкретики не совсем понятно, чего мы добиваемся.

Автор: Владимир Feb 10 2018, 19:32

Я всю жизнь только так пары и делаю, их в современных проектах обычно очень много (пар), не одна. Грубо говоря, а как еще AD поймет, какие из цепей с директивой Diff pair, коих, скажем, 20 штук, образую пары (10 штук?? Ведь директива дифпары это набор параметров с DifferentialPair=true, без дополнительных параметров. М.б. в 17 и 18 версии уже не так?

Да ни как не поймет.

Просто в PCB из двух любых цепей образовать дифпару и дать ей имя без всяких директив.

Это было всегда с самых старых версий.

Все отличие только в том, что на схеме это наглядно.

А на PCB нужно выбирать цепи из длинного списка всех возможных цепей.

Но при сноровке-- это быстро делается

Автор: Smen Feb 12 2018, 05:46

Так а мне не нужна жёсткая фиксация.

Мне необходимо соблюсти только минимальный зазор (что б при производстве дорожки не "слиплись").

Не понял, выше говорили, что в новых версиях возможно?

Автор: Владимир Feb 12 2018, 06:17

Да, возможно.

Где-то в районе 14-15 версий такая возможность появилась

Автор: RadiatoR Feb 12 2018, 12:35

Всем доброго дня.

Бывает такая ситуация, что можно использовать 2 разных компонента, а на плате сразу есть 2 футпринта, например:

Как в альте такое сделать? На схематике я могу выбрать вариант, а как на самой плате это сделать? Если создавать компоненты он добавляет только тот компонент, что есть в варианте, а нужно оба и чтобы они не ругались друг на друга при пересечении (хотя тут можно в правилах задать отрицательный клиренс).

Есть какой-то специальный метод для этого?

Автор: Владимир Feb 12 2018, 12:39

Сделайте специальный Footprint

Это будет самое простое, понятное и работающей из многих вариантов

Автор: Dmitry Dubrovenko Feb 12 2018, 15:57

Я так и делаю.

Автор: vGera Feb 15 2018, 07:16

Во всех схемах, которые я видел, в таких случаях просто кидают на схему два компонента (две микросхемы в разных корпусах), пишут что монтируется "или-или" (хть с вариантами АД, хоть нет), ну а в правилах если используется component clearance для этой парочки можно его просто выключить.

Автор: juvf Feb 16 2018, 10:10

В разных схемах (на разных листах) одного проекта объеденил цепь через Net Label. При экспорте в PCB выскакивает ошибка "Duplicate Net Names Wire GPIO_1". В PCB эти цепи обозначает как GPIO_1, но не объединяет, считает, что это разные цепи. Как сказать альтиуму, что это одна цепь?

Автор: Владимир Feb 16 2018, 10:45

В настройках проекта Net Label ==> Global

А дальше открыть панель Message и смотреть, где и почему на одной цепи 2 разных NetLabel

Автор: juvf Feb 16 2018, 11:24

Это где? Меню->Project->Project Options... Тут? А дальше? Не могу найти настройку Net Label.

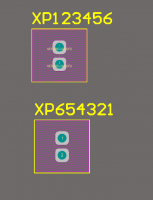

Для эксперимента добавил на одну схему новый разъем, назначил ему рефдес XP123456. Объединил его выводы цепью и назвал цепь NetLabel23ASDFG. См Снимок.png

Скопировал XP123456 с его цепями в буфер и вставил на другой лист. Переименовал рефдес в XP654321. Экспортирую схему в PCB. Получаю ошибку "Duplicate Net Names Wire NetLabel23ASDFG", см скриншот из Message.

На пп добавилось два разъема, но у одного нет цепей. См скрин. Почему возникает эта ошибка? Почему альтиум говорит Duplicate Net Names Wire?

ps вообще - что эта ошибка означает? Перевод понятен "Обнаружен дубликат имени цепи". Но ведь Net Label и создан для того, чтобы объединять цепи, т.е. если встречается две не обедненные цепи, и на них ставится одинаковая метка, то считается, что это одна цепь. Почему альтиум упорно продолжает считать что это разные цепи и говорит, что я назвал разные цепи одним именем?

Автор: Владимир Feb 16 2018, 11:40

Option

на одном листе

если на разных-- нужны соответсвующие настройки.

передача межу листами бывает

глобальные-- все передается на все

Через PORT - на другие литы передается только через PORT

Иерархическая (вертикальная) --- Через PORT и Sheet Entry

Многоканальная

Между листами ОДНОЙ функциональной группы (горизонтальная) через Sheet Connector

...

Автор: Vasily_ Feb 16 2018, 11:53

А что, Altium автоматом не умеет подключатся к шине как было в пикаде, или я опять что то пропустил?

Автор: Владимир Feb 16 2018, 12:04

А алтиума есть BUS для одноименных цепей. Там свой синтаксис в именовании и передаче сигналоа.

Harness для разнородных сигналов включая и сам BUS и Harnes

Первый является частичным аналогм для Pcаd в части одноименных сигналов

Второй это что-то, чего и близко не было в PCAD

В том понимании, как рисует большинства в PCAD -- это просто графика НИЧЕГО не означающая. Которую можно удалить, и ничего не изменится.

То есть можно было проста на рисовать Place/Line

Понимание Bus и как он работает происходит на 5 проекте.

До Harnes долетает не каждая пцица

Автор: juvf Feb 16 2018, 12:05

если на разных-- нужны соответсвующие настройки.

передача межу листами бывает

глобальные-- все передается на все

Просто если изначально проект создавать в АД, то ни чего специально настраивать не нужно. Net Identirier Scope установлен Automatic (Base on project contents).

Эотт проект - результат импорта проекта из EAGLE, позможно из EAGLE були подхваченны какието особые настройки, только я не смог их убрать.

Автор: Владимир Feb 16 2018, 12:08

Bus Entry -- это чистая графика для красоты оформления схемы (не более)

Ну тогда может быть и засуха и наводнеие и землетрясение.

Проект в студию

Автор: Vasily_ Feb 16 2018, 12:31

Это понятно, в пикаде это тоже чистая графика, только сделана гораздо умнее.

Расставлять Bus Entry ручками это маразм.

Автор: Владимир Feb 16 2018, 12:46

Ну да. в Pcad они автоматически появлялись.

Я быстро привык к этой особенности.

На самом деле потери времени практически нет

Автор: EvgenWL Feb 17 2018, 18:40

Это режим отображения цепей своим цветом. Настраивается в PCB Editor - Board Insight Color Overrides. Переключается по F5.

Автор: juvf Feb 19 2018, 02:56

Спасибо. Нашел эти настройки, нашел вкл/откл, управление цветом. В панели PCB выбирается цвет и цепь для подсветки.

Автор: moon333 Feb 20 2018, 14:25

Есть ли команда в AD, чтобы убрать не подключённые куски plane? Например для полигона есть Remove Dead Copper. А вот для plane такого не нашёл...

Автор: Constantin Feb 20 2018, 18:00

Чем искать такую команду, лучше заменить plane сигнальным слоем и залить полигон. Намного гибче и "надежнее".

Автор: Димон Безпарольный Feb 21 2018, 06:51

При доработке чужих проектов так и делал. Попутно хотел спросить - в чем преимущество Plane? Дорожку там не проведешь...

Автор: Uree Feb 21 2018, 07:49

Изначально плэйн-слои были придуманы для облегчения работы компа. Они не обрабатываются как сигнальные, с полным пересчетом контуров меди, поэтому многослойный проект с плэйн-слоями требует меньше ресурсов и быстрее "крутится" на слабых компах.

Но в общем и целом для нормальных САПРов это уже с десяток лет не актуально. Правда АД в их число пока не входит...

Автор: EvilWrecker Feb 21 2018, 07:59

Не войдет и без плейнов - и это еще просто перезаливка полигонов самая обычная. Вот когда дело доходит до удаления неиспользуемых падов

В плане разводки- ни в чем, а если еще split plane то и контролировать неудобно.

Автор: filip popov Feb 21 2018, 08:13

Островки или другие элементы можно удалить на слое плейна вручную, используя Place->Polygon Pour Cutout, указав в нем необходимый слой плейна.

Но занятие это весьма сомнительное. При перемещении элементов по плате необходимо будет все эти вырезы перемещать вручную.

Как уже неоднократно упоминалось, сигнальные слои с заливкой полигоном - более гибкий вариант.

Автор: peshkoff Feb 21 2018, 08:18

Нету такого. Забить. считать, что это "баланс меди"

Это зависит от количества цепей питания на плате

Автор: MVJ Feb 21 2018, 09:34

AD 14.3.10

Сделал плату и проверил DRC - никаких ошибок нет.

Сделал gerber-файлы (слои Тop, Bottom, TopSolder, BotSolder, Board(Механик1)) и решил их открыть и посмотреть. Все gerber-файлы отображаются нормально (ширина платы - во всю рабочую область экрана), кроме Bottom - он отобразился в несколько раз меньше в нижней части экрана. Догадываюсь, что, возможно, в проекте в слое Bottom присутствует какой-то элемент (возможно случайный трек) вне контура платы, но найти его не могу. В DRC проверки на наличие чего-либо вне контура платы не нашел.

Автор: Димон Безпарольный Feb 21 2018, 10:43

Непонятна политика инженеров Altium тогда получается. Вот перешли на 18 Altium отбросив все 32-битовые машины. А до сих пор по ресурсам жмутся... Чудно однако.

Автор: EvilWrecker Feb 21 2018, 11:05

Отбросить то отбросили, да только и 64 битами оно ест ресурсы так, как не снилось никакому другому пакету и близко и все равно тормозит. налицо эффективное использование ресурсов

Чтобы сравнить:сейчас в неспешной проработке вот http://electronix.ru/redirect.php?https://www.xilinx.com/products/boards-and-kits/vcu1525-a.html#hardware плата и что бы думали там по ресурсам? Аллегро просит слегка больше 200 метров на нее, изредка при определенных условиях доходит до 300. В альтиуме пойдешь удалять неиспользуемые пады на 10 слойке- несколько часов на перезаливку, просто сидишь и втыкаешь у монитора.

Сколько бы они там не говорили про

Автор: MVJ Feb 21 2018, 13:19

Сделал gerber-файлы (слои Тop, Bottom, TopSolder, BotSolder, Board(Механик1)) и решил их открыть и посмотреть. Все gerber-файлы отображаются нормально (ширина платы - во всю рабочую область экрана), кроме Bottom - он отобразился в несколько раз меньше в нижней части экрана. Догадываюсь, что, возможно, в проекте в слое Bottom присутствует какой-то элемент (возможно случайный трек) вне контура платы, но найти его не могу. В DRC проверки на наличие чего-либо вне контура платы не нашел.

Таки нашел. Если в PCB Filter выбрать Track - Free, слой Bottom, то нашелся крошечный трек вне платы (причем очень далеко от нее). Как он туда попал - х.з. Все-таки в DRC неплохо было бы иметь проверку на наличие чего-либо вне платы.

Автор: peshkoff Feb 21 2018, 13:50

Чтобы сравнить:сейчас в неспешной проработке вот http://electronix.ru/redirect.php?https://www.xilinx.com/products/boards-and-kits/vcu1525-a.html#hardware плата и что бы думали там по ресурсам? Аллегро просит слегка больше 200 метров на нее, изредка при определенных условиях доходит до 300. В альтиуме пойдешь удалять неиспользуемые пады на 10 слойке- несколько часов на перезаливку, просто сидишь и втыкаешь у монитора.

...

Не вводите в заблужение. В аллегро эта плата открывается как есть, а в альтиуме вы ее импортировали. при импорте альтиум не понимает какие границы полигона рисованные, а какие получились засчет обрисовки объектов.

И альтиум при импорте все границы прорисовывает даже там, где обтекание.

В итоге получаем полигон с десятками тысяч точек. Это видно в свойствах полигона. Потому так и тормозит.

И кстати, раньше эти точки можно было редактировать путем копирования в ексель и округления, сейчас эту функцию убрали...

Автор: EvilWrecker Feb 21 2018, 17:48

В этом и кроется подвох- я вообще не кручу эту плату в альтиуме и не пытался ее импортировать

Автор: vGera Feb 22 2018, 16:00

Плейны хороши при использовании impedance-controlled разводки (кмк AD только плейны в своих формулах и обрабатывает), с плейнами AD намного быстрее работает на любом компе, чем с полигонами, в герберы выгружается негатив и он компактнее. В общем, гибче - да, надежнее непонятно чем. Любая многослойка (нормальная) это чередование сигнальных слоев и слоев питания, что не почитай, типа рекомендаций по разводке всяких скоростных интерфейсов везде так. Вот в АД плейны и ввели.

Если Ваша версия верна... Я как-то тоже потерял нечто вне контура ПП, и сделал так. Выделил мышкой всю ПП, и на вкладке PCB Filter написал запрос "Not IsSelected". Выделилось нечто не выделенное и спрятавшееся где-то далеко за ПП, которое я не мог найти, и я его наконец-то удалил

UPD Ваш способ по теме ниже тоже хорош, но, как мне кажется, менее универсален в деле поиска "затерянных" непонятно каких объектов.

Автор: Uree Feb 22 2018, 17:36

Легче компу - да, а где Вы там гибкость увидели я не понял. С точностью до наоборот, никакой гибкости. Не говоря уже о наглядности.

Автор: Constantin Feb 22 2018, 17:52

Я как-то не доверяю "impedance-controlled" имени Altium'a и следовательно не использую.

Надежнее с том смысле, что если плейн не сплошной, то нужно очень внимательно следить за линиями раздела, иначе он сольет области без предупреждения и ага :-)

Автор: Sanchosd Feb 26 2018, 10:29

К сожалению да(((

У меня вообще абсурдная ситация:

Нужно помочь с железом. Плата, размер листа А4, 6 слоев. Никаих БГА, просто россыпь компоненов.

Пробую импортировать из ПКАДА, 18-м АД,- сваливается в Error при импорте непосредственно PCB файла.

Попробовал повторить несколько раз, так и не смог.

У одного из авторов стоит Альтиум 09!!!

Он мигом импортировал плату!!!!

Ну как так?

Дополнение ОЗУ до 8Гб никак не помогла. Когда смотрю в диспетчере задач мониторинг загрузки ЦП и загрузку памяти... короче там выгребается все, так, что самой винде не остается ничего)))))

Занятная штука:

Worspace, в нем список проектов.

По-умолчанию все проекты после запуска АД свернуты.

Развернуть проект, чтоб увидеть входящие в него папки- можно только кликнув на треугольничек рядом с его названием. Двойной клик не разворачивает.

Развернуть все входящие в проект папки можно двойным кликом.

Это так задумано, или никто не пользуется двойным кликом? оО

Автор: Димон Безпарольный Feb 26 2018, 11:05

Worspace, в нем список проектов.

По-умолчанию все проекты после запуска АД свернуты.

Развернуть проект, чтоб увидеть входящие в него папки- можно только кликнув на треугольничек рядом с его названием. Двойной клик не разворачивает.

Развернуть все входящие в проект папки можно двойным кликом.

Это так задумано, или никто не пользуется двойным кликом? оО

Иногда пользуюсь кода проекты меж собой связаны. Альтиум запоминает при выходе состояние. Повторный вход - уже не требуется разворачивать. Альтиум 17.

Автор: MVJ Feb 27 2018, 08:51

В PCAD200x есть программа для работы с библиотеками Library Executive, с помощью которой легко копировать из одной

библиотеки в другую как компоненты, так и отдельно УГО и футпринты, а также редактировать, удалять и пр. Почему подобного нет в AD (у меня версия 14.3.10)?

Автор: Владимир Feb 27 2018, 09:01

При использовании баз или Vault это бессмысленно.

В простых иногда вредно.

Но чем вас не устраивает копи-пасте. быстро, понятно, эфективно

Автор: Димон Безпарольный Feb 27 2018, 11:38

библиотеки в другую как компоненты, так и отдельно УГО и футпринты, а также редактировать, удалять и пр. Почему подобного нет в AD (у меня версия 14.3.10)?

Это еще проще. Открываете обе библиотеки, жмете CTRL и выбираете несколько элементов мышью. И копипаст.

Автор: G_A_S Mar 4 2018, 11:38

Доброго времени суток!

Подскажите, пожалуйста, как описать правило отступа ViaStiching от дорожек, для которых сформирован класс цепей.

Если в настройках ViaStiching кликнуть по созданию правила и во втором выражении прописать нужный класс цепей, поставив необходимый зазор, Альтиум игнорирует это правило.

Спасибо

Автор: Spartak Mar 5 2018, 08:40

Подскажите, пожалуйста, как описать правило отступа ViaStiching от дорожек, для которых сформирован класс цепей.

Если в настройках ViaStiching кликнуть по созданию правила и во втором выражении прописать нужный класс цепей, поставив необходимый зазор, Альтиум игнорирует это правило.

Спасибо

Ещё на приоритеты надо смотреть. Может там правило с другим значением более приоритетно.

Автор: musa Mar 6 2018, 08:57

Как изменить сочетание клавиш. В Альтиуме Выбор групы элементов делается с нажатой клавишей "Shift" С этой же клавишей происходит и выбор отдельных примитивов компоненте. Достаточно часто они конфликтуют что неудобно. Как для групового выбора переназначить клавишу допустим как и везде на "Ctrl"

Автор: Master_MW Mar 6 2018, 10:17

Доброго времени суток, уважаемые коллеги.

Может ли кто подсказать, есть ли возможность в AD17 отключить компиляцию в проекте "на лету" электрической принципиальной схемы?

Дело в том, что при установке каждого нового компонента в схему, AD компилит схему (снизу загорается надпись Compiling.....) и , при второй тысяче компонентов на многолистовой схеме ощутимо тормозит. Можно ли отключить он-лайн компиляцию? В PCB это делается, а как это сделать в схематике - не нашел ....

Автор: Smen Mar 6 2018, 11:27

Коллеги!

А как вывести в ПДФ только слой шёлкографии (производитель просит в качестве сборочного чертежа).

Пробовал при экспорте отключать все слои, кроме силка, но остаются только отдельные надписи, а те, которые входят в футпринты пропадают.

Автор: Master_MW Mar 6 2018, 11:44

А как вывести в ПДФ только слой шёлкографии (производитель просит в качестве сборочного чертежа).

Пробовал при экспорте отключать все слои, кроме силка, но остаются только отдельные надписи, а те, которые входят в футпринты пропадают.

Рекомендую Вам освоить такой инструмент, как Assemply Drawning (File-Assemply Outputs-Assembly Drawnings). Нам Резонит неоднократно собирал по ним модули. Пример результата в аттаче.

Автор: musa Mar 6 2018, 11:50

А при чем здесь шелкография. Шелгография это слой маркировки на плате. В нем ничего лишнего и не должно быть. Графика сборочного чертежа формируется в соответствующих механических слоях и вы всеравно эту графику делаете. Выводите и её тоже. Посмотрите что у вас указано в задании на печать может галочку какую нибудь не поставили. Вот он и не знает что вы хотите вывести на печать.

Автор: Smen Mar 6 2018, 12:19

У меня только можно в метафайл (AD13).

Автор: Master_MW Mar 6 2018, 12:23

У меня только можно в метафайл (AD13).

Просто распечатываете в пдф через, например, pdf creator.

Автор: musa Mar 6 2018, 12:48

Он просто попросил PDF по которому можно собрать плату

Автор: Smen Mar 7 2018, 10:09

Не совсем понял, надо "отправить на печать" (не пользовался pdf creator)?

Автор: Sanchosd Mar 7 2018, 12:52

Друзья, такой вопрос.

Имеем простенький проектик.

В нем плата схема(1 лист), плата №1(с деталями и печатью), платка №2(голый текстолит).

Плата 2 выполняет роль "флажка", или упора, который вставляют в профрезерованный паз в первой плате.

Генерирую STEP из обоих плат, вставляю плату №2 как Place->3D Body в плату №1 в режиме 3D.

Выставил как нужно, сохранил.

Переделал плату №2 немного, сгенерировал STEPы.

Посмотрел, файлы новые, открыл в MCAD- форма изменилась, т.е. к генерированию STEP претензий нет.

АД выкинул окошко, что мол STEP обновился, заменить? Подтверждаю- заменить(обновить).

Но, в режиме просмотра 3D, альтий ничего не обновляет. Форма платы №2 осталась прежней.

Где-то кто-то тут писал про кэширование 3Д моделей...

Подскажете чего?

Спасибо!

ЗЫ: В меню Properies 3D тела, где кнопки "Vault","Embed", "Link", есть кнопочка с символом "обновить",она тоже не работает, или я неправильно ее понимаю.

Автор: musa Mar 8 2018, 07:36

Как настроить свойство переходного отверстия чтобы оно не соединялось с внутренними слоями подключенними к той же цепи.

Автор: Владимир Mar 8 2018, 07:59

Запретите топологию на таком слое для этой цепи. Для полигонов запретите подключение к Via

Автор: musa Mar 8 2018, 08:42

Задача не в этом. Нужно запретить не для всей цепи а для конкретного переходного. Нужно для оптимизации подключения к цепям питания.

Автор: Владимир Mar 8 2018, 08:57

Используйте Free-PaD вместо Via, в таком случае

Или еще лучше Place/Polygon CutOut в зоне, где не нужно подключение

Автор: musa Mar 8 2018, 09:59

Ну как вариант но несколько хлопотно. Тоесть нужно поставить , подключить к цепи. Via ставятся сами. CutOut применять неудобно.

Автор: Владимир Mar 8 2018, 10:11

Но если одно место - то это быстрее чем правила и другие хитрости.

если десяток, второй таких Via то тоже быстрее. После первого --- копи пасте хорошо работает

Автор: Mr.M Mar 10 2018, 07:53

День добрый коллеги!

Встала задача сделать тестовые площадки на плате и вот возникла проблема.

Производитель ПП указывает следующие требования:

· Расстояние от компонентов высотой менее 2,5 мм до центра тестовой площадки не должно быть меньше

0,635 мм.

· Расстояние от компонентов высотой 2,5мм…5,0 мм до центра тестовой площадки не должно быть меньше

0,965 мм.

· Расстояние от компонентов высотой 5,0мм…10,0 мм до центра тестовой площадки не должно быть

меньше 3,0мм.

Вопрос: Как настроить это в правилах проектирования?

Я пытался настроить дополнительные правила для высоких компонентов, но из этого ничего не вышло.

Подскажите, как быть?

Автор: Master_MW Mar 10 2018, 20:12

Может ли кто подсказать, есть ли возможность в AD17 отключить компиляцию в проекте "на лету" электрической принципиальной схемы?

Дело в том, что при установке каждого нового компонента в схему, AD компилит схему (снизу загорается надпись Compiling.....) и , при второй тысяче компонентов на многолистовой схеме ощутимо тормозит. Можно ли отключить он-лайн компиляцию? В PCB это делается, а как это сделать в схематике - не нашел ....

Извиняюсь за настырность, но таки никто не подскажет?

Автор: _Макс Mar 11 2018, 12:00

Коллеги, при экспорте DXF/DWG получаю в MCAD-е трассы в виде линий. Пробовал разные опции импорта в NX и SolidWorks.

Мне нужно получить очертание трасс с учетом их актуальной ширины на металлическом слое. В идеале, с дырочками, там где пады. Как это сделать?

AD 17.1.6

Автор: Spartak Mar 11 2018, 12:52

Мне нужно получить очертание трасс с учетом их актуальной ширины на металлическом слое. В идеале, с дырочками, там где пады. Как это сделать?

AD 17.1.6

Экспортируйте в виде блоков, полилиний и т.п., не делайте разбивку на элементы, и всё будет в порядке. Там другое неприятно, с текстом придётся повозиться. Текстовые стили не совпадают от слова СОВСЕМ. А зачем Вы в SW DXF экспортируете, это же трёхмерка? Там надо STEP или (лучше) PARASOLID. DXF формат лучше всех понимает его родоначальник AUTOCAD.

Автор: _Макс Mar 11 2018, 13:03

Из Altium в SolidWorks или NX.

Мне нужны только контуры выбранных дорожек. Я сам выберу, будь они конурами, а не линиями. В этом проблема.

Никакого 3D и текста не нужно. Это другое.

Автор: Iptash Mar 11 2018, 14:04

Как отключить Show Simple 3D Bodies в 17 версии в библиотеке. В 15 версии в левом нижнем углу просмотра 3D можно было отключать. В 17 версии там переключатель 3D 2D

Автор: Владимир Mar 11 2018, 14:53

Да тамже. В первой вкладке View Configuratiun

Автор: Владимир Mar 11 2018, 16:58

Ну так это не в библиотеке, а в панели.

Никогда не интересовала, так как давно не использую включение Footprint в УГО

Автор: Iptash Mar 11 2018, 19:25

В свойствах общее отключение есть и все. Но оно реагирует только в PCB библиотеке и в 3D.

Автор: Spartak Mar 12 2018, 11:41

Мне нужны только контуры выбранных дорожек. Я сам выберу, будь они конурами, а не линиями. В этом проблема.

Никакого 3D и текста не нужно. Это другое.

Так КОНТУРЫ дорожек Вы иначе, чем через PARASOLID не получите, он передаёт дорожки как трёхмерную ленту с высотой, равной толщине фольги. Потом из восстановленной трёхмерки можете делать чертёж, и там будут КОНТУРЫ. Может Вам нужно что-то вроде этого (см. вложения)? Тогда можно и по-другому.

Автор: koluna Mar 12 2018, 12:43

Всем привет.

Подскажите, пожалуйста, как дла Альтиума девятого получить файл pick & place с координатами компонентов для автоматического монтажа?

Автор: Владимир Mar 12 2018, 12:50

Служба Job

Assembly Output\Generate Pick and Place Files

Добавить службу и настроить

Автор: koluna Mar 12 2018, 12:55

Добавить службу и настроить

Это сразу и для SMD и для штыревых одновременно?

А вообще, что еще нужно для авт. монтажа? Два слоя паяльной пасты для трафаретов?

Автор: Владимир Mar 12 2018, 15:48

как настроите. Хотите вместе,хотите раздельно.

Хотя это уже дело производства. Они все равно его переделывают.

Что нужно-- зависит от того, где делать собираетесь.

Там лучше и спрашивать.

Автор: -=Space=- Mar 12 2018, 16:31

Подскажите с такими граблями.

Требуется немного откорректировать графику (шелкографию) компонента на плате. Именно на плате, а не в библиотеке.

Конкретно нужно сдвиуть две линии, обозначающие "+" у конденсатора. У некоторых элементов он попадает на пады соседних элементов.

Как пытаюсь делать:

Снимаю галку lock primitives, выделяю линию. Пытаюсь сдвинуть курсором с крестиком - никак, стоит на месте.

Могу сдвинуть курсором ввиде стрелочек, но только один конец линии и только в одном направлении (горизонтально или вертикально).

За центр тянется с изгибом.

На произвольное место удается сдвинуть, только если задать координаты вручную. Но это маразм и дико не продуктивно.

Кстати сам контур компонента двигается легко, проблема тольок с "+".

Такое ощущение, что есть где то привязка, но я не найду где, я их все отключил. По клику на кнопку Snap внизу окна в меню все галочки сняты. Может еще где то осталась?

Еще коротенький вопрос, можно ли назначить горячую кнопку на свой набор слоев и быстро переключать их, как shift+s?

Автор: Владимир Mar 12 2018, 17:19

Надо было обозначать или знаком "+", или в зоне запрета установки других элементов.

В первом случае текст легко и двигается и размер меняется.

Во втором случает обозначение никогда не попадет на пад соседнего элемента.

Теперь придется "мучаться в любом случае

Автор: _Макс Mar 12 2018, 18:19

Мне нужно порезать материал по контуру дорожки с заданным отступом от края. Собственно для этого и нужен сам контур в каком-то формате. Достаточно 2D. Как его получить, ума не приложу.

Автор: -=Space=- Mar 12 2018, 18:45

Да, этот способ думаю лучший, не так много кондеров-электролитов, переделать либы и все.

Интересна причина такого поведения. Попробовал на диоде, там тоже одинокая линия не двигается.

Автор: Constantin Mar 12 2018, 20:00

Я бы смотрел в сторону вывода в GERBER и попытался получить нужный результат в соответствующих редакторах. Или еще лучше - получение из GERBER'ов контура с нужным отступом в программе подготовки управляющих файлов для сверлильно - фрезерных станков с ЧПУ.

Автор: koluna Mar 13 2018, 06:29

А где настроить?

В самом задании у меня только две настройки - формат и единицы.

Автор: Владимир Mar 13 2018, 07:16

Двойно клик по службе

выскочит таблица с настройками, параметрами где можно все отсортировать, Включит , исключить и т.п.

Там все также, как и при генерации BOM

Автор: koluna Mar 13 2018, 08:37

выскочит таблица с настройками, параметрами

А вот не выскакивает... только формат и единицы.

Может, у меня Альтиум слишком старый (9.3.1)?

Автор: Владимир Mar 13 2018, 08:42

Может, у меня Альтиум слишком старый (9.3.1)?

не помню.

таких старых версий нет.

а операция экзотическая.

у меня просили ее только несколько раз, да и то наверное не использовали

Автор: Анна Анна Mar 13 2018, 09:01

Встала задача сделать тестовые площадки на плате и вот возникла проблема.

Производитель ПП указывает следующие требования:

· Расстояние от компонентов высотой менее 2,5 мм до центра тестовой площадки не должно быть меньше

0,635 мм.

· Расстояние от компонентов высотой 2,5мм…5,0 мм до центра тестовой площадки не должно быть меньше

0,965 мм.

· Расстояние от компонентов высотой 5,0мм…10,0 мм до центра тестовой площадки не должно быть

меньше 3,0мм.

Вопрос: Как настроить это в правилах проектирования?

Я пытался настроить дополнительные правила для высоких компонентов, но из этого ничего не вышло.

Подскажите, как быть?

Строки для выбора компонентов по высоте в правилах:

IsComponent And (Height < 2.5)

IsComponent And ((Height >= 2.5) And (Height < 5))

IsComponent And ((Height >= 5) And (Height < 10))

Автор: Mr.M Mar 13 2018, 18:07

IsComponent And (Height < 2.5)

IsComponent And ((Height >= 2.5) And (Height < 5))

IsComponent And ((Height >= 5) And (Height < 10))

Спасибо за ответ)

Но не в этом проблема. Высоких компонентов не так много, я их по отдельности указать могу. Проблема собственно в том что дальше делать? Хотя бы для одного конкретного компонента. Как правило прописать? Чтоб было одно общее и несколько дополнительных, для высоких. Я как не пытался, только основное работает..

Автор: Анна Анна Mar 14 2018, 06:18

Но не в этом проблема. Высоких компонентов не так много, я их по отдельности указать могу. Проблема собственно в том что дальше делать? Хотя бы для одного конкретного компонента. Как правило прописать? Чтоб было одно общее и несколько дополнительных, для высоких. Я как не пытался, только основное работает..

А вы напишите сюда:

1) своё правило, которое работает,

2) те правила, которые не работают,

3) и каким объектом у вас является контрольная точка (Arc или Pad или ...)?

Автор: Владимир Mar 14 2018, 06:27

Все зависит от того, как вы оформляете сами компоненты, тестовую точку.

P.S. Если у вас их не много-- сделайте все в ручном режиме. Это будет быстрее чем писать и проверять правила, править библиотечные компоненты и т.п.

Автор: Mr.M Mar 14 2018, 18:55

Владимир , я пока и делаю в ручном режиме, но всё таки хочется разобраться, в будущем ещё пригодится)

Анна Анна

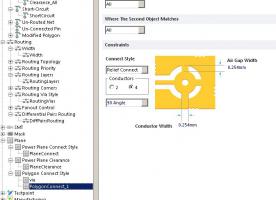

Контрольная точка это Pad, добавляю прямо в PCB редакторе. (Пад выбирается командой "(ObjectKind = 'Pad') And (AsMM(PadXSize_AllLayers) = 0.9) And (AsMM(PadYSize_AllLayers) = 0.9)")

Основное правило задаётся как показано на картинке (для всех компонентов).

Дополнительные правила которые не работают не вижу смысла кидать, да и нету их в сохранённом виде. Я просто перебирал все варианты, что в голову приходили, но, увы, безрезультатно.

http://electronix.ru/redirect.php?https://postimages.org/

https://s14.postimg.org/pftch17yp/image002.jpg

Автор: RadiatoR Mar 15 2018, 04:50

Mr.M, добрый день.

А что это у Вас за симпатичная темная тема альта?

Автор: Mr.M Mar 15 2018, 05:50

А что это у Вас за симпатичная темная тема альта?

Это новая стандартная тема в AD18 и Altium NEXUS.

Очень приятная вещь, глаза меньше устают. Хотя пару дней попривыкать придётся)

Автор: RadiatoR Mar 15 2018, 05:52

Dark тема в visual studio давно привычная вещь. Очень приятная. Приятно, что альтий взял ее на вооружение и, судя по фото, сделал ее нормально.

А Нексус что за зверь такой?

Автор: Mr.M Mar 15 2018, 06:07

А Нексус что за зверь такой?

Да тоже самое, только с заделом на совместную работу.

Скрин для наглядности.

http://electronix.ru/redirect.php?http://www.altium.com/documentation/sites/default/files/wiki_attachments/296627/AltiumNEXUSGraphic.png

Автор: RadiatoR Mar 15 2018, 06:12

Наглядно, спасибо.

Хорошо, что компания прёт

Автор: Анна Анна Mar 15 2018, 06:52

Анна Анна

Контрольная точка это Pad, добавляю прямо в PCB редакторе. (Пад выбирается командой "(ObjectKind = 'Pad') And (AsMM(PadXSize_AllLayers) = 0.9) And (AsMM(PadYSize_AllLayers) = 0.9)")

Основное правило задаётся как показано на картинке (для всех компонентов).

Дополнительные правила которые не работают не вижу смысла кидать, да и нету их в сохранённом виде. Я просто перебирал все варианты, что в голову приходили, но, увы, безрезультатно.

http://electronix.ru/redirect.php?https://postimages.org/

https://s14.postimg.org/pftch17yp/image002.jpg

Mr.M, про раздел правил Testpoint я ничего не подскажу, никогда им не пользовалась (и по моему опыту с Altium - не всё, что в правилах декларировано - работает). Для контроля расстояний использую разделы Electrical/Clearance и Placement/Component Cliearance. Нужные вам правила я бы завела в раздел Electrical/Clearance.

Автор: Mr.M Mar 15 2018, 08:48

Так дело в том, как я понял, что Electrical/Clearance работает только с элементами топологии, а Placement/Component Cliearance с 3D моделями, а мне нужно правило между 3D моделью и элементом топологии. Поэтому ни в том ни в другом разделе ничего сделать не получилось. Ну либо всё таки руки не оттуда растут.

Попробуйте вы задать такое правило, есль не затруднит, и отпишитесь если вдруг получится.

Автор: RadiatoR Mar 15 2018, 08:52

Не обязательно.

У меня работает нормально правило между компонентом и переходным http://electronix.ru/redirect.php?https://c2n.me/3SEgtNR

Автор: Владимир Mar 15 2018, 09:04

1. Так как требуется Testpoint с отступом от высоких компонентов то это в раздел Assembly TestPoint

2. У вас стоит флаг Allow Testpoint Under Component

Для Assembly TestPoint он должен быть снят

Автор: Анна Анна Mar 15 2018, 10:34

Не получилось у меня в Electrical/Clear. сделать работающее правило.

А в CompClear. получилось, сделав тестовую точку компонентом из одного Pad.

IsComponent And (Height < 2.5)

__________________________

InComponent('15','16') //перечислить компоненты-тестовые точки

__________________________

Minimum Horizontal Clearance = 0.635 //здесь надо учесть слой TopSolder площадки, если SolderMaskExpansion=0,1, то расстояние задать 0,535.

__________________________

Minimum Vertical Clearance = 0

Автор: Димон Безпарольный Mar 15 2018, 10:47

Перестали отображаться связи на PCB в одном проекте. Отображаются только при перетаскивании. Опять что - то съехало. Как поправить?

Автор: RadiatoR Mar 15 2018, 11:40

View -> Connections -> Show all

Автор: Димон Безпарольный Mar 15 2018, 14:58

Спасибо. Почему - то земляной полигон наступает на полигон 3.3В. На скриншоте - если дорожу убираю, земляной полигон заполняет все пространство как будто полигона 3.3В вообще нет.

http://electronix.ru/redirect.php?https://postimages.org/

http://electronix.ru/redirect.php?https://postimages.org/

Что надо подправить?

Автор: Владимир Mar 15 2018, 15:00

Приоритеты настроить

Автор: RadiatoR Mar 16 2018, 04:43

T -> G -> Enter

Далее в области Pour order выбрать порядок заполнения полигонов

Автор: musa Mar 16 2018, 12:24

Что то непонял как в Free-PaD сделать отключение от определенных слоев.

Автор: peshkoff Mar 16 2018, 12:52

ему можно присвоить имя, а потом в правилах использовать. видимо это подразумевается

Автор: Владимир Mar 16 2018, 12:56

Уберите медь на этом слое в настройках PAD

В правилах задайте зазор до Hole

Не подключит

Автор: peshkoff Mar 16 2018, 12:58

В правилах задайте зазор до Hole

Не подключит

ну если медь убрать, то и виа не подключит

Автор: Владимир Mar 16 2018, 13:02

У Via нет настройки ободка по слоям. По крайней мере в старых версиях

Автор: Spartak Mar 16 2018, 18:08

Сейчас уже Full Stack для Via редактировать можно.

Автор: Димон Безпарольный Mar 16 2018, 19:18

Почему при распечатке 3D панели (place board array) на виде 3D не видно дорожек? Это где - то настраивается?

Автор: KA_ru Mar 22 2018, 12:20

Есть много канальная схема хочу подключиться к линии только в одном канале. Линия с именем. Возможно такое?

Автор: Lehin_05 Mar 22 2018, 12:47

Возможно. На видео рассказывают как сделать http://electronix.ru/redirect.php?https://youtu.be/Ic3tv5pcKyQ

Автор: KA_ru Mar 22 2018, 20:07

Это стандартный подход с портом. У меня есть линия которую я не хочу выводит через порт.

Автор: Владимир Mar 23 2018, 05:11

Определитесь, что вы хотите.

Многоканальные системы подразумевают вертикальную связь через порты.

Если хотите схему "запутать", то в PCB есть куча возможностей это сделать без изменения схемы

Автор: -=Space=- Mar 23 2018, 07:30

Использую функцию схемы Net color.

подсвечивает цепи согласно логики (цифровое питание - красный, аналоговое - розовый и так по всем цветам)

Не нравится, что функция работает крайне медленно. После клика по цепи Альтиум подвисает на 2-3 секунды.

Как ускорить? может отключить какие проверки можно? Например , если на схеме два совпадающих десигнитора , он запарит про эту ошибку, хотя мне на данном этапе она не важна.

Автор: musa Mar 25 2018, 06:38

Напомните как компонент исключить из проверки зазоров между падами или создать правило. Вроде недавно это где то описывалось

Автор: Владимир Mar 25 2018, 09:07

В последних версиях достаточно в правиле поставить флаг (надеюсь найдете без картинки)

В старых-- нужно было писать или исключения в правиле или дополнительное правило

Автор: musa Mar 25 2018, 17:33

У меня 16 версия. Что то не нашел.

В правилах нашел. Но вроде был вариант проще

Автор: Владимир Mar 25 2018, 18:13

Куда уж проще? тыкнуть на флаг

Автор: Professor Chaos Mar 25 2018, 20:08

Флаг "Ignore Pad to Pad clearances within footprint" надо поставить.

Автор: _Макс Mar 25 2018, 23:12

К сожалению, даже при экспорте DXF из Camtastic я снова вижу в механическом каде вместо очертаний дорожки, линию нулевой толщины. Не понимаю, что там не передается, но получается, что Altium упрямо подменяет контур дорожки центер-линией.

http://electronix.ru/redirect.php?https://postimages.org/

Мне нужно очертание контура дорожки, чтобы сделать offset, скомбинировать на листе и отдать на порезку материала (листовая медь).

Я подумал использовать эту команду:

http://electronix.ru/redirect.php?https://postimages.org/

Созданный outline я могу переместить на механический слой и сделать экспорт в механический CAD.

Но у меня вопрос: из какого правила Altium берет зазор и толщину линии для создания контура данной командой? В моем случае, создалась линия толщиной 0,203 мм, такого значения у меня нет ни в одном правиле! Оно не типичное.

http://electronix.ru/redirect.php?https://postimg.org/image/m1fkslb5x/

Столь же странным (дробное значение) получился шаг с которым содается контур...

http://electronix.ru/redirect.php?https://postimg.org/image/9a1ema40l/

Какими правилами управляется эта команда?

Автор: musa Mar 26 2018, 03:58

Ну это когда есть куда поставить. А как создать правило аналогичное галочке. Чтобы именно игнорировать.

Автор: Sanchosd Mar 27 2018, 10:02

Друзья, подскажите, а как сделать так, чтоб реперные точки попадали в pick&Place файл?

Репера я вручную ставлю.

Может как-то более изысканно все делается?

Автор: filmi Mar 27 2018, 10:11

Репера я вручную ставлю.

Может как-то более изысканно все делается?

Делайте их как компонент - тогда попадут!

Автор: musa Mar 27 2018, 10:25

В альтиуме можно переместить компонент просто подхватив его мышкой. Иногда это просто мешает так как подхватывается не то что нужно. Как сделать чтобы двигать можно было только после выделения

Автор: Sanchosd Mar 27 2018, 13:18

Если уж про Harness зашла речь, подскажите, имя цепи ХХХ, вход и выход Harness connector'a тоже должен называться XXX?

Или можно вообще цепь не называть, она автоматом получит имя harness Entry?

Пользую Harness, но недавно и немного, компилятор ругается, что что-то с именами, хоть реально все в порядке и на плате все работает.

ооК)

Автор: Владимир Mar 27 2018, 13:26

Или можно вообще цепь не называть, она автоматом получит имя harness Entry?

Пользую Harness, но недавно и немного, компилятор ругается, что что-то с именами, хоть реально все в порядке и на плате все работает.

Не обязательно. Entry - это формально номера проводов в жгуте.

Но для Еntry для BUS -- синтаксис соблюдается такой же

Netlabel желательно ставить на таких цепях, иначе сложно разобраться

Автор: Smen Mar 28 2018, 07:27

Коллеги, напомните, где настраивается появление линий указывающих, что по этой координате есть компонент, когда начинаешь перетаскивать другой компонент (в примере на картинке перетаскивается реперная точка и появляется вертикальная линия)?

http://electronix.ru/redirect.php?https://postimages.org/

Автор: Smen Apr 2 2018, 07:12

Коллеги, неужели вопрос настолько глуп, или все в отпусках? ![]()

Автор: musa Apr 2 2018, 07:26

Да нормальный вопрос. Просто никто не парится. Нажимаете Shift и двигаете. При совпадении появляется маркер. Никто его не включает и не выключает.

Автор: Smen Apr 2 2018, 08:04

Так он у меня без всякого Шифта появляется.

Автор: peshkoff Apr 2 2018, 10:43

что за линия появлется? перекрестие что ли? в настройках можно выставить Large 90 и small 90. других настроек нет...

Автор: Smen Apr 3 2018, 09:17

Линия от центра перетаскиваемого объекта до центра другого объекта, когда эти центры совпадают (по вертикали, или горизонтали)

Автор: Constantin Apr 3 2018, 15:59

Это признак привязки, меню настроек вызывается кнопкой "Snap" в правом нижнем углу PCB редактора.

Автор: musa Apr 6 2018, 04:47

Можно ли в Альтиуме выделить несколько пинов и назначить им имя цепи а то задолбало тыкаться на каждый пин открывать его свойства и в них искать цепь с которай его нужно соединить. Или может есть способ проще?

Автор: peshkoff Apr 6 2018, 05:39

Можно, конечно. Нужно создать документ, называется .SchDoc

Автор: RadiatoR Apr 6 2018, 05:45

Так вы можете вашим же способом это делать, просто выделите нужные пады и в PCB Inspector установите поле Net.

Но правильно, конечно же, через схему.

Автор: Владимир Apr 6 2018, 06:25

Это для существующей Net

Для новой-- надо ее сперва создать

Все это так.

Но схемы может и не быть

Автор: Smen Apr 6 2018, 06:34

Автор: musa Apr 6 2018, 07:03

Странно но работает.

Автор: Владимир Apr 6 2018, 07:55

Это работало всегда

Автор: musa Apr 6 2018, 10:09

Ну обычно выделяешь несколько примитивов вызываешь инспектор и что нибудь меняешь. Но меняется только в одном. И потом долго думаешь по какому признаку объединить их чтобы потом изменить во всех. Но получается что в каких то случаях можно и выделив несколько что то изменить.

А по поводу "давно известно" кому то известно но большинству не слишком опытных скорее нет. В книках то об этом не написано и где нам об этом узнать? Вот только не надо посылать на англоязычный сайт.

Автор: Владимир Apr 6 2018, 10:47

Не верю

Автор: RadiatoR Apr 9 2018, 08:55

Всем доброго дня.

Есть проблема:

Есть правило [Un-routed net], которое это разрешает, но вынуждает тащить цепь до самого центра примитива, что не всегда требуется, например здесь:

Есть ли правило, которое считает сечение металла, соединяющегося с примитивом и если оно меньше, то высвечивает ошибку?

В дополнение поясните, что делают эти опции:

Спасибо.

Автор: Владимир Apr 9 2018, 10:06

у вас там все есть. второй флаг в отмеченном включите.

Только задумываться при проверке будет (то есть проверка занимает времени раза в 3-5 дольше)

Автор: Sergey Makarov Apr 10 2018, 06:24

Добрый день!

Подскажите пожалуйста как работает функция Align. Не работает по отношению к проводникам в PCB функция Align to grid. И не понятно как поменять расстояние на которое функция Align Left/Right (maintain spacing) раздвигает проводники. Мне необходимо расположить большую группу проводников на одинаковом расстоянии друг от друга, думал смогу воспользоваться этой функцией чтоб вручную не толкать проводники. Но результатом функции Align Left/Right (maintain spacing) получается расстояние 2,2 мм, а нужно 0,35 мм. В хелпе пишут что расстояние должно соответствовать расстоянию из правил.

Автор: musa Apr 10 2018, 06:50

Ну и объедините их в отдельный класс и для него создайте собственное правило

Автор: Sergey Makarov Apr 10 2018, 07:10

вопрос не как вести проводники с помощью правил, а как работает функция Align.

Автор: adnovice Apr 10 2018, 11:13

Подскажите, пожалуйста, как избавиться от увеличивающей рамки.

Автор: musa Apr 10 2018, 12:00

В настройках РСВ в разделе Board Insight Lens отключите видимость

Автор: Димон Безпарольный Apr 13 2018, 06:12

У кого - нибудь было такое:

Альтиум работает если есть Net Framework 4.6.1

http://electronix.ru/redirect.php?https://postimages.org/

Но дюже умная винда при обновлении его сносит устанавливая 4.7.1. После установки 4.7.1. дюже умный мелкософт запрещает ставить 4.6.1 обратно. Альтиум (17.1) без 4.6.1 не запускается сваливаясь в циклическую ошибку.

18-й альтиум кстати тоже.

В итоге систему приходится откатывать взад ибо запрещать обновление 4.7.1. Но если не успел запретить - получи от мелкософта.

Автор: peshkoff Apr 13 2018, 08:24

framework 4.7.1 все альтиумы работают 13..18

Автор: -=Space=- Apr 18 2018, 08:22

Делаю базу компонентов DBLib, разъемы.

Они делятся на штыри (XP?) и гнезда (XS?). Символ использую один и тотже "conn-XXpin", где XX число пинов.

Default Designаtor "XP?" и его надо , в некоторых случаях, перезаписывать на "XS?"

Все параметры удалось перезаписывать, например поле Comment или Description переносится из базы в компонент

А с полем Designаtor засада, оно не перезаписывается, хотя в список параметров попадает.

Это вообще возможно? или придется плодить два символа на каждый тип?

Автор: Владимир Apr 18 2018, 10:21

УГО для штырей и гнезд различаются.

То есть плодить (не верное слово так как только 2) символы не придется, это необходимость

Автор: -=Space=- Apr 18 2018, 11:20

О, это совершенно не обязательно.

http://electronix.ru/redirect.php?http://docs.cntd.ru/document/1200086241 рисунок 9

мы спользуем две первые колонки, редко (на схемах соединений блока) все три.

потом плодить не два символа, а по два , даже по 3 на каждое число пинов (еще контактные поля на ПП , которые не имеют ни штырей, ни гнезд, обознчаются X или, для стройности все двух-буквенные, XT)

Автор: Владимир Apr 18 2018, 12:13

Это не УГО, а таблица в замен УГО.

И пункт касается только "5.3.25 Характеристики входных и выходных цепей изделия..."

И там использовано обозначение X1.

Не для всех соединителей такое показывают это и это не является обязанностью.

Ну так и используйте однобуквенное обозначение.

Оно ГОСТ тоже не запрещено.

Автор: Gluk Apr 19 2018, 08:49

Из Easy-PC можно перетащить проекты в альтиум?

Автор: MVJ Apr 20 2018, 13:04

AD14. Сделал схему и плату, при этом компоненты брал из разных библиотек. После этого командами "Make Schematic Library" и "Make PCB Library" сделал соответственно библиотеки SchLib и PcbLib с именем проекта. Как правильно указать, что теперь все компоненты находятся в новых библиотеках? Для схемы получилось - через SCH Inspecror поменял свойство Library сразу для всех компонентов, а как для PCB ?

Автор: Владимир Apr 20 2018, 18:34

Достаточно в Footpint Manager указать Any для всех Footprint.

Есть еще Parameter Manager, PCBLIST, Инспектор

Там тоже можно

Автор: MVJ Apr 23 2018, 07:26

В схеме через Footpint Manager (+ Validate, Execute Changes) поменял библиотеку на новую (созданную Make PCB Library) - в плате ничего не поменялось и Design->Update PCB Document никаких изменений не предлагает. По-прежнему если открыть в PCB свойство любого компонента, то в Footprint->Library будет указана его старая библиотека.

Там тоже можно

В Parameter Manager , PCBLIST и PCB Inspector тоже не нашел как заменить библиотеку.

Автор: Владимир Apr 23 2018, 18:16

Так если название Footprint не изменилось, то и не поменяет.( оно не сверят, что это разное)

Поменяйте принудительно из библиотеки -- Тогда точно обновит

или Tools >> update from PCB Library -- тогда обновит то, что настроите

Автор: MVJ Apr 27 2018, 08:14

или Tools >> update from PCB Library -- тогда обновит то, что настроите

Уточню вопрос.

Имеем проект со схемой и платой (допустим Project1). Компоненты были взяты из нескольких библиотек (допустим Lib1.IntLib, Lib2.IntLib, Lib3.IntLib и т.д.). После выполнения команд "Make Schematic Library" и "Make PCB Library" получили соответственно библиотеки Project1.SchLib и Project1.PcbLib. Теперь если открыть в PCB свойство какого-нибудь компонента, то в Footprint->Library будет указана его старая библиотека (например Lib2.IntLib). Как теперь для всех компонентов заменить это свойство на Project1.PcbLib? В схеме можно через SCH Inspecror поменять свойство Library на Project1.SchLib сразу для всех компонентов, а вот в PCB через PCB Inspecror свойство Footprint->Library недоступно. Можно, конечно, вручную для каждого компонента, но в плате две сотни компонентов.

Автор: Spartak Apr 27 2018, 14:01

Имеем проект со схемой и платой (допустим Project1). Компоненты были взяты из нескольких библиотек (допустим Lib1.IntLib, Lib2.IntLib, Lib3.IntLib и т.д.). После выполнения команд "Make Schematic Library" и "Make PCB Library" получили соответственно библиотеки Project1.SchLib и Project1.PcbLib. Теперь если открыть в PCB свойство какого-нибудь компонента, то в Footprint->Library будет указана его старая библиотека (например Lib2.IntLib). Как теперь для всех компонентов заменить это свойство на Project1.PcbLib? В схеме можно через SCH Inspecror поменять свойство Library на Project1.SchLib сразу для всех компонентов, а вот в PCB через PCB Inspecror свойство Footprint->Library недоступно. Можно, конечно, вручную для каждого компонента, но в плате две сотни компонентов.

Заменили библиотеки в схематике - откомпилируйте проект, затем передайте изменения на плату. Откуда же иначе редактор плат узнает об изменениях?

Автор: peshkoff Apr 28 2018, 07:15

в этом случае он заменит футпринт только если он поменялся.

Если в названии не было изменений, то и обновления не пройдет.

на самом деле задача не такая тривиальная. в свое время даже скрипты писали, и то работало через раз.

возмжно в 18 версии что поменялось

Автор: MVJ May 2 2018, 08:21

Если в названии не было изменений, то и обновления не пройдет.

на самом деле задача не такая тривиальная. в свое время даже скрипты писали, и то работало через раз..

Вообще-то странно, мне казалось, что команды "Make Schematic Library" и "Make PCB Library" более всего нужны именно для описанного мною выше случая и если это не так, то для чего тогда они нужны?

Автор: Владимир May 2 2018, 08:51

Эти команды нужны для того, чтобы "вытянуть" библиотечные элементы из проекта, если исходных библиотек нет.

Потом их можно использовать как в этом, так и в других проектах

Автор: Spartak May 2 2018, 19:59

Если в названии не было изменений, то и обновления не пройдет.

на самом деле задача не такая тривиальная. в свое время даже скрипты писали, и то работало через раз.

возмжно в 18 версии что поменялось

Отключите в проекте при компиляции все лишние библиотеки.

Автор: Владимир May 2 2018, 20:10

Это не поможет.

1. В схеме: каждому компоненту в свойствах или через Tools/Footprint Manager указать требуемый Footprint из НУЖНОЙ библиотеки.

2. в PCB: После передачи изменений из схемы -- Tools/ Update From PCB library

Автор: peshkoff May 3 2018, 06:11

1. В схеме: каждому компоненту в свойствах или через Tools/Footprint Manager указать требуемый Footprint из НУЖНОЙ библиотеки.

2. в PCB: После передачи изменений из схемы -- Tools/ Update From PCB library

Все манипуляции обычно как раз для №2 и нужны, сперва нужную библиотеку установить в св-вах компонента, а потом можно делать Tools\Update from...

иначе не находит футпринт.

Автор: Saprx May 8 2018, 04:50

В одном проекте не работает команда Design View (при выборе области и вставке вида ничего не происходит), пробовал на разных машинах. В чем может быть загвоздка?

Автор: MiklPolikov May 8 2018, 10:24

Подскажите, как в правилах в языке запросов указать конкретный PAD ?

Например, я поставил на плату PAD и назвал его FREE-PAD-1 . Как указать его в правилах ?

Аналогичный вопрос про PAD в составе компонента.

Как сделать через класс падов - знаю. А просто через название пада ?

Заранее спасибо !

Автор: peshkoff May 8 2018, 10:32

Например, я поставил на плату PAD и назвал его FREE-PAD-1 . Как указать его в правилах ?

Аналогичный вопрос про PAD в составе компонента.

Как сделать через класс падов - знаю. А просто через название пада ?

Заранее спасибо !

(IsPad And (Name Like 'FREE-PAD-1'))

HasFootprintPad ('NameOfFootprint','NameOfPad')

Автор: MVJ May 11 2018, 09:11

Конвертация из DWG в step

Многие производители корпусов приборов выкладывают чертежи в формате DWG, например: http://electronix.ru/redirect.php?https://www.kradex.com.pl/shop?product=z67&lang=ru&session=618c67d898f51d7128f32726b34cb815

Хотел попробовать сделать 3D-модель для использования в AD14. Какую посоветуете программу (желательно бесплатную) для конвертации DWG в step для подобных задач? Или просто конвертацией здесь не обойдешься и нужна более серьезная программа?

Автор: DSIoffe May 11 2018, 12:31

Здравствуйте все!

Я раскрасил цепь: в панели PCB выбрал цепь, ПКМ и Change Net Color.

А как теперь убрать этот цвет? Если снять галку возле имени цепи, то контактные площадки обесцвечиваются, а связи так и остаются раскрашенными.

У меня AD 17.1.9.

Заранее признателен.

Автор: vGera May 14 2018, 12:10

F5 (меню Vew/net color override), и галки снимать не надо ![]()

Автор: DSIoffe May 14 2018, 12:47