Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Системы на ПЛИС - System on a Programmable Chip (SoPC) _ Свои процессоры

Автор: PVL Mar 12 2009, 19:51

Занимаюсь разработкой своего проца под SoC. Если есть предложения по системе команд и практической реализации пишем сюда.

Автор: SM Mar 12 2009, 19:58

Как классно поставлен вопрос ![]()

![]() Свои процы делаются для своих задач и исходя из каких-то своих требований. А не так вот - давайте, мол, все советуйте и систему команд, и реализацию. Хотя бы сказали, что это за процессор, какая архитектура в основе, и т.д.

Свои процы делаются для своих задач и исходя из каких-то своих требований. А не так вот - давайте, мол, все советуйте и систему команд, и реализацию. Хотя бы сказали, что это за процессор, какая архитектура в основе, и т.д.

Автор: PVL Mar 12 2009, 20:05

Сейчас видится МИСК архитектура. Арифметика целочисленная, под простую сигналку и ИО.

Автор: Methane Mar 12 2009, 20:13

Что такое МИСК?

Автор: PVL Mar 12 2009, 20:16

Почти тоже что РИСК только с бОльшим количеством рабочих регистров 256... 1024. Идеально для блочной памяти в ПЛИС.

Автор: Methane Mar 12 2009, 20:20

И тремя тактами на операцию?

Автор: PVL Mar 12 2009, 20:23

Не для сигналки можно и больше тактов, данные ведь независимые. Сейчас прикидываю конвейер на 8... 11 тактов. Затык с тем что разные инструкции имеют разное их число. Как райт бэк согласовывать.

Автор: Methane Mar 12 2009, 20:37

Как вы из регистрового файла, сразу несколько значений собираетесь вытаскивать за один такт?

Автор: PVL Mar 12 2009, 20:39

Не поверишь...

Автор: Methane Mar 12 2009, 20:49

А я и не заметил.

Пусть по две такта на команду. Или по одному но с аккумулятором. Ж)

Автор: PVL Mar 12 2009, 20:53

Пусть по две такта на команду. Или по одному но с аккумулятором. Ж)

На спартане 3Е при частоте 300 МГц за один такт ничего кроме логического И или пересылки не выполняется. Сложение 4 такта, умножение от 8 - ми. Деление пока совсем не фурычит. Плиске пришлось радиатор довесить - греется. Система команд пока не для записи во внешнюю память - аж 57 бит на инструкцию.

Автор: Methane Mar 12 2009, 21:02

Жуть Сартан, на 300, (это же типа циклона, только более убогого?) Я помню что циклона, первая, "в лоб" умножает 16х16 в 32 за 16 наносекунд умножает. Жуть.

Автор: des00 Mar 13 2009, 03:47

пройтись по этому форуму, только на моей памяти подобных пионерских тем около 5-6. В том числе я собирался заняться парой тем, но времени нет.

затем пройтись по опенкоресам, там много реализаций.

ЗЫ. на будующее учитесь писать компиляторы, отладчики и прочее

Автор: SM Mar 13 2009, 07:51

Угу, поддерживаю... У меня только порт бинутилсов занял полмесяца. А вот про С - даже думать боюсь.

Автор: Ynicky Mar 13 2009, 10:23

А у меня уже есть свой процессор. LCC осилил, а вот с ассемблером напряг.

По образованию я не программист, но приходится писать программы для отладки

железа. Нашел вот такой проект:

http://electronix.ru/redirect.php?http://sun.hasenbraten.de/vasm/index.php?view=source

Но из исходников собрать .exe не могу. Может кто поможет.

Поставил "Visual Studio 2008". Но с ней тоже надо разбираться.

У меня "Windows XP SP3".

Николай.

Автор: SM Mar 13 2009, 10:55

По образованию я не программист, но приходится писать программы для отладки

железа.

Мой совет, как уже прошедшего этот этап - берите binutils, и делайте на основе какого-то уже существующего там. Неделя на то, чтобы въехать, ну и неделя на то, чтобы свой сделать. Там, в бинутилс, "все для людей", т.е. добавить свою систему команд достаточно просто, при том, что сразу будут работать все фичи и объектного кода, и линковки.

Что интересно - я давал объявление на эту работу (за деньги), ни одного желающего не нашлось! Не то, что бы условия не устроили, а они были вполне щедрыми, а именно не было даже желающих!

Автор: Sefo Mar 13 2009, 11:40

Какой формат инструкции?

Автор: SM Mar 13 2009, 18:41

Ну почему же - расширить до 64 бит, и при шине внешней памяти шириной 128 и больше бит очень даже смотреться будет, выборка по паре или более инструкций за такт. Хотя лично я предпочитаю variable length, правда ведущую за собой серьезные усложнения декодера и схемы буфера предвыборки. (я так понял, что речь все таки в данном случае идет о суперпроизводительной числомолотилке, а не о CPU общего назначения, перекошенного под что-то конкретное)

Автор: PVL Mar 19 2009, 16:03

57 бит нужно ядру ,чтобы выполнить инструкцию. Типа откуда взять, как переключить мультиплексор разультата, как положить. С положить напряг - умноженеи и деление результат 64 бита, умножение 9 тактов, сложение 4, деление 12 кароче баги с конвейером.

Во первых систему команд, хочется уложить в 16 бит дабы не юзать БГА корпус. Народный проц хочу сделать.

Во вторых уже не просто числомолотилка поскольку есть спец узлы под фурье и вейвлет, на числомолотилке раз в 10 медленнее будет.

Шина 96 бит - читать шесть инструкций за такт дабы работать на СРАМ. С динамикой пока лениво связываться.

И вообще сейчас есть спартан 3Е - 500к. На нем не далеко уити от числомолотилки..

Автор: SM Mar 19 2009, 17:28

Автор: Harbour Mar 21 2009, 11:19

Не надо ля-ля, помню обьяву, просто был дико занят в тот момент

Автор: PVL Mar 24 2009, 14:54

Что такое binutils? Готовая среда для разработки С - компайлера? Где взять? Подскажите , а то сейчас с программерами сношаюсь - достали ![]()

Автор: Ynicky Mar 24 2009, 16:53

http://electronix.ru/redirect.php?http://ftp.gnu.org/gnu/binutils/binutils-2.19.1.tar.gz

Автор: SM Mar 24 2009, 19:13

нет, готовая среда для разработки С компайлера это gcc

Автор: Maverick Mar 25 2009, 06:29

А можно узнать как Вы делаете целочисленное деление за 12 тактов, наверное при разрядности данных 32 или 16.

Поделитесь пожалуйста алгоритмом, а лучше описанием на VHDL (идеальный вариант

а не подскажите где можно взять готовую среду - gcc?

Автор: SM Mar 25 2009, 08:33

Поделитесь пожалуйста алгоритмом, а лучше описанием на VHDL (идеальный вариант

А в чем вопрос-то? Например деление за два такта делается при помощи комбинаторного "полуделителя", который при N-битном входе дает N/2-битное частное и N-битный остаток. Деление за 3 такта - "третьделителя" - соотв N/3 и N. Ну и так далее.

вот пример полнофункционального делителя, который делит 8/8 бит за 1 такт, а 16/16 бит за два такта, с поддержкой дробного деления и чисел со знаком.

input [15:0] num; // numerator

input [15:0] den; // denominator

output [15:0] quot; // quotient

output [15:0] rem; // remainder

output divz, n_out; // divide-by-zero & sign bits

input m16, sn, sd, frct, n_in, cycle, clock; // 8/16_mode, numerator_signed, denominator_signed, fractional/normal, sign_from_PSW, cpu_cycle_#, clock

wire [15:0] int_den, int_num, int_quot, ext_num, ext_den, int_rem;

wire nsgn, dsgn, qsgn;

assign nsgn = sn & (m16 ? num[15] : num[7]);

assign dsgn = sd & (m16 ? den[15] : den[7]);

assign qsgn = nsgn ^ dsgn;

assign ext_num = m16 ? num : { {8{nsgn}}, num[7:0]};

assign ext_den = m16 ? den : { {8{dsgn}}, den[7:0]};

assign int_num = (ext_num ^ {16{nsgn}}) + nsgn;

assign int_den = (ext_den ^ {16{dsgn}}) + dsgn;

assign divz = !(|int_den);

wire en_frct = frct & (int_num < int_den); // fractional mode only if |num| < |den|

wire numz = !(|int_num);

reg [3:0] i;

reg [16:0] temp;

reg [15:0] save_rem;

reg [17:0] temp1;

reg [7:0] out, save_out;

always @*

begin

temp = cycle ? {save_rem, int_num[7] & !(en_frct)} :

(en_frct ? {int_num, 1'b0} : {16'h0000,int_num[m16?15:7]});

for (i=0; i<8; i = i+1'b1)

begin

temp1 = temp - int_den;

out[7-i] = !temp1[17];

if (i != 7) temp = {(temp1[17] ? temp[15:0] : temp1[15:0]), int_num[(cycle | !m16) ? (6-i) : (14-i)] & !(en_frct)};

else temp = {1'b0, (temp1[17] ? temp[15:0] : temp1[15:0])};

end

end

always @(posedge clock)

if (!cycle) save_rem <= temp[15:0];

always @(posedge clock)

if (!cycle) save_out <= out;

assign int_quot = {save_out, out};

assign int_rem = temp[15:0];

// sign of remaider :

// sign of remainder is equal to sign of numerator.

assign rem = (int_rem ^ {16{nsgn}}) + nsgn;

// sign of quotient :

// fractional mode - quotient always positive

// integer mode - quotient has sign of den*num

wire t_qsgn = qsgn & !frct;

assign quot = (int_quot ^ {16{t_qsgn}}) + t_qsgn;

// sign output:

// fractional mode - if numerator not zero, put sign into N

// integer mode - put sign into N

assign n_out = (!numz | !frct) ? qsgn : n_in;

endmodule

ну как бы gcc.gnu.org

Автор: yes Mar 25 2009, 18:01

я всегда думал, что MISC это minimal instruction ...

то есть по русски - безоперандный (или стековый) комп

http://electronix.ru/redirect.php?http://en.wikipedia.org/wiki/Minimal_instruction_set_computer

(кстати там по ссылке есть и OISC one ... - имхо, cool)

примеры таких - всякие лисп/форт/жава компутеры

для ПЛИС есть ZPU (имхо, интересно, но мне не увы нужно)

http://electronix.ru/redirect.php?http://www.zylin.com/zpu.htm

Автор: PVL Mar 29 2009, 15:34

то есть по русски - безоперандный (или стековый) комп

http://electronix.ru/redirect.php?http://en.wikipedia.org/wiki/Minimal_instruction_set_computer

(кстати там по ссылке есть и OISC one ... - имхо, cool)

примеры таких - всякие лисп/форт/жава компутеры

для ПЛИС есть ZPU (имхо, интересно, но мне не увы нужно)

http://electronix.ru/redirect.php?http://www.zylin.com/zpu.htm

Это ЛАЖА ,а не процессор. 300 ЛУТ таблиц 95 МГц. ААААхренеть производительность. У меня без нагрева шарашит на 240 МГц комерческий Спартан 3е работает. Индустриальные добегают до 300... 350 или 200 МГц на -40 градусов цельсия. Правда ПЛИС на 500 к ушла вся.

Автор: yes Mar 30 2009, 10:35

а что С++ и eCos у Вас работают?

имхо, не надо путать теплое с мягким - написать стэйтмашинку которая работает на спартане это одно (у меня в прошлом проекте автоматом вышло ~200МГц без каких-либо усилий с моей стороны), а написать процессор, который можно применять для процессорных задач (то есть компилятор, ОСь и т.п.) это совершенно другой уровень задачи

Автор: Ynicky Jun 13 2009, 11:04

Чтобы не плодить новую тему, напишу сдесь. Если, конечно, автор темы не против.

Недавно прикрепили ко мне студента, а так как в связи с кризисом и мне то делать

особо нечего, то чего уж говорить про бедного студента. Поэтому решил ему дать

интересную тему (с моей точки зрения) для обучения разработке soc проектов

со встроенным процессорным ядром (чем собственно я и занимаюсь).

За основу взяли студенческое risc ядро, описанное в книге Сергиенко А.М.

“VHDL для проектирования вычислительных устройств”. Систему команд и архитектуру

немного доработали. Сделали простенький soc проект в Active-HDL81 для FPGA ф.Actel.

Его, собственно, и предлагаю для повторения всеми желающими. С некоторыми доработками

его можно реализовать и для других FPGA. Пока, для простоты,

пзу команд сделали в виде vhdl. Хотелось бы общими усилиями протестировать

процессорное ядро. Да и может кому пригодится. Оговорюсь сразу, проект сырой.

Поэтому будут исправления и доработки. Может у кого будут дельные предложения.

Готов рассмотреть. Краткое описание процессора можно найти в Директории "Doc".

Ассемблер - в директории "st16asm". Я его делал в "Microsoft Visual Studio 2008".

Еще не разобрался, как сделать, чтобы ".exe" файл запускался на других компьютерах,

где нет MSVC2008 (не программист). Компилятор сделаю попозже, после отработки

системы команд. Это будет LCC, так как есть уже опыт написания

"machine description" файлов под свою систему команд. Ну вот, собственно, пока все.

Будут вопросы, задавайте.

Николай.

Автор: Ynicky Jun 14 2009, 14:30

Выкладываю новую версию проекта.

Просьба сообщить, работает ли ассемблер у кого нет "Microsoft Visual Studio".

Николай.

Автор: Leka Jun 14 2009, 18:27

Команды Break и LU - что делают?

И зачем выделенный регистр SP (при отсутствии команд push/pop и аппаратном стеке возвратов)?

Автор: Ynicky Jun 14 2009, 19:02

И зачем выделенный регистр SP (при отсутствии команд push/pop и аппаратном стеке возвратов)?

LU - Load Byte Unsigned. Беззнаковая загрузка байта.

Команда Break нужна только при отладке ПО с помощью внутрисхемного эмулятора, если память программ является оперативной. Вместо команды на которой ставится точка останова заносится Break. При дальнейшем пуске Break заменяется обратно на штатную команду. Если память программ - ПЗУ, то точки останова прописываются через JTAG в специальный регистр внутрисхемного эмулятора. С помощью аппаратного компаратора сравнивается текущий адрес команды и адрес точки останова. При совпадении происходит остановка процессора. Через JTAG процессор можно снова запустить, блокировав сигнал с компаратора на один период тактовой частоты процессора.

Регистр SP - это регистр общего назначения, используемый программой в качестве указателя на стек данных.

Николай.

Автор: Leka Jun 14 2009, 19:39

Работает.

Автор: des00 Jun 15 2009, 02:59

для тех кто альдеком не пользуется, могли бы и vhd файл из risc_cpu.bde сгенерировать, делов то на минуту

зачем "По сигналу RESET разряды всех регистров обнуляются." вот это сделали ? это сразу режет вам крылья, при использовании на хилой платформе + файл rfile.vhd -> R_RF4:process(CLK,RST,data_w,rfsel) вот вас прибило каждый регистр ручками описывать %)))

в файле tst_alu.asm есть такой код

lea r5,0x0

но в доке Doc\to101st16.doc

команды lea нет.

Автор: Ynicky Jun 15 2009, 06:42

зачем "По сигналу RESET разряды всех регистров обнуляются." вот это сделали ? это сразу режет вам крылья, при использовании на хилой платформе + файл rfile.vhd -> R_RF4:process(CLK,RST,data_w,rfsel) вот вас прибило каждый регистр ручками описывать %)))

в файле tst_alu.asm есть такой код

lea r5,0x0

но в доке Doc\to101st16.doc

команды lea нет.

1. Эти файлы генерятся автоматически при каждой компиляции и находятся в директории compile.

2. Виноват, соврал. При использовании в качестве регистрового файла внутренней памяти исходное значение берется из файлов инициализации (r8x256_M0.mem). rfile.vhd - как пример на регистрах.

3. lea - Load Effective Address. Это псевдокоманда для занесения в регистры констант.

lea r5,0xFF00 преобразуется ассемблером в

imm 0xFF00

addi r5,r0,0

Но можно писать и как в tst_alu.asm.

Если успею, вечером добавлю в описание.

Николай.

Автор: SFx Jun 15 2009, 07:34

смотрите файлы из архива, они как раз вам и нужны

risc_st.rar\risc_st\risc_st_core\compile\risc_st_core.vhd

risc_st.rar\risc_st\risc_st_core\compile\risc_sync.vhd

З.Ы. пардон, страницу не обновил....

Автор: Ynicky Jun 15 2009, 17:13

Исправили ошибки загрузки/выгрузки.

Николай.

Автор: Ynicky Jun 17 2009, 15:07

Подкорректировали проект.

Проверили прерывания.

Дополнил описание.

В принципе проект "готов".

Осталось доделать внутрисхемный эмулятор для работы с отладчиком (программа на PC).

Николай.

Автор: Ynicky Jul 1 2009, 05:52

Написали JTAG на vhdl, чтобы можно было проект зашить в другие FPGA (останется поменять ОЗУ).

Отмоделировали команды (stop, step, run) внутрисхемного эмулятора.

Подработал ассемблер.

Написал еще несколько тестовых программок.

Проверили в железе работу с семисегментным индикатором.

Николай.

Автор: Ynicky Jul 8 2009, 07:06

Добавили 2 блока к внутрисхемному эмулятору.

Отмоделировали чтение памяти команд и данных в режиме отладки.

Остальное - после отпуска.

Николай.

Автор: Ynicky Sep 10 2009, 18:18

Добавили блок чтения регистрового файла в режиме отладки.

Николай.

Автор: kuchynski Oct 16 2009, 06:37

Пользуюсь своим процессором 5 год, за это время и отладил до безглючности. Работает на Xilinx.

Из плюсов:

язык форт, встроенные uart, фильтры с плавающей точкой, делители, разрядность до 32 бит с/без знака, переменное число поддерживаемых команд.

Из минусов:

средний текстовый редактор, недописанный отладчик, полностью отсутствует описание.

Автор: Aner Oct 16 2009, 09:58

Из плюсов:

язык форт, встроенные uart, фильтры с плавающей точкой, делители, разрядность до 32 бит с/без знака, переменное число поддерживаемых команд.

Из минусов:

средний текстовый редактор, недописанный отладчик, полностью отсутствует описание.

респект и уважение за такое.

Хотелось узнать следующее из плюсов/ минусов:

Тактовая, производительность в ~мипсах для математики, если подсчитывали.

Если сравнить с имеющимися ARM_ами то вот к какому ближе (по архитектуре) и есть ли преимущество и в чем?

По потреблению наверное проигрыш. Насколько хорош компилятор из форта получился?

Дебагер тоже наверное медленный, не реалтайм. С описанием понимаю вас, такое часто бывает. Поскольку требует много времени.

Автор: kuchynski Oct 21 2009, 09:10

Если сравнить с имеющимися ARM_ами то вот к какому ближе (по архитектуре) и есть ли преимущество и в чем?

По потреблению наверное проигрыш. Насколько хорош компилятор из форта получился?

Дебагер тоже наверное медленный, не реалтайм.

Несколько лет назад таких ARM не было, сейчас не знаю. Основное преимущество - переменная разрядность, требуеться 23 разряда - будет 23-х разрядный проц, знаковый бит не надо - убираем, лишнего в микросхеме никто не возмёт.

Все операции(кроме деления, фильтра) выполняются за один такт, работает на 48 Мгц на XC3S400-4PQ208C при 20 разрядах ядра, больше просто не подавал.

Форт хорош тем, что: 1. небольшой код программы(отсутствует поле адреса регистра); 2. при прерываниях не нужно сохранять ни одного регистра; 3. более высокий уровень письма, чем у ассемблера, поскольку компилятор самоделанный, писать можно в буквальном смысле на русском языке.

Дебагер - отстой, не пользуюсь.

и не для кого его писать! Похвастался здесь и хорошо, платят совсем за другое.

Автор: OverDrewk Oct 23 2009, 04:57

По образованию я не программист, но приходится писать программы для отладки

железа. Нашел вот такой проект:

http://electronix.ru/redirect.php?http://sun.hasenbraten.de/vasm/index.php?view=source

Но из исходников собрать .exe не могу. Может кто поможет.

Поставил "Visual Studio 2008". Но с ней тоже надо разбираться.

У меня "Windows XP SP3".

Николай.

Смотри инструкцию, под Windows может и не соберешь. Исходя из содержимого vasm.tar.gz по данному линку надо ставить Linux, ну или minGW(под Windows) и собирать проект. Инструкция http://electronix.ru/redirect.php?http://sun.hasenbraten.de/vasm/index.php?view=compile

Автор: Ynicky Oct 23 2009, 16:07

Пошел по пути наименьшего сопротивления. Переделал свой процессор на MIPS32,

т.к. изначально делал его под эту архитектуру.

Поставил SDE v6. И теперь не знаю проблем ни с С ни с ASM-ом.

Единственное разочарование - не своя система команд.

Николай.

Автор: Leka Oct 23 2009, 17:32

Ну и каковы результаты синтеза?

Автор: Ynicky Oct 23 2009, 19:27

Пока не доделал блок MDU (multiply divide unit), поэтому результат синтеза без него.

Николай.

Автор: Leka Oct 23 2009, 20:26

~2K LUT - немного по сравнению с LEON/OpenRISC/Cortex-M и тп.

Без внешней памяти получится запустить что-либо дельное, написанное на Си?

Автор: Ynicky Oct 23 2009, 20:39

Так это только ядро. Без кэш программ и данных. Без FPU.

Я в свое время синтезил leon2, точные цифры не помню, но сравнивал со своим процессором.

Результаты были не в мою пользу. Но у меня было много мультимедийных инструкций.

Николай.

Эту версию (MIPS32) еще не применял в серьезных разработках.

Но предыдущий процессор используется в MP3 камкордере со встроенной памятью

128 кБ ПЗУ программ и 64кБ ОЗУ программ/данных (правда в ASIC-е на 0,18мкм).

Николай.

Автор: Leka Oct 23 2009, 20:45

Вот и спрашиваю, можно каким Си-компилятором создавать более-менее практичные приложения для системы с несколькими Кбайтами памяти(те без внешней памяти).

Для FPGA, не для ASIC.

Автор: Ynicky Oct 23 2009, 20:47

Можно, например WEB камера (без звука, в системах безопасности) на основе камкордера занимает у меня 32 кБ кода, написанного на С.

А FPGA - это промежуточная стадия перед ASIC-ом.

Николай.

Автор: Leka Oct 23 2009, 21:20

Значит все-таки для ASIC. Для FPGA и 8КБ памяти м/б максимумом (для кода+данные).

Автор: flipflop Dec 5 2009, 14:19

Кто-нибудь реализовал MMU? Поделитесь опытом.

Не совсем понятно, как его реализовать таким образом, чтобы чтение и запись из памяти проходило за один такт (не хочется отходить от классической схемы 5-6 ступенчатого конвейера).

Автор: Ynicky Dec 6 2009, 09:41

Не совсем понятно, как его реализовать таким образом, чтобы чтение и запись из памяти проходило за один такт (не хочется отходить от классической схемы 5-6 ступенчатого конвейера).

А что значит за один такт?

Если обращение происходит к внутренней памяти малого объема (например к встроенной в FPGA)

или к кеш первого уровня (также малого объема) то это можно сделать и за один такт.

Если Вам надо обратиться к дальней памяти или кеш второго уровня (например для заполнения кеш первого уровня),

то в этом случае нужна остановка процессора (stall). А количество тактов в конвейере тут не причем.

Николай.

Автор: flipflop Dec 6 2009, 10:27

Если обращение происходит к внутренней памяти малого объема (например к встроенной в FPGA)

или к кеш первого уровня (также малого объема) то это можно сделать и за один такт.

Если Вам надо обратиться к дальней памяти или кеш второго уровня (например для заполнения кеш первого уровня),

то в этом случае нужна остановка процессора (stall). А количество тактов в конвейере тут не причем.

Николай.

Это понятно. Рассматриваем только кэш первого уровня: все равно, получается так, что выборка команды и доступ к памяти данных тянет за собой всю производительность.

У меня 32-разрядный RISC (load/store) процессор, целевая микросхема Spartan-3AN (XC3S700AN-FG484):

1) Какую память использовать для кэша: блочную или распределенную?

2) Какой уровень ассоциативности/размер тэга оптимален?

3) Есть ли смысл (с точки зрения производительности) разбить выборку команды и доступ к памяти на 2 ступени? Выигрыш в частоте вполне реален, но конвейер становиться на 2 ступени длиннее, причем одна из них всегда работает в холостую.

Автор: Ynicky Dec 6 2009, 12:45

В моем последнем процессоре как раз это и используется.

Команды ветвления при этом имеют два слота задержки, но я на это пошел,

так как только используя слоты можно не потерять в производительности.

Только приходится критичный код править в ассемблере, т.е. переставлять команды,

т.к. компилятор не может это сделать сам.

Еще я сделал флаг в командах ветвления для аннулирования слотов задержки.

Это позволяет немного сократить код (не надо в пустые слоты добавлять nop).

Но этим я пользуюсь редко.

Так же и с данными. Если результат загрузки регистра не используется в следующих

командах, то процессор не останавливается.

Но при этом также, в большинстве случаев, требуется правка кода вручную.

Что касается первых двух пунктов, то оптимальный результат может дать только перебор различных комбинаций.

Николай.

Автор: flipflop Dec 6 2009, 12:54

Команды ветвления при этом имеют два слота задержки, но я на это пошел,

так как только используя слоты можно не потерять в производительности.

Только приходится критичный код править в ассемблере, т.е. переставлять команды,

т.к. компилятор не может это сделать сам.

...

Что касается первых двух пунктов, то оптимальный результат может дать только перебор различных комбинаций.

Николай.

Ясно, значит я все правильно понимаю и проблемы вполне реальные .

Если не секрет, какой частоты и на каком кристалле вам удалось добиться?

Автор: Ynicky Dec 6 2009, 13:06

Если не секрет, какой частоты и на каком кристалле вам удалось добиться?

В ASIC-е на 0,18 - 250 МГц.

Но там много мультимедийных инструкций, тормозящих процессор.

Николай.

Автор: flipflop Dec 6 2009, 13:21

Но там много мультимедийных инструкций, тормозящих процессор.

Николай.

Ого, а где вы их производите?

Автор: Ynicky Dec 6 2009, 13:34

Ну не в России же.

Николай.

Автор: Ynicky May 23 2010, 16:56

Перешел в тему "Свои процессоры" из "Цифровой видеокамеры".

Предлагается всем поучаствовать в обсуждении открытого RISC процессора

с большим регистровым файлом. Выкладываю краткое описание процессора.

Пока не охвачена тема доступа к специализированным регистрам, т.е

формат команд для доступа к ним. Какие еще нужны (frame pointer, variable pointer)?

По мере устаканивания архитектуры и системы команд, буду

выкладывать проект на VHDL.

Николай.

Автор: Leka May 24 2010, 21:01

Я бы упростил систему команд, все-таки большинству ASIC недоступен, и упор лучше делать на достижение приемлемых характеристик в FPGA.

В "своих процессорах" до сих пор самой сложной задачей являлся софт, так что конкретно обсудить архитектуру лучше после первых версий компилятора с "ассемблерного Си" (начал делать).

Мой ник лучше убрать из титульного листа, тк не автор данной архитектуры, и VHDL не знаю. У меня архитектура другая - нет типов, нет флагов АЛУ, и тд.

Автор: Ynicky May 25 2010, 05:43

Я как раз и собираюсь "пощупать" процессор в FPGA.

Хотя это будет Virtex5 (на работе отдаю новую схему пп для разводки). Туда много чего влезет.

Планирую одну такую платку взять домой на время.

Но можно и попроще.

А как можно сделать if...else без флагов?

Можно, конечно, сделать команды "branch" (BR) без CMP так:

BR if RD = 0, RD /= 0, RD < 0, RD >= 0 и т.д.

Хотя это теже флаги без сохранения в регистре.

Но при этом смещение будет в 12 разрядов или в 32 разряда с предварительной командой IMM.

Николай.

Автор: =AK= May 25 2010, 07:26

1. RISC неэффективно расходует память программ

2. Большой регистровый файл - значит, контекст сохранять долго. Значит, на прерывания медленно будет реагировать.

А кто компилятор будет делать под такую архитектуру? Или предполагается его на ассемблере мутузить?

Автор: Leka May 25 2010, 08:01

Пример бесфлагового процессора - NIOS II, даже переноса нет.

А зачем сохранять контекст? Все переменные подпрограммы прерывания - статические. Если нужна реентрабельность - свой собственный статический стек.

Для начала - "ассемблерное" подмножество Си (см пример "N-ферзей" в предыдущей ветке), потом расширяем компилируемое подмножество.

Автор: Ynicky May 25 2010, 11:12

Мой опыт в проектировании процессоров говорит, что надо начинать проверку с условных команд

ветвления (BR) и конвейера обработки данных. Так что желательно сейчас сосредоточиться

на этих командах. Если бы места в коде команд хватило бы на 2 регистра и смещение, то я бы

сделал команды условных ветвлений как в NIOSII и MIPS32.

Николай.

Автор: Ynicky May 25 2010, 15:21

Начал делать АЛУ и сразу возникла мысль: в операциях формата RI

поменять местами RD и RS. Тогда получим:

RR: RD = RD opalu RS (пример на ассемблере: add rd,rs)

RI: RD = RS opalu IMM (пример на ассемблере: addi rd,rs,imm)

При этом в формате RI регистр-источник и регистр-приемник могут быть разными.

To Leka: это не усложнит компилятор?

Николай.

Автор: Leka May 25 2010, 17:45

Не усложнит.

Автор: Leka May 25 2010, 21:47

Проблема вот в чем.

На уровне "ассемблерного" Си нет оптимизации, поэтому для 2х- и 3х- операндных архитектур запись одного и того-же алгоритма д/б различной для достижения оптимума по объему кода и быстродействию.

На примере кода N-ферзей.

Если для 3х-операндной архитектуры оптимально использование индексных массивов "arow[pos]", "arow[pos1]", и тд, то для 2х-операндной архитектуры оптимальнее будет использование модифицируемых указателей "*arow", "*arow1", и тд. Тк одной 3х-операндной инструкции:

arow[pos1] = temp;

непосредственно соответствуют три 2х-операндные инструкции:

tmp = arow;

tmp += pos1;

*tmp = temp;

Ветвления:

"if( pos != N )..." - одна бесфлаговая 3х-операндная инструкция, или

"if( pos - N != 0 )..." - две флаговые 2х-операндные инструкции (сравнение + ветвление), или

"if( tmp=pos, tmp -= N, tmp != 0 )..." - три бесфлаговые 2х-операндные инструкции.

Пришел к выводу, что используемое "ассемблерное" подмножество Си д/б жестко привязано к целевой архитектуре, те все преобразования выражений вынести из уровня компиляции:

"ассемблерное" подмножество Си --> машинные коды,

на уровень компиляции:

к-л подмножество Си --> "ассемблерное" подмножество Си.

На код самого компилятора ("ассемблерное" подмножество Си --> машинные коды) это слабо повлияет, тк все особенности архитектуры предполагаю вынести во внешние таблицы(файлы) - делаю универсальным, чтобы и для своих процессоров использовать.

Автор: =AK= May 26 2010, 07:43

Для того, чтобы обработку прерывания делать на С. И для того, чтобы более высокоприоритетное прерывание могло прервать низкоприоритетное (это не совсем реентерабельность).

А если свой собственный стек - что в нем сохранять-то? Все регистры - слишком долго, веть их же много. А если запретить использовать все, то на фиг их надо было делать много?

Две страницы регистров - отдельно для "нормальной" работы, отдельно для прерываний - выглядит более прогрессивным решением, чем просто много регистров. Еще больше страниц регистров, которые бы образовали стековую структуру, выглядит еще более заманчивым. А на каждой странице много регистров не нужно.

Ссылочку приведите

Автор: Leka May 26 2010, 08:28

Если регистры не используются одновременно разными подпрограммами, то сохранять их не нужно. Если регистров много - их можно без конфликтов распределить по подпрограммам, и сохранять ничего не придется.

Прерывания в процессоре с 1К регистров у меня реализованы, пишутся на "автокоде"( http://electronix.ru/forum/index.php?showtopic=52166&st=120&p=605442&#entry605442 ), никаких потерь на входе/выходе.

"Ассемблерный" Си для 3х-операндной архитектуры: http://electronix.ru/forum/index.php?showtopic=76026&view=findpost&p=760789

Автор: =AK= May 26 2010, 11:14

Если вы пишете на ассемблере и вручную распределяете регистры и задаете их использование, то не нужно. Да, еще одно условие: вы не используете подпрограмм. Вся ваша программа должна быть написана как линейный "спагетти" код на ассемблере, это обязательное условие, чтобы не сохранять регистры.

Автор: Leka May 26 2010, 12:36

Из:

int

count,

arow[20],

...

автоматически создается:

queens_return;

queens_N;

queens_count,

queens_arow[20],

...

queens(){

...

с соответствующим переименованием всех переменных.

Все переменные стали глобальными, вызов "cnt=queens(8);" преобразуется в:

queens();

cnt=queens_return;

И так для всех подпрограмм.

Если не хватит ~1К адресного пространства для всех таких переменных, тогда только и придется организовывать программное сохранение/восстановление контеста, и тп - для некритичного кода. И вовсе не обязательно сохранять/восстанвливать весь регистровый файл. Имхо, очень удобно для небольших систем без монстроидальных ОС.

Автор: =AK= May 26 2010, 12:46

...

И так для всех подпрограмм.

Я в одной подпрограмме вызову другую, а она пропишет свои временные переменные поверх задействованных. Вот и придется вам весь код раскатать в плоский "блин", без подпрограмм (функций). Или же строго следить за "уровнем": main может использовать одни переменные, подпрограммы первого уровня (их можно вызывать только из main) - другие, подпрограммы второго уровня - свой набор, и т.п. Маразм, короче. Архаическое программирование в стиле старых PIC-ов на ассемблере.

Автор: Leka May 26 2010, 13:11

А нету временных переменных. Как после:

#define int static int

и тп.

Проверено на практике на "автокоде" - подпрограммы из подпрограмм вызываются без к-л ограничений, прерывания тоже работают.

Автор: Ynicky May 26 2010, 17:40

Может я, конечно, чего не понимаю.

Я пока не задавал глупых вопросов про служебные регистры, потому что думал рано. Но их в систему команд все равно придется вводить. К ним я планировал добавить "frame pointer" или как его там назвать. Компилятор знает сколько регистров надо зарезервировать для подпрограммы. При вызове подпрограммы во "frame pointer" записывается это значение (или добавляется к его содержимому). А дальше адрес регистров вычисляется в аппаратуре прибавлением текущего адреса к "frame pointer".

При выходе из подпрограммы - вычитать это значение.

Но что делать, если "frame pointer" перешагнет через максимальное число регистров? Тут я могу завести это событие на NMI или вызвать TRAP. Поправьте, если что-то недопонял.

Николай.

Автор: Leka May 26 2010, 19:59

потому что думал рано. Но их в систему команд все равно

придется вводить. К ним я планировал добавить "frame pointer"

или как его там назвать...

Тогда регистры придется делить на локальные и глобальные, и делать мультиплексор(или что другое) на входе адреса. И сразу делать 3х-операндную архитектуру, тк для 2х-операндной такое не имеет смысла, имхо.

Как обращаться к служебным регистрам из Си - еще не решил, важно обеспечить простоту отладки "ассемблерного" Си-кода на ПК со стандартным Си-компилятором (сам использую открытый Tiny C Compiler). Предлагайте варианты.

http://electronix.ru/redirect.php?http://ru.wikipedia.org/wiki/Tiny_C_Compiler

Автор: Leka May 27 2010, 05:04

Гораздо проще придумать свой язык и компилятор к нему, чем делать компилятор к Си.

Масса вопросов типа:

В каком порядке будут вызываться функции a(), b(), c(), и почему?

Автор: Leka May 27 2010, 08:08

Вся система команд с учетом архитектуры будет описываться в отдельном файле, в таком примерно формате:

001 01000 dddddddddddd ssssssssssss

dddddddddddd += kkkkkkkkkkkk

010 01000 kkkkkkkkkkkk dddddddddddd

dddddddddddd += hhhhhhhhhhhhhhhhhhhhkkkkkkkkkkkk

000 00101 xxxxhhhhhhhh hhhhhhhhhhhh

010 01000 kkkkkkkkkkkk dddddddddddd

* ssssssssssss = dddddddddddd

011 xx110 dddddddddddd ssssssssssss

dddddddddddd = * ssssssssssss

011 xx010 dddddddddddd ssssssssssss

dddddddddddd < ssssssssssss

001 00110 dddddddddddd ssssssssssss

110 x0100 pppppppppppp pppppppppppp

...

Это избавит от необходимости переделывать компилятор с "ассемблерного" Си при изменениях в архитектуре (система и разрядность команд, число операндов, регистров, ...).

Автор: =AK= May 27 2010, 08:59

Насколько мне известно, типичная программа на С в основном использует как раз таки временные переменные. Глобальных в программах немного, зато чуть не в каждой функции - несколько локальных: счетчик цикла, промежуточные результаты, и т.п. Вы предлагаете процессор, при использовании которого временных переменных вообще нет, все они сделаны глобальными. Соответственно, программы потребуют в несколько раз больше памяти данных. То есть, мало того, что ваш процессор неэффективен по использованию памяти программ (поскольку RISC), он, оказывается, и память данных (регистры) транжирит. По-моему, от таких архитектур давным-давно отказались, как от неэффективных.

Я, кстати, свои первые программы писал для машины с 45-разрядными словами и 3-адресными командами. БЭСМ-4 называлась, чудо техники начала 60-х. Дежавю.

Автор: Ynicky May 27 2010, 09:21

Как обращаться к служебным регистрам из Си - еще не решил, важно обеспечить простоту отладки "ассемблерного" Си-кода на ПК со стандартным Си-компилятором (сам использую открытый Tiny C Compiler). Предлагайте варианты.

Вообще то лучше сделать служебные регистры в виде сопроцессора как в MIPS32,

и доступ к ним организовать через команды mtcp (move to coprocessor) и mfcp (move from coprocessor).

А что касается компиляторов, то я дело имел только с LCC.

И еще, меня никто не поправил насчет нового формата RI.

Тут я ошибся (сказывается опыт работы с 3-х операндными командами).

Для регистров есть только одно поле в команде, так что 2 регистра и смещение не могут быть

в одной команде 2-х операндных инструкций.

Описание нужно вернуть к версии 1.0.0.

Николай.

Вы, наверно, имеете в виду процессоры с фиксированной длиной команд, а не RISC.

Есть RISC-и с переменной длиной команд, где код используется эффективно.

Но это (фиксированная длина команд) окупается простотой реализации.

Николай.

Автор: Leka May 27 2010, 09:31

На проценты, а не в разы, тк память данных - не только простые переменные и указатели, но и массивы, и в большинстве полезных программ основной объем данных приходится на массивы. А массивы хранятся не в регистровом файле.

В ветке, где приводил пример программы N-ферзей на автокоде, предлагал сравнить эффективность архитектур на разных софт-процессорах - никто не откликнулся.

Эффективность использования памяти программ гораздо сильнее зависит от качества кода, чем от разрядности команд. Пример - Tiny C Compiler, 100Кб кода против десятков Мб от других разработчиков.

Удачное разбиение кода на маленькие подпрограммы - самый эффективный способ сжать код, поэтому важны малые издержки на вызовы пп. Например, у меня команда call совмещена с пересылкой регистр-регистр, а ret - c любой операцией алу:

f(&a); - одна инструкция на вызов пп с передачей аргумента,

f(int *a){ return *a >>= 8; } - одна инструкция на всю пп.

Автор: =AK= May 27 2010, 10:04

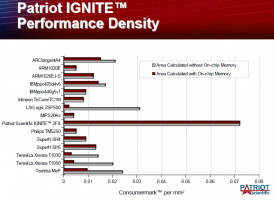

Есть специальная контора, которая сравнивает - http://electronix.ru/redirect.php?http://www.eembc.org/ Бенчмарки, приведенные в http://electronix.ru/redirect.php?http://www.ptsc.com/documentation/PTSC_Presentation.pdf, меня лично вполне убедили, что с большим отрывом лидирует стековая архитектура

Автор: Leka May 27 2010, 12:19

Презентации - неинтересно.

Первая попавшаяся нерекламная ссылка по IGNITE: http://electronix.ru/redirect.php?http://java.epicentertech.com/Archive_Embedded/Patriot_Scientific/Ignite%20Processor%20-%20Java/

Автор: Ynicky May 30 2010, 07:15

Ну вот, выкладываю первую версию процессора.

Проект сделан в ACTIVE-HDL 8.2. На нем проще моделировать.

На конечном этапе сделаю в ISE для Xilinx и в QuartusII для альтеры.

Память программ и регистровый файл сделал пока поведенческими для быстроты моделирования.

Программу проверки пишу в кодах (файл prg.txt). Оказалось не очень нудно,

т.к. простые форматы команд. Отладил почти все условия ветвления в командах BRcc.

АЛУ полностью пока не проверял (только частично в тестах BRcc).

To Leka: В принципе, можно уже моделировать программу N-ферзей.

Хорошо бы компилятор мог на выходе записывать текстовый файл (как prg.txt).

Но это не обязательно. Я, наверно, смогу сам преобразовать из других форматов.

И еще: В директории doc находится новая версия описания RF32.

Николай.

Автор: des00 May 30 2010, 10:32

Спасибо конечно, но вот те кто не пользуются альедеком должны вытаскивать структуру из скомпилированного bdf файла? Это я к тому что структурная и функциональная схема не помешали бы, также как и описание портов ввода/вывода процессора %)

Автор: Leka May 31 2010, 22:17

На этой неделе постараюсь выложить первую версию компилятора. Отвлекают вопросы методического характера, например: Си ориентирован на явное использование указателей --> получается неудобно для архитектуры с большим регистровым файлом, тк указатели нельзя применять к регистрам...

Нужна еще память данных для массивов, косвенно адресуемых LOAD/STORE.

Автор: Ynicky Jun 1 2010, 05:56

На днях сделаю.

Учту.

Автор: Leka Jun 1 2010, 22:29

Чтобы проще было вылавливать ошибки в компиляторе с "ассемблерного" подмножества Си, решил добавить промежуточный уровень "машинного" подмножества Си:

... --> "ассемблерный" Си --> "машинный" Си --> машинные коды.

Пример: N-ферзей на "машинном" Си для 3х-операндной архитектуры без типов,

main() - тестовая программа на Си - игноируется компилятором в машинные коды по пробелу в начале строки.

R2;

R3[20];

R4[20];

R5[20];

R6[20];

R7;

R8;

R9;

R10;

R11;

R12;

R13;

R14;

queens(){

L1:R2=0;

L2:R12=R1&1;

L3:R13=1<<R1;

L4:R9=R13-1;

L5:R13=R1>>1;

L6:R7=R9>>R13;

L7:R3[1]=0;

L8:R4[1]=0;

L9:R5[1]=0;

L10:R6[1]=R7;

L11:R10=1;

L12:if(R7==0)goto L46;

L13:R13=0-R7;

L14:R8=R7&R13;

L15:R13=-1-R8;

L16:R7=R7&R13;

L17:if(R10!=R12)goto L20;

L18:if(R7!=0)goto L20;

L19:R2=R2<<1;

L20:if(R10==R1)goto L44;

L21:R11=R10+1;

L22:R6[R10]=R7;

L23:R13=R3[R10];

L24:R13=R13|R8;

L25:R3[R11]=R13;

L26:R13=R4[R10];

L27:R13=R13|R8;

L28:R13=R13<<1;

L29:R4[R11]=R13;

L30:R13=R5[R10];

L31:R13=R13|R8;

L32:R13=R13>>1;

L33:R5[R11]=R13;

L34:R13=R3[R11];

L35:R14=R4[R11];

L36:R13=R13|R14;

L37:R14=R5[R11];

L38:R13=R13|R14;

L39:R13=-1-R13;

L40:R13=R13&R9;

L41:R7=R13;

L42:R10=R11;

L43:goto L45;

L44:R2=R2+1;

L45:goto L48;

L46:R10=R10-1;

L47:R7=R6[R10];

L48:if(R10!=0)goto L12;

L49:if(R12!=0)goto L51;

L50:R2=R2<<1;

L51:return(R2);

}

main(){

int n,cnt;

for(n = 1; n < 15; n = n + 1){

R1= n;

queens();

cnt = R2;

printf("queens(%d)=%d \n", n, cnt);

}

}

Автор: Ynicky Jun 2 2010, 06:50

А что означают выражения?:

R6[R10]=R7;

R13=R3[R10];

Николай.

Автор: Leka Jun 2 2010, 10:31

Косвенную адресацию памяти

R6[R10]=R7; --> STORE R7,(R6+R10)

R13=R3[R10]; --> LOAD R13,(R3+R10)

Для 2х-операндной архитектуры:

R6[R10]=R7; -->

MOV R0,R6

ADD R0,R10

ST R7,(R0)

R13=R3[R10]; -->

MOV R0,R3

ADD R0,R10

LD R13,(R0)

или переписать "ассемблерный" код под 2х-операндную архитектуру с использованием указателей R6 R3 вместо пар база-индекс:

*R6=R7;

R13=*R3;

и учесть такие мнемоники в трансляторе в машинные коды.

Вариант N-ферзей с указателями на "ассемблерном" Си (кроме main(){}).

int

count,

arow[20],

aleft[20],

aright[20],

aposs[20],

poss,

place,

val,

pos,

pos1,

N1,

temp,

temp1,

*prow,

*pleft,

*pright,

*pposs,

*prow1,

*pleft1,

*pright1,

*pposs1;

count = 0;

N1= N & 1;

temp = 1 << N;

val = temp - 1;

temp = N >> 1;

poss = val >> temp;

pos = 1;

//

prow=arow+1;

pleft=aleft+1;

pright=aright+1;

pposs=aposs+1;

//arow[1] = 0;

//aleft[1] = 0;

//aright[1] = 0;

//aposs[1] = poss;

*prow = 0;

*pleft = 0;

*pright = 0;

*pposs = poss;

do{

if( poss != 0 ){

temp = -poss;

place = poss & temp;

temp = ~place;

poss = poss & temp;

if( pos == N1 && poss == 0 )

count = count << 1;

if( pos != N ){

pos1 = pos + 1;

//

prow1 = prow+1;

pleft1 = pleft+1;

pright1 = pright+1;

pposs1 = pposs+1;

//aposs[pos] = poss;

*pposs = poss;

//temp = arow[pos];

temp = *prow;

temp = temp | place;

//arow[pos1] = temp;

*prow1 = temp;

//temp = aleft[pos];

temp = *pleft;

temp = temp | place;

temp = temp << 1;

//aleft[pos1] = temp;

*pleft1 = temp;

//temp = aright[pos];

temp = *pright;

temp = temp | place;

temp = temp >> 1;

//aright[pos1] = temp;

*pright1 = temp;

//temp = arow[pos1];

temp = *prow1;

//temp1 = aleft[pos1];

temp1 = *pleft1;

temp = temp | temp1;

//temp1 = aright[pos1];

temp1 = *pright1;

temp = temp | temp1;

temp = ~temp;

temp = temp & val;

poss = temp;

pos = pos1;

//

prow += 1;

pleft += 1;

pright += 1;

pposs += 1;

}else

count = count + 1;

}else{

pos = pos - 1;

//

prow -= 1;

pleft -= 1;

pright -= 1;

pposs -= 1;

//poss = aposs[pos];

poss = *pposs;

}

}while( pos != 0 );

if( N1 == 0 )

count = count << 1;

return count;

}

main(){

int N;

for(N = 1; N < 15; N = N + 1){

printf("queens(%d)=%d \n", N, queens(N));

}

}

Автор: Ynicky Jun 2 2010, 19:34

Закончил "в черне" процессор.

Вынес память программ и данных из ядра.

Дополнил системной шиной AMBA AHB и отладочными блоками для

работы через JTAG.

Теперь только тесты, тесты, правка и еще раз тесты.

Описание дополню в выходные.

Николай.

Автор: Leka Jun 2 2010, 20:50

Написал компилятор "ассемблерный" Си --> "машинный" Си, причешу - выложу (либо завтра, если успею, либо в понедельник).

Надо-бы побольше программ на "ассемблерном" Си для тестирования (как компилятора, так и процессора).

"Машинный" Си --> машинные коды на этой неделе уже не успею, но эта задачка заметно проще.

Автор: Ynicky Jun 5 2010, 16:47

Дополнил описание.

Автор: Leka Jun 7 2010, 19:40

Первая версия компилятора "ассемблерный" Си --> "машинный" Си.

Поддерживаются: int, if-else, do-while, блоки { }, см. примеры N-ферзей.

В текущей версии не поддерживаются вложенные круглые скобки и круглые скобки в выражениях.

Запуск из командной строки:

a2m < входной_файл > входной_файл

Например(см. a.bat):

a2m < q3.c > q3..c

Выходные (и входные) файлы можно проверить любым Си-компилятором, например, Tiny C Compiler в скриптовом режиме:

c:\tcc\tcc.exe -run q3..c

При установленном TinyCC:

a q3

Под "ассемблерным" подмножеством Си подразумевается отсутствие длинных арифметических и логических выражений, допускаются только 3х-операндные выражения(с учетом адреса перехода), которые м/б непосредственно преобразованы в машинные коды.

По поводу FP(указателя на кадр) - как в подпрограммах получать доступ к глобальным переменным в регистровом файле?

Автор: Leka Jun 7 2010, 21:25

У меня указатель на область локальных переменных аппаратно "разворачивал" нумерацию регистров, так что R(0), R(1), R(2), ... в подпрограмме любой вложенности указывали на глобальные переменные, а R(-1), R(-2), R(-3) - на локальные, или наоборот. Например, для 8 регистров:

R0 R7 R6 R5 R4 R3 R2 R1 - main(){ int R7, R6, R5; f1( R5 ); }

R0 R1 R2 R7 R6 R5 R4 R3 - f1( int R7 ){ int R6, R5; f2( R5 ); }

R0 R1 R2 R3 R4 R7 R6 R5 - f2( int R7 ){ int R6, R5; ... }

С программной точки зрения подобная перенумерация регистров очень удобна. Проверил и в железе, и в ассемблере. Единственный недостаток - лишняя ступень логики.

Автор: Ynicky Jun 8 2010, 06:39

Тут я не понял. Я всегда считал, что глобальные переменные находятся в памяти данных.

И доступ к ним осуществляется через load/store.

Если они будут находиться в регистровом файле, тогда без переключения регистров не обойтись.

И сколько их может потребоваться?

Николай.

P.S.

Предлагаю пока не заморачиваться по поводу FP.

А дальше будет видно.

Автор: Leka Jun 8 2010, 08:21

Для вспомогательной подпрограммы основные данные - внешние, "в противном случае зовется ... иначе" - задача. Локальных по своей сути данных немного, это промежуточные результаты выражений, счетчики циклов, и тп.

Нет никакого смысла делать большой регистровый файл для локальных данных: 16 уровней вложенности пп * 4 локальные переменные в среднем = 64 регистра.

Если основные данные не в регистровом файле, имеет смысл отказаться от load/store архитектуры, добавив косвенно-регистровую адресацию ( *a=*b+*c; if(*a==*d)...; и тп ). Была у меня такая в железе, см ветку "посоветуйте простой софт-процессор".

Согласен, сначала нужен компилятор "машинный" Си --> машинные коды.

Автор: Ynicky Jun 9 2010, 09:55

To Leka:

Попробовал написать простенький тест.

После компиляции a2m запустил LCC.

Пока 2 явных замечания:

1. return надо отделить от 1 и 0.

2. в разных подпрограммах повторяющиеся метки.

Проект во вложении.

Николай.

Автор: Leka Jun 9 2010, 12:52

Забыл написать, надо "return(1);" вместо "return 1;" Сделано специально - как вызов функции, а не ключевое слово.

Вроде это не противоречит стандарту (локальность меток в пределах функции), но если надо - могу добавлять имя функции к метке.

Автор: Leka Jun 9 2010, 13:59

В a2m пока только один тип "int", поэтому "void" не допускается.

Ошибки потом поправлю, сейчас прорабатываю компилятор в машинные коды.

Из-за зависимости длины инструкции от данных (вставка imm20 и тп), решил поменять концепцию.

Автор: Ynicky Jun 9 2010, 16:29

Исправил несколько ошибок.

Проверил АЛУ без SMUL (пока нет), load/store.

Николай.

Автор: Leka Jun 9 2010, 20:41

Принцип получения hex-файла машинных кодов:

компилятор a2m в "машинный"Си будет также автоматически генерировать файл "code.c" для Си-скрипта "machine.c", запускаемого после a2m. Си-скрипт м/б выполнен TinyCC с ключом "-run".

В приложении пробная версия "machine.c"(с выводом мнемоник вместо hex-кодов) и тестовый "code.c".

Для настройки на конкретную систему команд в "machine.c" надо поменять текстовый вывод мнемоник на вывод соответствующих hex-кодов. Переменная "p" обеспечивает несколько проходов(2) для "подгонки" относительных адресов инструкций, тк их число зависит от данных(добавлений "imm20"). "t"!=0 означает константу. Остальное, думаю, понятно будет из исходника.

"a2m" позже подправлю под вывод "code.c".

Автор: Leka Jun 16 2010, 10:45

Концепцию немного поменял, "a2.exe" выводит код для Си-препроцессора.

Не хватает времени, не сделал вывод hex-кодов для конкретного процессора - в "a2b.c" надо поменять текстовый вывод мнемоник на вывод соответствующих hex-кодов ("a2a.c" настроил для конкретного 2х-операндного процессора).

Автор: Leka Jun 16 2010, 15:48

Пример вывода hex-кодов для некоторых команд (mov, cmp, и тп) в "a2b.c", для остальных делается аналогично. М/б стоит переписать "a2a.c" и "a2b.c", чтобы проще было вводить/править hex-коды команд.

Автор: Ynicky Jun 17 2010, 09:23

Что означает hex-код? Файлы a2a.c и a2b.c идентичны.

Николай.

P.S.

С hex-кодом разобрался. Это AL2 в a2b.txt.

А в hex-код можно добавить комментарий в виде мнемоники команд?

Тогда будет проще править.

Автор: Leka Jun 17 2010, 10:03

В "a2b.c" я еще исправил ошибку, вернул необходимые пары "{" "}" (случайно выкинул, когда "причесывал") - иначе неправильно считает адреса команд.

Думаю, надо переписать "a2a.c" и "a2b.c", чтобы были комменты, и удобно было править. Но сейчас много дел навалилось, освобожусь - займусь.

Автор: Leka Jun 17 2010, 21:37

В "a2b.c" надо вместо "00" кодов операций поставить реальные.

Вывод комментов добавил.

Автор: Leka Jun 18 2010, 08:34

По поводу слотов задержки в командах условных переходов. В FPGA вся память - двухпортовая, можно использовать для упреждающей выборки альтернативной инструкции из памяти программ - выигрываем 1 такт.

Автор: Ynicky Jun 18 2010, 11:50

В принципе, можно вообще обойтись без слотов задержки, как, например, в ARM-е.

Тогда мы будем терять 3 слота задержки при невыполнении условия перехода (flush).

Можно, конечно, сделать альтернативную выборку команд и не терять ни одного слота,

переключаясь на альтернативную ветку конвейера.

Но это, по моему, будет привязывать данную архитектуру только к FPGA.

Как это может сочетаться с кеш, пока не знаю.

Николай.

Автор: Ynicky Jun 20 2010, 09:42

Вывод комментов добавил.

Есть вопросы по командам в "a2b.c".

1. "TST" - это операция "AND" без записи в регистр (т.е. только изменение флагов)?

2. "BZ","BNZ" - ветвление, если результат "=0" и "/=0"? Дело в том, что с командами "CMP"

все условия ветвления сравниваются с '0'. Значит ли это, что их можно приравнять

к командам "BEQ" и "BNE"?

3. Что из себя представляют команды: "COM", "LDI", "LDD", "LDDI", "STI", "STD", "STDI"?

4. "ASL" и "ASR" - это команды арифметического или логического сдвига?

Исправил еще несколько ошибок в процессоре.

Николай.

Автор: Leka Jun 20 2010, 14:41

любая операция без записи в регистр, устанавливающая нужные флаги для "BZ","BNZ".

Можно "CMP" с нулевой константой.

Да.

Напрямую не получится, тк "0" задан неявно.

Либо в "ассемблерном" Си всегда писать "if(a!=0)..." и "if(a==0)..." вместо "if(a)..." и "if(!a)...", либо ввести формальные команды "BZ" и"BNZ", подразумеавющие сравнение с нулем. В фактической системе команд они не нужны, и в машинных кодах

заменяются "BEQ" и "BNE" с нулевой константой.

COM: Ra=~Ra;

LDI: Ra=*Imm;

LDD: Ra=Rb[Rc];

LDDI: Ra=Rb[Imm];

STI: *Imm=Ra;

STD: Ra[Rb]=Rc;

STDI: Ra[Rb]=Imm;

"LDD" и "STD" - для 3х-операндной системы команд.

"LDDI" и "STDI" получаются "за компанию".

То-же, что и "<<" и ">>" в Си.

Можно добавлять свои команды например:

#define MAX( a, b ) AL2( max, maxi, a, b );

и определить соответствующие коды "max" и "maxi", из Си можно вызывать:

MAX( a, b );

Но тогда для отладки в Си надо определить в тестовых программах:

#define MAX( a, b ) if( a < b ) a = b

и тд и тп.

Для другой архитектуры "a2a.c" и "a2b.c" будут другими, а вот "a2с.c" менять не понадобится.

Автор: Ynicky Jun 20 2010, 16:28

Насколько я знаю, "<<" - это всегда логический сдвиг, а ">>" - либо логический либо арифметический,

в зависимости от переменной (беззнаковой или знаковой). Это так?

Николай.

Автор: Leka Jun 20 2010, 17:03

Для чисел в дополнительном коде арифметический и логический сдвиг влево - результат одинаковый.

в зависимости от переменной (беззнаковой или знаковой). Это так?

Да. У меня пока только один тип "int", и поэтому подразумевается только арифметический сдвиг.

В принципе, ввести дополнительные типы несложно, но проект, судя по всему, развиваться не будет(мало участников) - поэтому не вижу смысла (сам предпочитаю "бестиповую" архитектуру).

Автор: Ynicky Jun 20 2010, 17:11

Согласен.

Автор: Leka Jun 20 2010, 17:18

На всякий случай посмотрел стандарт на ANSI C, там результат сдвига вправо знаковых чисел - зависит от реализации.

Надеюсь, кое-какая польза все-таки была извлечена из этого проекта.

Автор: Ynicky Jun 20 2010, 17:46

Для меня - да.

Автор: Leka Jun 20 2010, 19:15

Посмотрел "a2h.c" и "aaa.txt".

Тк в системе команд rf32 нет "sti",

то либо предварительно загружать константы в определенный регистр(например R0),

либо все константы загружать в регистры в начале программы.

Например, по второму способу надо изменить "INT(a,b )" (объявление константы) в "a2h.c":

и "ST(a,b )":

в этом случае определять код sti не нужно.

Аналогично можно менять/добавлять другие команды.

"INT(a,b )" - объявление константы (int n=1; ), м/б код записи в регистр.

"ARR(a,b )" - объявление массива (int arow[20]; ) - д/б выделение памяти, пока игноируется. Д/б код типа "heap+=b; v[a]=heap;"

"CHR(a,b )" - объявление строковой константы (int s="hello,world!"; ) - д/б выделение и инициализация памяти, пока игноируется.

Автор: Leka Jun 20 2010, 22:04

Пример "a2h.c" с печатью секции ".REG" - начальные значения регистров, в тч адреса массивов. Там-же вариант разворачивания "sti" в 2 команды: "movi" и "st".

Автор: Leka Jun 20 2010, 23:14

Для примера переопределил "bz", "bnz", "neg", "com",

и исправил "ALxx" - чтобы проще было определять инструкции с константами.

Автор: Ynicky Jun 21 2010, 09:57

To Leka: А что делать с секцией ".REG"?

Надо прописывать в регистровый файл?

Николай.

P.S.

Понял, надо.

Автор: Ynicky Jun 23 2010, 18:38

Попробовал отмоделировать программу "queens".

Работает не правильно.

Тогда стал писать тесты. Сразу обнаружил следующее:

{

int iA = 1;

int iB = 2;

iB = iA;

}

=>

.REG

000:00000000

001:00000001

002:00000002

.CODE

000001:45002001 ;iB=iA; //формат RI вместо RR!!!

000002:12000000 ;}

Но если переменную iA не инициализировать, то все нормально:

{

int iA;

int iB = 2;

iB = iA;

}

=>

.REG

000:00000000

001:00000000

002:00000002

.CODE

000001:25002001;iB=iA; //!!!

000002:12000000;}

Николай.

Автор: Leka Jun 23 2010, 20:43

Поправил "a2" и "a2h.c" (помимо "#define REG" поменял также "#define STR" - это потом может пригодиться, для работы со строками, после определения "#define CHR").

Не ту версию прикрепил, поправил.

Автор: Ynicky Jun 27 2010, 10:38

{

int *ptr1;

int *ptr2;

int iA,iB;

*ptr1 = 0xA;

*ptr2 = 0xB;

iA = *ptr1;

iB = *ptr2;

}

=>

.REG

000:00000000

001:00000000

002:00000000

003:00000000

004:00000000

005:0000000A

006:0000000B

.CODE

000001:4500000A ;

000002:66001000 ;*ptr1=0xA;

000003:4500000B ;

000004:66002000 ;*ptr2=0xB;

000005:62003001 ;iA=*ptr1;

000006:62004002 ;iB=*ptr2;

000007:12000000 ;}

Помоему, в командах "STORE" (опкод 66) перепутаны местами RD и (RS).

У меня в системе команд RD и (RS) находятся в одном и том же месте для формата "LOAD/STORE".

Николай.

Автор: Leka Jun 28 2010, 18:05

В "a2h.c" "#define ST(a,b )..." надо исправить на "#define ST(b,a)...".

Автор: Ynicky Jun 29 2010, 09:10

Исправил, заработало, проверяю дальше.

Николай.

Автор: Ynicky Jul 3 2010, 18:52

Промоделировал "queens".

Результаты совпадают с "q.c".

Указатели в "q2.c" изменяются на 1, в то время как у меня в процессоре байтовая адресация,

т.е. указатели должны меняться на 4. Временно сдвинул адрес в процессоре на 2 разряда вправо

и все заработало.

2 Leka: Что нужно (или можно) посмотреть по результатам моделирования?

И еще, для чего в программе "q2.c" мы обращаемся к памяти через указатели?

Почему нельзя обойтись только регистрами?

Ошибок в процессоре больше пока не обнаружил.

Николай.

Автор: Leka Jul 5 2010, 19:20

Это общая проблема арифметики указателей.

По стандарту на Си, в "q2.c" все правильно, тк это компилятор должен делать поправку на тип данных (у меня не делает). Варианты выхода из этого положения:

1) добавить в компилятор полную поддержку типов, как в Си,

2) использовать в SoC раздельную память для байтов/слов,

3) ...

Сам использовал 2-ой вариант, тк SoC под конкретную задачу, и память разбивается на отдельные блоки нужного размера, и с нужной разрядностью(и не обязательно кратной 8).

А 1-ый вариант в одиночку делать не буду, тк предпочитаю бестиповые языки/архитектуры, и индексную адресацию.

Не понял.

В программе используются массивы, обращаться к элементам массива можно либо при помощи индексной адресации, либо через указатели. Как еще? Если процессор поддерживает косвенную адресацию регистрового файла, все-равно на Си это будет либо индексная адресация, либо указатели.

Автор: Leka Jul 6 2010, 22:53

Например, код на Си:

int *a, i; ... a+=i; *a=i; ...

и эквивалентный код на "ассемблерном" Си для 2х-операндной 32х-разрядной архитектуры:

int a, i, tmp; ... tmp=i; tmp<<=2; a+=tmp; *(int*)a=i; ...

--> имхо, громоздко, неэффективно, и непереносимо на другую разрядность/архитектуру.

Поэтому и нравятся бестиповые языки/архитектуры.

И с индексной адресацией.

Пример N-ферзей с явной арифметикой указателей:

queens(){

int

arow[20], aleft[20], aright[20], aposs[20],

poss, place, val, pos, pos1, n1, temp, temp1,

prow, pleft, pright, pposs,

prow1, pleft1, pright1, pposs1;

count = 0;

n1 = n;

n1 &= 1;

val = 1;

val <<= n;

val -= 1;

temp = n;

temp >>= 1;

poss = val;

poss >>= temp;

pos = 1;

prow = arow;

prow += 4;

pleft = aleft;

pleft += 4;

pright = aright;

pright += 4;

pposs = aposs;

pposs += 4;

prow1 = prow;

prow1 += 4;

pleft1 = pleft;

pleft1 += 4;

pright1 = pright;

pright1 += 4;

pposs1 = pposs;

pposs1 += 4;

*(int*)prow = 0;

*(int*)pleft = 0;

*(int*)pright = 0;

*(int*)pposs = poss;

do

if( poss ){

temp = poss;

temp = - temp; //0-temp;

place = poss;

place &= temp;

temp = place;

temp = ~temp; //^=-1;

poss &= temp;

if( pos == n1 )

if( ! poss )

count <<= 1;

if( pos != n ){

*(int*)pposs = poss;

temp = *(int*)prow;

temp |= place;

*(int*)prow1 = temp;

temp = *(int*)pleft;

temp |= place;

temp <<= 1;

*(int*)pleft1 = temp;

temp = *(int*)pright;

temp |= place;

temp >>= 1;

*(int*)pright1 = temp;

temp = *(int*)prow1;

temp1 = *(int*)pleft1;

temp |= temp1;

temp1 = *(int*)pright1;

temp |= temp1;

temp ^= -1;

temp &= val;

poss = temp;

pos += 1;

prow += 4;

pleft += 4;

pright += 4;

pposs += 4;

prow1 += 4;

pleft1 += 4;

pright1 += 4;

pposs1 += 4;

}else

count += 1;

}else{

pos -= 1;

prow -= 4;

pleft -= 4;

pright -= 4;

pposs -= 4;

prow1 -= 4;

pleft1 -= 4;

pright1 -= 4;

pposs1 -= 4;

poss = *(int*)pposs;

}

while( pos );

if( ! n1 )

count <<= 1;

}

main(){

do{

queens();

printf("queens(%d)=%d\n",n,count);

n = n + 1;

}while( n < 15 );

}

Чтобы такое можно было компилировать в hex-файл, надо слегка поправить компилятор:

1) убрать возможность объявления указателей "int*",

2) заменить в выражениях "*" на "*(int*)".

Стоит овчинка выделки?

Автор: Leka Oct 1 2010, 19:15

![]()

Между первым э/м реле: http://electronix.ru/redirect.php?http://ru.wikipedia.org/wiki/%D0%A0%D0%B5%D0%BB%D0%B5

и первой вычислительной машиной на них: http://electronix.ru/redirect.php?http://ru.wikipedia.org/wiki/Z3

>100 лет... Что мешало?

Автор: DevL Oct 25 2010, 20:20

очень интересный пример!

для уточнения - при симуляции надо использовать rf32sim_TB_runtest.do , правильно ?

и несколько для ленивых - есть ли описание signal names, что бы проследить исполнение src\prg.txt ?

Автор: Leka Jan 11 2011, 16:29

Жаль, что проект с компилятором заглох...

Делаю апгрейд своего софтпроцессора - вместо Фон-Неймановской архитектуры взял Гарвардскую, и выделил 1К регистровый файл в отдельную 3х-портовую память. После P&R для минимального 18-разрядного ядра без периферии:

Спартан3 ~120 ЛУТ, ~120МГц,

Циклон3 ~250 ЛУТ, ~120МГц.

a=b+c; - 1 такт,

a[i]=b[j]+c[k]; - 2 такта.

Автор: PVL Feb 22 2011, 23:37

Программеров разогнали, деньги кончились. Сейчас работаю только на основной работе.

По поводу производительности - сейчас рулят синтетические наборы инструкций с сетевой организацией вычислительных блоков. Одна российская контора пытается сделать это на ПЛИС. Цель - обогнать видеокарту по производительности. Блажен кто верует...

Автор: DevL Apr 20 2011, 21:02

кстати , для гибкости в выборе ассемблера - оказался очень забавный вариант описанные тут "Пакет для разработки ПО для ПК "Специалист""

http://electronix.ru/redirect.php?http://shoorick.ho.ua/spec/index.html

в частности использование winasm + fasm - где по большому , даже не важно что fasm не сильно работает с нужным 8080, а просто используется для трансляции например комадны

LXI в то что fasm может обработать

[b]db [/b]((r1 and 6) shl 3) + 1

[b]dw [/b]imm }

в итоге - получается удобство winasm как IDE + полная компиляция

Автор: Lexey May 7 2011, 22:03

Давно маюсь с софт-процессором для ПЛИС, решил поделиться своеми соображениями.

Ни один из готовых вариантов меня не радует, хотя в моих требованиях нет ничего оригинального и нереального:

1. FPGA не BGA (производство мелкосерийное, множество проектов с оригинальным железом)

2. SDRAM до 64MB (один 16-битный чип),

3. Полноценное ядро OC, файловая система, т.п. чтобы беспроблемно портировалось готовое.

5. Несложная но гибкая и разнообразная обработка потоков данных, cравнимых с пропускной способностью SDRAM

Ключевая проблема тут в том что имеющиеся процессоры очень непроизводительны при работе с SDRAM.

Я пытаюсь решить ее

1.Интеграция процессора с контроллером SDRAM:

1a. отказ от использования стандартной шины

1b. асинхронное выполнение команд загрузки/cохранения контроллером SDRAM

контроллер имеет 2 интерфейса c ядром: интерфейс приема команд и интерфейс возврата данных в регистры.

контроллер одновременно может обрабатывать около десятка команд, что позволяет оптимизировать работу шины.

2.Отказываюсь от кэша данных, как от вещи малоэффективной и ресурсоемкой в данной ситуации.

3.Интерфейс между ядром и потоковым железом реализуется через 2-x портовые блоки EBR, на что предполагается израсходовать

большинство доступных EBR.

При такой организации отпадает необходимость прямого доступа железо<->SDRAM, поскольку сам процессор сможет пересылять данные по прерываниям между EBR и SDRAM не менее производительно чем любой железный DMA (но при этом гораздо гибче и удобней),

a "DMA контроллер" железо<->EBR тривиален.

За основу взял архитектуру LM32, FPGA Lattice XP2, verilog,

Прочие подробности:

-Mинимальный MMU на 512 страниц в пространcтве 64MB (вся таблица страниц текущей задачи вмещается в один EBR)

-1KB 2-way Instruction cache+ 1KB local instruction memory (1 EBR)

-Регистры в распределенной памяти

-Минимальная конвейеризация (простейшие команды читают регистр, выполняются и сохраненяют результат в одном такте)

-Предполагаемая тактовая : 125 MHz (общая для ядра и SDRAM)

-Предполагаемый размер 2500 LUT+2EBR (без учета интерфейсных EBR)

-Возможность экономной реализации 2x-SIMD путем раздвоения ALU. (регистровый файл по-любому 2-x банковый)

-Потери перехода: прямой 1 такт , косвенный 2 такта.

Стадия разработки: около 50% исходников, через 3-4 месяца надеюсь дойдет до отладки

Автор: alexPec May 7 2011, 23:20

Отказываюсь от кэша данных, как от вещи малоэффективной и ресурсоемкой в данной ситуации.

Так кэш то и призвана решать эту проблему. Хотя смотря под какие задачи и какая кэш.

Предполагаемая тактовая : 125 MHz (общая для ядра и SDRAM)

На каких fpga? Если бюджетные, то мне например идея асинхронщины не нравится

a "DMA контроллер" железо<->EBR тривиален.

Опять же смотря под какие задачи. Если для обработки видео - без дма сразу нет. Да и вобще софт процессор без дма...

Автор: Lexey May 29 2011, 09:05

Интерфейс ядра - удобная штука для разделения проекта софтпроцессора на части.

При соблюдении несложных правил, определенных этим интерфейсом можно делать свои софт-процессоры используя готовую подсистему MMU, поддерживающую такой интерфейс, или наоборот.

- Подсистема MMU берет на себя все вопросы интерфейса процессора с внешним миром, включая по мере необходимости

такие вещи как организацию кэшей, трансляцию адресов и организацию внешних шин.

- Подсистема ядра определяет архитектуру процессора.

Предлагаю свою концепцию интерфейса:

input clk,rst,

//-- Instruction readout ----------------

input [31:0]C, //P3 Codeword

input [23:0]PC,//Program Counter

input CFault, //P3 Page Fault detected on current codeword

input CRdy, //P3 CodeWord Ready from IC

output CFRq, //P6 Next Codeword Fetch Request (keep it until CRdy become active)

input [1:0]PWords,// Prefetched words beyond the current codeword, sat@3

//-- Jumps ---------------

output JI,JR,JE, //Jump {Indirect,Relative,Exception} requests (Jx=JI|JR|JE)

input JB, //Jump Buffered, mutex{JI,JR,JE,JB}

output JxU, //Jump Unresolved for use with JI,JR,JE (most usable for JR)

input JBU, //Jump Buffered unresolved

output JAbort,JTake, //P7 Jump Abort/Take for unresolved buffered jump

output JFE, //Jump Fetch Enable (last slot word already fetched)

input Jmp, //P7+ Jump destination fetch

//Jx can be asserted only when all intended slot instructions

//already prefetched (see PWords)

//-- virtual adress from core ----------

output [23:0]JRA, //P6 JR address (from decoder)

output [23:0]JEA, //P4? JE address (Exception handler address)

output [25:0]LSA, //P3..P5 LS/JI address (from AU)

//-- Data Memory request interface -----------------

output MRq, //request

output MRqWr, //direction

output MRqSigned, //Load Mode

output [4:0]MRqGPR, //destination GPR

output [1:0]MRqSize,//data Size (bytes-1)

output [31:0]MRqWrD,//Write Data, M-aligned

output MRqExt, //Extended transfer (8 bytes), option for SIMD-like LS instructions

output [31:0]MRqWrExD,//Extended Data, 4-byte aligned, optional

input MRqAc, //Request Acception

input MRqFault, //last accepted request failed

input MRqWS, //Wait State for split-page translation

//MRqFail normally occurs next clock after MRqAc, only exception is rare case when

//unaligned request cross page boundary (MRqWS asserted for this case).

//MRqWS will be used as wait state for execution unit to prevent any next

//instruction from changing arch. state.

//-- Data Readout interface ------------------------

input MRdRq, //request

input [1:0]MRdSize,input [4:0]MRdGPR,input MRdSigned,//Destination descriptor

input [31:0]MRdD, //P4+m Read Data, M-aligned

input MRdEx, input [31:0]MRdExD, //optional

output MRdAc, //acception

)

P0..P7 - cтупени комбинаторной логики в 8-ступенчатой модели

Автор: svrdc Oct 31 2012, 07:00

Может кого интересуют IP дла плавающей точки. Могу предложить быстрый multifunc fp для вычисления DIV, RECP, SQRT, RSQRT

Автор: ArtemDement Dec 5 2012, 17:28

Ни у кого 10 000 000 $ не завалялось для спонсирования открытого процессора от http://electronix.ru/redirect.php?http://www.qimod.com ?

http://electronix.ru/redirect.php?http://habrahabr.ru/post/161489/

Автор: Victor® Dec 5 2012, 17:57

http://electronix.ru/redirect.php?http://habrahabr.ru/post/161489/

Лохотроном каким-то попахивает....

Вот это гораздо прозрачнее и понятнее.

http://electronix.ru/redirect.php?http://opencores.org/donation

Автор: SyncLair Dec 6 2012, 21:30

Я что-то не понимаю зачем городить процессор, вроде и так все процессоры что есть имеют свободную спецификацию. Вот городить ВИДЕОпроцессор ну для трёхмерной графики -- это толк может и будет

Автор: Wic Dec 7 2012, 05:34

Свободная спецификация != открытый код/бесплатная лицензия. Если бы тот же арм имел открытый код, его бы очень быстро клонировали для специфичных применений. То о чем писали на хабре, имхо, фантастика. Современный процессор за 10Му.е. не сделать. А вот софтверный процессор с открытым кодом для FPGA реальная задача. Но ее нужно решать с оглядкой на ОС, которые на нем буду крутиться *nix/win/etc.

Автор: Leka Dec 7 2012, 07:17

"- Хочу предложить последнее свое изобретение. Это автомат для бритья. Клиент опускает монеты, просовывает голову в отверстие, и две бритвы автоматически бреют.

- Но ведь у каждого индивидуальное строение лица...

- Так это только в первый раз!"

ОС и интерфейсы - это и есть "автоматические бритвы". И какой смысл в "индивидуальном строении" процессоров?

Автор: alman Dec 23 2012, 23:31

такие вещи как организацию кэшей, трансляцию адресов и организацию внешних шин.

Вы ещё не забросили разработку процессора? У меня есть пожелания к реализации MMU и пожелание расширить систему команд.

Автор: alexey123_45 Aug 1 2013, 05:58

А как Вы относитесь к построению и применению forth-процессоров? Мне кажется, что это перспективное направление

Автор: Corner Aug 17 2013, 20:04

А мне больше нравиться архитектура, когда в одном программном слове указатели на данные и их формат. Одна инструкция содержит до 11 скрытых операций: две загрузки, три модификации данных, три пост модификации адреса, сохранение и две арифметические операции. Мало кода, четкая параллельность...

Автор: Егоров Aug 17 2013, 21:03

Прошу прощения, если невпопад, давно отошел от этих дел. Но то, что Вы описали - система команд, не архитектура. Архитектура тут одна - микропрограммное выполнение инструкций. Можно при одной и той же архитектуре ЦП создать множество систем команд, было бы умение прошить микропрограммник. Да, код сокращает, но время обработки растет даже непропорционально и с обработкой прерываний сложности возникают. Прервать можно безболезненно программу, а длиннючую микропрограмму уже рисковано.

По-настоящему архитектуру ЦП затрагивают другие критерии. Например, в одной разработке нужно было за один такт, а не побитно подпрограммой, развернуть слово , младший разряд в старший и т.д, наоборот. Вот там в архитектуру был включен специальный аппаратный блок.

Ну и еще фундаментальные общие определения архитектуры - гарвардская, фон-неймановская, теговая. Это относится к взаимодействию ЦП и памяти.

Автор: Corner Aug 21 2013, 16:21

http://electronix.ru/redirect.php?http://multiclet.com/ - будущее российских систем на кристалле.

Сколько не читал так и не понял, что тут за архитектура и на каких частотах работает. Такое ощущение, что это несколько ALU с шедулером и КП.

Автор: Paviaa Feb 21 2014, 12:19

Изучаю verilog, делаю свой процессор.

Чувствую что застрял. Какие есть архитектуры процессоров и что по ним можно прочитать?

Автор: Postoroniy_V Feb 21 2014, 13:38

Чувствую что застрял. Какие есть архитектуры процессоров и что по ним можно прочитать?

Computer Architecture A Quantitative Approach

осторожно трафик -> http://electronix.ru/redirect.php?http://eecs.oregonstate.edu/research/vlsi/teaching/ECE570_WIN13/computer_arch_quantitative_approach.pdf

http://electronix.ru/forum/index.php?showtopic=88548

Автор: Ynicky Feb 24 2014, 16:29

Мне очень помогло это: lec9_2.pdf ( 822.35 килобайт )

: 341

lec9_2.pdf ( 822.35 килобайт )

: 341

http://electronix.ru/redirect.php?http://www.kurtm.net/archive/2003-Fall-cs152-public_html/lecnotes/

Автор: alman Apr 29 2014, 01:01

Позвольте и мне показать "микропроцессор". Это 32-х битное ядро, которое выглядит так:

Ядро использует собственную систему команд, нескромно названную "Эверест":

- 16 регистров общего назначения

- позиционно независимый код

- большой запас для расширения системы команд

Частичное описание системы команд: http://electronix.ru/redirect.php?http://everest.l4os.ru/core/

Несколько слов об ассемблере: http://electronix.ru/redirect.php?http://everest.l4os.ru/assembler/

Пример пошаговой отладки ядра: http://electronix.ru/redirect.php?http://everest.l4os.ru/test_of_strlen/

Выполнение команд занимает 2-3 клока, не считая тактов ожидания внешних устройств. Ядро проверено на плате "Марсоход2" и показало возможность работы на 100МГц. В перспективе возможна реалиазция конвейерного исполнения команд. В более далёкой перспективе - одновременное выполнение нескольких команд за такт. Причём, параллельное выполнение некоторых команд можно достичь с небольшими издержками за счёт коротких команд и 40-битной входной шины. Т.е. в перспективе ожидается параллельное выполнение нескольких команд, если они не взаимозависимы и целиком поместились на входную 40-битную шину. Впрочем, это отдалённые перспективы, потому что...

Процессор создаётся с надеждой на то, что в скором будущем он обзаведётся аппаратным планировщиком и расширенным MMU с поддержкой универсальных страниц виртуальной памяти. В результате процессор станет первым в мире микропроцессором с аппаратно реализованным микроядром http://electronix.ru/redirect.php?http://l4hq.org/. Если успеет...

Собственно, ради реализации аппаратного микроядра и был затеян этот проект. Процессор создаётся под уже существующую микроядерную операционную систему (точнее - http://electronix.ru/redirect.php?http://L4os.ru).

Автор: alman May 5 2014, 11:55

Разреште поделиться небольшим успехом - процессор научился программно писать в последовательный порт.

Подробности по клику:

http://electronix.ru/redirect.php?http://everest.l4os.ru/hello_world/

Автор: alman May 9 2014, 19:47

Такое живое обсуждение процессоров в этой теме ![]()