Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Системы на ПЛИС - System on a Programmable Chip (SoPC) _ NIOS для начинающих

Автор: AlexBel Oct 12 2009, 17:47

Имею девборду Altera DE1 (Cyclone II 2C20). Хотел бы своими руками "пошшупать" NIOS. Где-нибудь можно найти что-то типа "курса для начинающих", желательно с использованием DE1? Чтобы и теория была и практика и доступные пониманию новичков примеры. Конечная цель - создание "железа" с SDRAM и видеоконтроллером и разработка софта под него.

Автор: Full41 Oct 12 2009, 18:00

Материала на русском языке мало, я бы даже сказал почти нет! А вот на английском на официальном сайте altera есть, да же есть примеры процессоров. Я когда начинал пробовать работать с NIOS сделал простенький проект, который нашел на одном сайте, там расписано как делать и какие инструменты для чего! А после этого уже стал сам пробовать реализовать свои небольшие придумки на NIOS! Если хочешь могу скинуть ссылку на сайт!=))

Автор: AlexBel Oct 12 2009, 18:39

Спрашиваешь!

Автор: Full41 Oct 12 2009, 18:46

У тебя проблемы с ящиком не чего не отправляется!! если напишешь почту, то скину туда

Автор: AlexBel Oct 12 2009, 19:22

alex (собака) speccyland.net

Автор: Full41 Oct 12 2009, 19:28

Все отправил

Автор: AlexBel Oct 12 2009, 20:09

Все получил, спасибо, буду изучать!

Автор: iosifk Oct 13 2009, 04:50

demosondemand.com

Или ниписать в Гамму-выборг и поросить диск с этими презентациями...

А у меня на сайте есть пара статей... Но они еще про самый первый Ниос. И еще сохранилось кое-что, что я переводил по Ниосу на сайте Эфо. Ссылка у меня на сайте есть.

Удачи!

Автор: sysel Oct 13 2009, 05:47

Это сайт какой-то подпольной экстремистской организации?

Если нет - выложите, пожалуйста, ссылку тут.

Автор: Full41 Oct 13 2009, 06:01

Да нет нормальный сайт, там просто в кратце на русском приводят пример создания проекта на NIOS. Я с этого все начинал!!

http://electronix.ru/redirect.php?http://www.(текст)profelectronica.ru/index.php?option=com_content&view=article&id=64%3Aniosii&catid=42%3Adevaart&Itemid=71&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b

При использовании ссылки убрать фразу (текст)

http://electronix.ru/redirect.php?http://www.(текст)profelectronica.ru/index.php?option=com_content&view=article&id=64%3Aniosii&catid=42%3Adevaart&Itemid=71&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b

При использовании ссылки убрать фразу (текст)

это не правильная ссылка вот правильная

http://electronix.ru/redirect.php?http://www.profelectronica.ru/index.php?option=com_content&view=article&id=64%3Aniosii&catid=42%3Adevaart&Itemid=71&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b

[quote name='Full41' date='Oct 13 2009, 10:00' post='661400']

Да нет нормальный сайт, там просто в кратце на русском приводят пример создания проекта на NIOS. Я с этого все начинал!!

http://electronix.ru/redirect.php?http://www.profelectronica.ru/index.php?option=com_content&view=article&id=64%3Aniosii&catid=42%3Adevaart&Itemid=71&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b&8287022a4ffc9b43c8b1b7997c9cdac2=790a0c5e9deed6e28c62d24039cbdd9b

Автор: Stewart Little Oct 13 2009, 13:01

Полезный ресурс для начинающих - http://electronix.ru/redirect.php?http://www.nioswiki.com/

Содержит кучу примеров, в т.ч. SDRAM и пр.

Автор: AlexBel Oct 13 2009, 16:31

Содержит кучу примеров, в т.ч. SDRAM и пр.

Спасибо!

Автор: Kuzmi4 Oct 13 2009, 18:13

Может тему в шапку вынести , а то вопросы по ниосу довольно часто встречаются ??

Автор: Full41 Oct 14 2009, 05:20

точно, необходимо перенести тему NIOS в шапку!!

Автор: Omen_13 Oct 18 2009, 18:45

Сделано по просьбе трудящихся... ![]()

С уважением, модератор

Автор: Reanimator++ Oct 27 2009, 11:28

AlexBel

Леш, я запустил ниос пройдя "Nios II Hardware Development Tutorial" - http://electronix.ru/redirect.php?http://www.altera.com/literature/tt/tt_nios2_hardware_tutorial.pdf

Просто по порядку делай что там написано и все )

у меня кита нет, потому запускал на своей макетке под EP2C8. все получается, правда пришлось поиграться с оптимизирующими галочками, поскольку пример без модификаций расчитан на EP2C20, а у С8 меньше onchip RAM.

использовал программатор Игоря - http://electronix.ru/redirect.php?http://www.speccyland.net/forum/viewtopic.php?f=13&t=9

Nios II IDE нормально с ним работает, включая пошаговую отладку программы в железе.

Автор: Full41 Nov 17 2009, 13:28

Хотел узнать, можно ли использовать переферийные устройства из SOPC Builde (rs232, USB и тд), без использования самого процессора!?

Автор: Kuzmi4 Nov 17 2009, 13:50

2 Full41 - можно, только вам тогда нужно будет написать своего мастера, который ими дирижировать будет ![]()

Автор: Full41 Nov 17 2009, 13:58

То есть самому написать мастер шину!!?

Автор: Stewart Little Nov 17 2009, 14:06

Не "мастер шину", а "мастер на шину". Шина - она стандартная (Авалон), на ней бывают мастеры и слейвы.

Мастер - это тот, кто может инициировать транзакцию (т.е. передачу данных). Стандартные мастеры - это, к примеру, ядро NiosII, или блок DMA.

Слейв - тот, кто поддерживает транзакцию (т.е. принимает или передает даные в соответствии с поступившим ему запросом).

Ваши rs232, USB и тд. - это слейвы. К ним должен кто-то обращаться (во-первых - для того, чтобы сконфигурировать, или задать режим; во-вторых - записать или считать информацию). Этот "кто-то" и есть мастер.

Автор: Full41 Nov 17 2009, 14:13

Все понял!! Буду пробовать!! Спасибо!!

Автор: Евгений Николаев Dec 9 2009, 17:21

Уважаемые гуру, подскажите - как "объяснить" NIOS IDE 9.1, что после компиляции проекта мне нужно обновлять onchip_memory.hex? А то отчитывается об успешной компиляции, пишет- сколько байт ушло на код, генерит .elf, .objdump и на этом всё.

В SOPC-builder'е кроме onchip_memory никакой другой памяти нет, векторы Reset, Exception и Break настроены на onchip_memory.

При тех же самых действиях NIOS IDE 7.2 генерировал .hex без вопросов, а здесь сходу не получилось.

Ну и заодно - сходу не нашёл привычной вкладки настроек "program never exits", "small C library" и т.п.. Где искать?

Автор: inco Dec 9 2009, 19:59

Евгений Николаев

В 9.1 в этом плане сильно всё поменялось!

Теперь для генерации файлов инициализации памяти надо правой кнопкой клацнуть по названию проекта в project explorer в выпавшем окне Make targets->Build.. появится окно Make Targets в котором должен быть пункт mem_init_install. Стать на этот пункт и нажать в этом же окне кнопку Build. После этого ниос сгенерит новые файлы образов памяти. Если этого пункта нет, то нажать кнопку Add и в появившемся окне Create a new Make terget создать такой пункт. В поле Target Name ввести mem_init_install, в поле Make Target тоже mem_init_install остальное по умолчанию. После этого можно будет генерить образы.

Редактировать параметры компиляции надо в BSP Editor.

Чтобы его вызвать в project explorer правой кнопкой клацнуть по названию проекта системной библиотеки и в выпавшем окне Nios II->BSP Editor...

Автор: Евгений Николаев Dec 10 2009, 04:37

inco, спасибо!

Сегодня попробую. Честно говоря, считал, что перейду с 7.2 на 9.1 за один день, но 9-ый, в отличие от 7-го, не интуитивно понятен.

---

Работает! ![]()

Кстати, переход начал поэтапно - сначала поставил 9-ый квартус, но пользовался 7-ым NIOS IDE - на первый взгляд всё нормально, с портов читает, выводит, но почему-то перестали работать прерывания от внутреннего обработчика.

Сейчас с 9-ым всё заработало. Видимо, альтеровцы частично что-то сменили внутри (кривые руки разработчика - тоже не исключаются, конечно ![]() ).

).

Автор: AlexBel Dec 12 2009, 18:05

Reanimator++

Рома, спасибо, извини, что не отреагировал сразу, но причину знаешь ![]()

Обязательно это попробую, как закончу проект...

Автор: barabek Dec 20 2009, 02:30

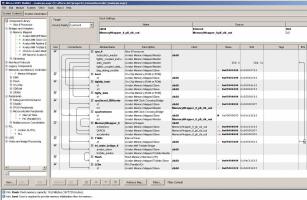

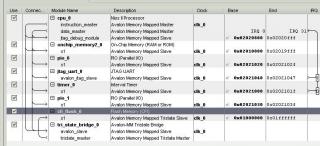

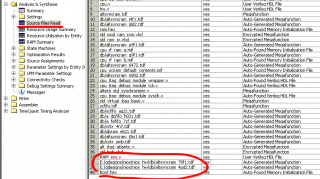

Подскажите. Есть система, картинка во вложении. MemoryWraper - это мой собственный контроллер DDR. Он включает в себя собственно контроллер доступа к DDR памяти, контроллер LCD (800*480) и что-то типа слабенького акселератора для видео (может отрисовывать точки, линии, заполненные прямоугольные области и символы с возможностью их масштабирования), ну и конечно арбитраж для совместного доступа. Соответственно, видеопамять и память, доступная для nios вся расположена в DDR, только в разных областях. Работает это все на 100МГц, а nios на 50.

Теперь собственно сама проблема. Собираю NIOS без кэша данных и с минимальным кэшем инструкций 512байт. В IDE для в свойствах системной библиотеки указываю для всего использовать только MemoryWraper. Программа (freertos с двумя примитивными task) не работает, причем по дебугеру сбоит в разных местах. Если выставить в настройках для .text и .rodata использовать MemoryWraper, а для всего остального onchip память tigtly_data - работает. Подскажите в каком направлении копать. То ли мой контроллер памяти тупит, но тогда, по идее он должен сбоить и на инструкциях (ведь при маленьком кэше инструкций выборки из памяти обязаны быть), либо что-то еще.

P.S. Если добавить кэш данных 1к и кэш инструкций довожу до 4к, при этом в кэш данных выставляю line size 32 байта, то работает при любом размещении. Если 4 байта line size - не работает, сбоит.

Автор: vadimuzzz Dec 20 2009, 03:23

похоже, сбоит запись в память(MemoryWraper), тогда понятно, почему не сбоит на инструкциях(там только чтение).

Автор: barabek Dec 20 2009, 03:38

Попробую это выяснить. Смущает то что при старте программа из флеша бутлоадером записывается в DDR. А есть ли какие-нибудь хитрые тесты памяти? Дело в том, что я писал прогу из 3 циклов, в первом цикле писала в DDR,во втором считывала, модифицировала и обратно записывала. В третьем проверялось содержимое. Затем опять на первый цикл. Работает без сбоев. Кэш обходил командами IOWR_32DIRECT и IORD_32DIRECT. Может нужны какие-то более жесткие тесты?

PS. Сейчас опять добавил подобный тест в одну из task. Каждую секунду выполняется один из выше описанных циклов. В конце 3-й секунды проверяется содержимое.

{

unsigned char i;

if(fl){for(i=0;i<64;i++)IOWR_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4, i);}

else {for(i=0;i<64;i++)IOWR_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4, 50000000-i);}

}

void SecondTune(void)

{

unsigned char i;

int tmp;

for(i=0;i<64;i++)

{

tmp=IORD_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4);

tmp*=10;

IOWR_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4, tmp);

}

}

unsigned char CheckMem(unsigned char fl)

{

unsigned char i,res=0;

int tmp;

for(i=0;i<64;i++)

{

tmp=IORD_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4);

if(tmp!=((fl?i:(50000000-i))*10))res=1;

}

return res;

}

В таске делаю это:

switch(state)

{

case 0: FirstFill(fl);break;

case 1: SecondTune();break;

case 2: if(CheckMem(fl))

{

LCDSetPrintPoint(120,70);LCDPutChar(ch+'B');

LCDSetPrintPoint(132,70);LCDPutChar(ch+'A');

LCDSetPrintPoint(144,70);LCDPutChar(ch+'D');

LCDSetPrintPoint(156,70);LCDPutChar(ch+'!');

LCDSetPrintPoint(168,70);LCDPutChar(ch+'!');

}else

{

LCDSetPrintPoint(120,120);LCDPutChar(ch+'O');

LCDSetPrintPoint(132,120);LCDPutChar(ch+'K');

LCDSetPrintPoint(144,120);LCDPutChar(ch+'!');

LCDSetPrintPoint(156,120);LCDPutChar(ch+'!');

LCDSetPrintPoint(168,120);LCDPutChar(ch+'!');

}

break;

}

state++;

if(state==3){state=0;fl=!fl;}

Сбоев нет! Хоть бы знать, куда копать. При этом у меня сейчас все сегменты установлены на MemoryWraper и есть дата кэш, описанный выше.

Автор: vadimuzzz Dec 20 2009, 06:42

можно погонять контроллер на тестах, что генерит мегавизард (файл _top.vhd или _top.v). еще такая дока есть www.altera.com/literature/an/an380.pdf. хуже, если где-то времянки перекосило.

Автор: barabek Dec 20 2009, 11:28

Насчёт времянок - это врядли. Так как считавание и запись от акселератора идет нормально. На экране изображение чистое. А внутри не может быть, ругался бы timequest. А за тесты спасибо за наводку. Завтра на работе посмотрю. А то я сам писал testbench, мог что-нибудь не учесть. Даже мой приведенный тест мне самому теперь не нравится- запись производится в последовательные ячейки.

Автор: barabek Dec 21 2009, 08:48

Переделал тест. Теперь он пишет сперва 5 ячеек подряд, затем 5 через 1, 5 через 2 и так далее до промежутка между ячейками равного 10 (получается две посылки подряд будут обращаться к одному банку в DDR но в разные блоки burst, она у меня 16 битная с burstlength=4, на один burst ложатся два int). Промежуточные ячейки, как фон, предварительно тоже заполняю. Проверял и с возрастающими адресами и с понижающимися, как в коде:

{

unsigned int i,j;

unsigned int addr=0;

for(i=0;i<300;i++)IOWR_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4, (fl?0xa5a55a5a:0x5a5aa5a5));

// for(j=1;j<11;j++)

// {

// for(i=1;i<=5;i++)

for(j=10;j>0;j--)

{

for(i=5;i>0;i--)

{

addr=((j-1)*j)/2*5+j*i;

IOWR_32DIRECT(CPU2EXTMEM_BASE+0x10000,addr*4, (fl?addr:(50000000-addr)));

}

}

//*********

void SecondTune(void)

{

unsigned int i,tmp;

for(i=0;i<300;i++)

{

tmp=IORD_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4);

tmp^=0xffffffff;

IOWR_32DIRECT(CPU2EXTMEM_BASE+0x10000, i*4, tmp);

}

}

//***********

unsigned char CheckMem(unsigned char fl)

{

unsigned int i=1,j=1,res=0,tmp;

unsigned int k;

for(k=0;k<300;k++)

{

tmp=IORD_32DIRECT(CPU2EXTMEM_BASE+0x10000, k*4);

if((((j-1)*j)/2*5+j*i)==k && j<11)

{

if(tmp!=((fl?k:(50000000-k))^0xffffffff))

res=1;

if(i==5){i=1;j++;}

else i++;

}

else

{

if(tmp!=((fl?0xa5a55a5a:0x5a5aa5a5)^0xffffffff))res=1;

}

}

return res;

}

В task блок проверки тот же. Работает, собака, как часы. Что еще можно придумать? Не может же Nios сам как-то подругому обращаться? Просто с родной (как советовал vadimuzzz) алтеровскй тестер небольшой головняк прикрутить для проверки. СтОит ли?

Может это ClockCrossBridge как-то у меня не правильно настроен, в описании мутная формула дана для минимальной длины slave-to-master, у меня он 64, а master-to-slave = 8.

Можно, конечно, забить. Такой вариант системы, как сейчас работает. Но как начну дальше писать уже нормальную прогу с несколькими task да как опять вылезет. Страшно.

Автор: Kuzmi4 Dec 21 2009, 08:57

2 barabek

когда у меня возникают проблемы похожего характера - цепляюсь сигналтабом на вх/вых порты компонента и смотрю что там творится. У меня как то тоже было что мои представления фунциклирования ниосовской проги расходились с тем, что я увидел на сигналтабе ![]()

Как вариант, если прога не большая и влезет в он-чип -может стоит поднять гейт-левел симуляцию (вдруг квартус чегой то за вас додумал) ?

Автор: barabek Dec 21 2009, 09:28

Kuzmi4

По поводу сигналтаба идея хорошая, но боюсь что будет: " - Петька, приборы? -40 -Что 40?.....". Всмысле как я буду отлавливать неудачные записи, не представляю. Нужно подумать.

По второму. По поводу гейт-левел понял. Но не понял причем здесь влезет или не влезет во внутреннюю память. Не могли бы разъяснить для тех кто в прочном корпусе ![]() . Кстати по поводу такой симуляции. Я под конец написания своего контроллера пробовал такую симуляцию. Она почему-то не пошла. Т.е. вообще все молчало. Забил. Если все-таки к ней вернуться, где почитать, как проводить симуляцию вместе с ниосом. Что-бы уже наверняка. При этом мне как раз и нужно, чтобы симулировалось с внешней памятью. С внутренней и так работает.

. Кстати по поводу такой симуляции. Я под конец написания своего контроллера пробовал такую симуляцию. Она почему-то не пошла. Т.е. вообще все молчало. Забил. Если все-таки к ней вернуться, где почитать, как проводить симуляцию вместе с ниосом. Что-бы уже наверняка. При этом мне как раз и нужно, чтобы симулировалось с внешней памятью. С внутренней и так работает.

А кто-нибудь пробовал подобную систему, но что-бы все сегменты распологались строго в DDR? Может это все-таки сомо ядро ниоса тупит при большой и изменяющейся латентностью чтения/записи данных. (всегда есть надежда что не сам виноват ![]() ).

).

Автор: vadimuzzz Dec 21 2009, 09:36

я гонял на стартер-ките. все в DDR(контроллер альтеровский), загрузка из FLASH. глюков не было, даже линукс грузил.

Автор: Kuzmi4 Dec 21 2009, 10:12

Разъясняю - пишем прогу для ниоса2, компилим, располагаем её в on-chip памяти, далее собираем всё системку на Modelsim-е, инициализируя вашу on-chip тем что выдал IDE (там только по-моему нужно будет ELF в HEX перегнать вроде), цепляем модельки ДДР2(ищем на сайте производителя - точно должны дыть) и LCD (если есть, тут думаю всё сложней чем поиск на сайте производителя будет), выводим интересующие вайры, делаем нужные стробы и смотрим что к чему..

Но это как то долго и интересно, когда железо в разработке или заказчику нужна функциональная модель того, что есть в железе.

Да и судя по-всему для вас это всё будет проблемно по началу и займёт много времемни. Думаю что всё же проще вам прицепить сигнал-таб и просто, для начала, посмотреть транзакции - как они у вас вообсче проходят в зависимости от ваших экспериментов с программой и ниосом2, ну а потом уже и стробы понапридумывать для тригирования событий.

Ну вот как то так..

Автор: vadimuzzz Dec 21 2009, 10:40

кстати, как-то упустили из виду. а какого рода сбой? повисает прога? и акселератор имеет прямой доступ к памяти?

Автор: barabek Dec 22 2009, 03:58

Убрал data cache.

Проверил - сбои непредсказуемые. Поясняю. В моей main перед уходом в sheduler имеются несколько строк кода. В зависимости от того, куда я ставлю breakpoint, а затем после остановки пускаю дальше прога вылетает в разные места. Иногда летит в обработку exception. причем подлавливал в регистре exception 0x14,0x0c и 0x1c (Illegal Instruction, Trap Instruction и Misaligned Destination Address). В другом месте поставлю брейкпоинт или делаю пошагово может дойти до цикла for(;;); и висеть, при этом ipending и ienable висят в 0х01 (то есть должно идти в прерывание, но не идет). Была ситуация, что крутится в цикле проверки пришедшего прерывания (ipending при этом равен 0x01, а переменная active - запомненное значение ipending в файле alt_irq_handler.c). Получается, что все-таки глюк с памятью скорее всего

Одно радует - если повторяю одни и теже действия с breakpoint вроде есть повторяемость. Значит можно будет сигналтаб (как советует Kuzmi4) на это как-нибудь настроить. Сейчас буду читать про связку сигналтаб+ниос, где-то видел апликуху или раздел.

2 vadimuzzz .Акселератор имеет прямой доступ. У меня контроллер MemoryWraper включает себя акселератор, контроллер вывода на LCD и контроллер доступа nios к памяти. Соответственно внутри реализован арбитр, который разруливает между ними. При этом половину полосы пропускания отводится для вывода на экран (подготовку fifo строки), оставшаяся половина делится между акселератором, чтением и записью в память поровну. Просто для чтения и записи один интерфейс с nios, для акселератора отдельный.

PS. Если вообще не ставить breakpoint, то залетаю до for(;;); и весит, при этом ipending и ienable равны 0х01, status=0, exception=0. Делаю перестановки строк, опять запускаю без брейкпоинтов - зависает на бесконечном цикле определения прерывания (active=0;)Очень странно. А можно ли будет одновременно работать и в дебугере niosa и в signaltab?

Автор: vadimuzzz Dec 22 2009, 07:00

можно и даже лучше так и делать www.altera.com/literature/an/an446.pdf плагин для ниоса в сигналтапе и дизассемблер умеет. еще можно попробовать так: .text и .rom запихать в он-чип, все остальное - в DDR. если сбои будут, значит конфликт с размещением(кто-то, скорее всего акселератор, пишет не по адресу, например, гадит в .text). что-то похожее было у меня, когда мой самописный avalon-master затирал память программ. сигналтапом я его и ущучил.

Автор: barabek Dec 23 2009, 13:42

vadimuzzz и Kuzmi4, спасибо! Действительно полезный оказался плагин. Нашел по крайней мере один косяк. В проге после компиляции обнаружил, что встречаются подряд 2 инструкции stw и ldw на тот же адрес (причем неоднократно - вроде неразумно поступает компилятор, но что есть то есть). А у меня запись и чтение идут по отдельным маршрутам. Соответственно чтение иногда обгоняет запись. Отсюда имею свое горе ![]() . Буду теперь ломать голову над этой проблемой.

. Буду теперь ломать голову над этой проблемой.

Автор: barabek Jan 24 2010, 07:28

Не знаю точно, сюда нужно постить, или в раздел gcc микроконтроллеров. Поиском похожие темы не нашел.

Есть такие структуры, описывающие подпись для кнопок меню (пока только текст, без иконок)

typedef struct {unsigned char lines;const lable_line_st* strinrs;}lable_text_st;

typedef struct {lable_text_st text;}lable_st;

Т.е. при выводе на экран сразу могу определить сколько строк в подписи и сколько в каждой строке символов для выравнивания по центру.

Необходимо каким-то образом красиво создавать подписи на этапе компиляции. Ничего не смог придумать лучше, чем:

#define STRINGLINE(x) {(sizeof(x)-1),x}

// в тексте

const lable_line_st Button1_text[]={STRINGLINE("line 0,"),STRINGLINE("line 2"),STRINGLINE("and line 3")};

const lable_st Button1={{3,

&Button1_text[0]

}};

хотелось бы, чтобы подпись можно было бы создавать как нибудь наглядней , что-то типа

Реально ли это как-нибудь сделать? Пробовал делать структуру с переменной длиной массива

typedef struct {unsigned char lines;const lable_line_st strinrs[];}lable_text_st;

Но компилятор ругается, т.к. эта структура является вложенной в другую структуру.

PS. Работаю в nios IDE, соответственно компилятор gcc, в свойствах библиотеки не стоит флажок "support C++" ,

Автор: vadimuzzz Jan 25 2010, 01:39

посмотрите тут http://electronix.ru/redirect.php?http://porn.quiteajolt.com/2007/11/05/initializing-a-struct-with-a-string-array-member-in-c/

название сайта жжот )

Автор: Serg_Sm Feb 10 2010, 10:07

Здравствуйте. Начинаю разбираться с ниосом, при этом возникло множество вопросов, кита к сожалению нет. Документации очень много, где конкретно искать непонятно плюс ко всему все рассмотренные мной описания сделаны под предыдущие версии, а в 9.1 много чего по другому.

Ответьте пожалуйста на следующие вопросы:

Я сделал проект на циклоне3 в квартусе состоящий из одного NIOS и PIO порта вывода (+JTAG UART). В NIOS IDE создал проект "Hello World small" на основе квартусовского.

1) В main вбил строчку

IOWR(0x00000000, 0, 0xffffffff); - запись в порт "1" с учетом того, что в SOPC Builder pio занимает адресное пространство с 0х00000000 верно или нет?

Скомпилилось успешно, elf создался.

2) Как зашить данный проект и откуда (квартус или NIOS IDE)? Компилирую в квартусе - в симуляторе выход не меняется.

В NIOS IDE запуск через "NIOS hardware" ничего не дает. Подцеплял плату подключенную через USB-Blaster, но не к JTAG (в плате используется AS загрузка), сброс видно что работает, но в списках соединений ничего не появляется. Будет ли работать при подключении к JTAG или надо еще что-нибудь сделать?

3) В каком именно документе находится описание использования периферии NIOS?

4) JTAG при конфигурировании NIOSа добавлять нужно для программирования? Или он по дефолту есть? "JTAG UART" это замена штатному или основной?

Автор: barabek Feb 11 2010, 05:43

Основное по NIOS - на "родине" http://electronix.ru/redirect.php?http://www.altera.com/literature/lit-nio2.jsp (Processor Reference Handbook, Software Developer's Handbook, ну и остальные по мере надобности), по самому Quartus - естественно первым делом его handbook ( http://electronix.ru/redirect.php?http://www.altera.com/literature/hb/qts/quartusii_handbook.pdf).

Книги эти большие, но там много воды, нужно научиться их читать, пропуская введения и т.п. перед каждым разделом.

1) Да.

2) Не понял как у Вас разведена на плате схема программирования. Возможны варианты с разведенными отдельно разъемами и JTAG и AS как на Figure 10–28. в книге "Cyclone III Device Handbook, Volume 1", на самом деле достаточно развести как "Figure 10–29. Programming Serial Configuration Devices In-System Using the JTAG Interface". У Вас вообще jtag выведен?

3) http://electronix.ru/redirect.php?http://www.altera.com/literature/hb/nios2/n2cpu_nii5v3.pdf

4) Нет, добавлять ничего не обязательно. JTAG UART это отдельная фича (сам не пользовался

Автор: Serg_Sm Feb 11 2010, 06:53

Большое спасибо за ответ.

Сейчас платы с разведенным JTAG у меня нет, поэтому хочу попробовать загрузить через AS. Требуется ли для этого какие-либо манипуляции в NIOS IDE?

После компиляции в симуляторе квартуса видно, что pio выводы остаются в нуле. Хотя в проекте NIOS им присваивается значение "1".

Автор: S_Lee Feb 22 2010, 20:45

Доброго времени суток. Я начал работать в SOPC Builder (Q8.1) и столкнулся с проблемой: мне необходимо создать свой условно говоря интерфейсик, для этого я хочу создать в SOPC свой компонент который будет состоять только из сигналов входов и выходов, но, создав такой компонент он не размещается в системе, а точнее он не попадает в адресное пространство. Кто-то может подсказать что-то? Как правильно создать компонент в сопк баилдер состоящий из портов входов и выходов?

Автор: barabek Feb 23 2010, 02:36

А чем стандартные Peripherals->PIO не устраивают? А по теме -мало информации, отсюда только вопросы: интерфейс делали согласно спецификации авалон шины? В SOPC билдере, когда создавали новый компонент все сигналы и интерфейсы правильно определялись/назначались? Наконец, литературу "Avalon Interface Specifications" и раздел в quartus handbook "component editor" читали?

Автор: Kuzmi4 Feb 23 2010, 08:43

для начала простенькие вопросы:

1) адресные линии вы ему забили в интерфейсе ?

2)на последней стадии создания ошибок в окошке не наблюдалось ?

3) он у вас в сопц билдере отражается ?

Автор: styuf Mar 9 2010, 10:22

Здравствуйте.

Я сделал проектик, с использованием niosa, который как то преобразует входные данные в выходные. Сам проект работает нормально, если программу хранить во внутренней памяти процессора. Но при попытки использования внешней флэшки застопорился. Делаю все, как написано http://electronix.ru/redirect.php?http://www.profelectronica.ru/index.php?option=com_content&view=article&id=64%3Aniosii&catid=42%3Adevaart&Itemid=71&8287022a4ffc9b43c8b1b7997c9cdac2=8a1e49e43ab21e3e9029372cab250efb&limitstart=3 , и появляется ошибка: No CFI table found at address 0x01000000.

Может что посоветуете?

Автор: vadimuzzz Mar 9 2010, 10:44

и появляется ошибка: No CFI table found at address 0x01000000.

Может что посоветуете?

у меня слабо развит дар телепатии, поэтому вопросы:

-что за плата(кит или своя)

-что за проект в квартусе(самодельный или из примеров)

-что нужно сделать с флешкой (только исполнять программу или еще и ПЛИС конфигурировать)

-картинку из SOPC-билдера

-читали ли эти темы: http://electronix.ru/forum/index.php?showtopic=64687 http://electronix.ru/forum/index.php?showtopic=70900

указанная ошибка появляется когда проц не видит флешку по указанному адресу, причин м.б. несколько - корявая распиновка, не тот адрес

Автор: styuf Mar 12 2010, 09:23

Жалко, что плохо развит ![]()

По порядку:

- плата стандартная альтеровская - Nios II Development board для EP2C35F672C6N такого циклона второго;

- проект самодельный;

- только программку хранить;

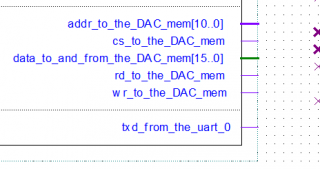

- картинка из SOPC (прикрепленна);

- читал, но видимо до проблем, разобранных там еще не добрался, по причине, обнаруженной пол часа назад: оказалась, что в SOPCе указывал не ту память. Отодрал наклейку с корпуса памяти и обнаружил S29GL128M10TFIR1. И думаю все бы ничего, щас все исправлю, но в инете не нашел ни одного описания именно этой памяти, даже на сайте изготовителя, а без описания не знаю как задавать в сопсе описание оной памяти.

Никто не работал с такой?

Автор: vadimuzzz Mar 13 2010, 10:57

это spansion. сама микросхема, видимо, снята с производства. ее более новая версия: http://electronix.ru/redirect.php?http://www.spansion.com/Products/Pages/ProductDetails.aspx?ProdID=S29GL128P. вот даташит на старую: http://electronix.ru/redirect.php?http://rapidshare.com/files/362755049/013-5320-S29GL032M10.pdf.html. из схематика http://electronix.ru/redirect.php?http://www.altera.com/literature/manual/CycloneII_NiosII_2C35_Rev02_DB_SCH.zip (зачем наклейку отдирали ? ![]() ) видно, что подкючена в 8-битном режиме, это надо учесть в SOPC-билдере. по идее, там все как у интела, ну в крайнем случае override сделать. читайте тут: www.altera.com/literature/ug/ug_nios2_flash_programmer.pdf. вектор сброса ниоса нацелить на флеш.

) видно, что подкючена в 8-битном режиме, это надо учесть в SOPC-билдере. по идее, там все как у интела, ну в крайнем случае override сделать. читайте тут: www.altera.com/literature/ug/ug_nios2_flash_programmer.pdf. вектор сброса ниоса нацелить на флеш.

Автор: S_Lee Mar 14 2010, 14:37

Кто-то может подсказать как можно создать блок, дающий на вывод тактирование в 1кГц, у меня циклон первый, там 50МГц тактовая, счетчик такую не дает частоту, можно конечно в ниосе написать мелкую программку, которая будет тактировать в 1кГц, но возможно есть проще способ???

Автор: barabek Mar 15 2010, 01:03

У счетчика есть опция timeout_pulse.

clock cycle whenever the timer reaches zero.

Автор: S_Lee Mar 20 2010, 09:40

как счетчик может дать 1КГц из 50МГц??? 16ти разрядный допустим -> (50 000 000 / (2^16=65536))=762 Гц

Автор: des00 Mar 20 2010, 09:56

а поделить на число отличное от 2^16 ?

Автор: barabek Mar 21 2010, 22:07

Не берем 65536, берем 50000 и получаем ровно 1кГц.

Автор: styuf Mar 22 2010, 07:20

Вечер добрый)

Вопросы собственно такие:

-Научился работать с флэшкой (ну или почти научился), делаю так, что бы с неё по нажатию кнопки фактори (factory) грузился и проект в альтеру с ниосом, и программка к ниосу. Но возникает такая трудность - программа работает 5 минут и стопарится. то бишь просто перестает реагировать на что либо (в нормальных условиях она по нажатию кнопки на плате раз в секунду выдает данные из ниоса). У кого-нить была такая проблема или хотя бы идеи есть, а то третий день ничего придумать не могу.

- Чем отличаются режимы NIOS II EPCS, NIOS II USER, NIOS II FACTORY в флэш программере кроме адреса оффсета?

Данные о проекте чуть выше по топику.

Автор: vadimuzzz Mar 22 2010, 07:52

во флеш-программере, пожалуй, ничем. последние 2 имеют отношение к фиче циклона-3 - Remote Upgrade. пример для active parallel: www.altera.com/literature/an/AN521.pdf

по первому вопросу: ниос тоже висит или только программа? на flash-programmer откликается?

Автор: styuf Mar 22 2010, 08:10

Эти параметры по умолчанию выставляют разное смещение адреса. Я так понимаю, именно начиная с величины смещения и начинается писаться прошивка для альтеры (То бишь не с нулевого). Судя по всему у циклона есть контроллер, которые работает с флэшками и при включении питания тянет прошивку из определенного места. А как конфигурировать контроллер мне на глаза не попадалось(

Хм, я даже и не знаю. Посмотрю, тогда скажу. У меня подозрения на переполнение чего-нибудь (памяти). Так как программа работает ровно какое-то время в активном режиме (при нажатой кнопке). В пассивном режиме, когда ничего в логике альтеры не происходит, оно может стоять хоть сколько.

Автор: vadimuzzz Mar 22 2010, 08:26

не только

http://electronix.ru/redirect.php?http://www.altera.com/literature/hb/cyc3/cyclone3_handbook.pdf секция 9

Автор: spectr Apr 13 2010, 18:17

Только начал осваивать Nios, поэтому сразу начали возникать вопросы. По мере их возникновения стараюсь по максимуму курить маны, но не всегда получается докопаться до истины. Вот и споткнулся на очередной, наверняка, простейшей фигне, но нигде не смог найти описание или какое-то указание о ней.

Итак, имею девбоард Altera DE2-70, QII 8.1 и Nios IDE такой же версии.

Собираю простейшую систему:

Самый мощный вариант процессора, он-чип память, PIO-вход (подключенный к свичам на плате), PIO-выход (подключенный к светодиодам на плате).

Компилю систему, заливаю ее программером (.sof-файл) - он прекрасно подцепляется (появляется сообщение о том, что система имеет такие-то временные ограничения и чере столько-то будет отключена - типа, все окей.

Далее в IDE создаю Nios II C/C++ проект (с библиотекой), содержащий в исходнике простейший сишный код (слизан из альтеровского же pdf-ника), адреса, естественно, выставляю те, которые получились у меня:

#define LEDs (char *) 0x0001810

void main()

{

while (1)

*LEDs = *Switches;

}

После этого компилю проект, а далее начинается вопрос (конфигурация хардвары создана).

Если я запускаю программу в режиме отладки (Debug as -> ....., бряк стоит на цикле), то при пошаговом выполнении (постоянно жму F5) я вижу что программа прекрасно работает, то есть светодиоды зажигаются/гаснут в зависимости от положения свичей.

Однако, если я запускаю проект не в режиме отладки, а просто как (Run as -> ......, бряк при этом снимаю), то программа, такое ощущение, не стартует... Так и не смог найти информацию - почему такое происходит....

То есть, что получается при запуске программы - я в консоли IDE вижу что он программу туда заливает (пишет ОК), верифицирует (пишет ОК), а потом пишет "Leaving target processor paused ". Я так понимаю что после загрузки программы процессор не запущен.

В хелпе все вроде бы четко написано (цитата из хелпа по Nios IDE):

1.

Creates a default run/debug configuration for the target board.

Note: This step usually completes automatically without user intervention. If it cannot (the most common cause is that you have multiple JTAG download cables installed), the IDE displays an error message, and you must manually set up a run configuration.

2.

Builds the project. If the project is not up-to-date, then the IDE builds it first to generate an up-to-date executable file.

3.

Establishes communication with the target board, and verifies that the expected SOPC Builder system is configured in the FPGA. If the FPGA is not configured properly, you should repeat the steps to configure the hardware.

4.

Downloads the executable file (.elf) to memory on the target board.

5.

Instructs the Nios II processor to begin executing the code.

Собственно, как выполнить пункт 5 (я так понимаю, именно в этом и затык) нигде не нашел упоминания.......

Автор: barabek Apr 13 2010, 23:29

попробуйте в строке "Additional nios2-download arguments" в диалоговом окне Run, вкладка Main написать --go

Автор: vadimuzzz Apr 14 2010, 00:37

это нормальное сообщение, а вот ваша программа вполне может и не работать так, как вы того ожидаете, особенно на NIOS-fast. точно сказать можно только для конкретной системы, но чаще всего это "фокусы" кэша данных. конструкции вида

//#define Switches (volatile char *) 0x0001800

//#define LEDs (char *) 0x0001810

#include "system.h"

#include "altera_avalon_pio_regs.h"

void main()

{

while (1)

//*LEDs = *Switches;

IOWR_ALTERA_AVALON_PIO_DATA(LEDs_base , IOWR_ALTERA_AVALON_PIO_DATA(Switches_base));//вместо LEDs_base и Switches_base подставить то, что в system.h

}

это будет работать независимо от наличия кэша

Автор: spectr Apr 15 2010, 06:33

Не помогло. Пишет следующее:

Processor is already paused

Initializing CPU cache (if present)

OK

Downloading 00002000 ( 0%)

Downloaded 8KB in 0.1s

Verifying 00002000 ( 0%)

Verified OK

Starting processor at address 0x00002020

и дальше тишина - никакой реакции на положения свичей.

...

это будет работать независимо от наличия кэша

На этот код компилятор вообще выдает ошибки:

#include "altera_avalon_pio_regs.h"

void main()

{

while (1)

IOWR_ALTERA_AVALON_PIO_DATA(0x00011010 , IOWR_ALTERA_AVALON_PIO_DATA(0x00011000));

}

Выхлоп компилятора:

- error: `IOWR_ALTERA_AVALON_PIO_DATA' undeclared (first use in this function) test_project main.c line 6;

- macro "IOWR_ALTERA_AVALON_PIO_DATA" requires 2 arguments, but only 1 given test_project main.c line 6;

Кроме того, еще ряд непонятных моментов образовался.

Вчера все работало (пускай и только в режиме отладки, но все же работало).

Сегодня - не работает вообще ни в одном из режимов (ни выполнение, ни отладка).

Почему? Ведь я не трогал абсолютно ничего...

П.С.: Может проще будет выложить сюда проект?

П.П.С.: В настройках компилятора отключено использование уменьшенных С-библиотек и всяческих оптимизаций, включена поддержка С++.

И еще вопрос: в настройках PIO в SOPC-билдере указываю разрядность 18 бит (именно столько свичей и светодиодов на плате). Однако, при отладке функционируют только 8 свичей и светодиодов. Что не так? Все адреса в SOPC-системе выровнены автоматически, если что.

Автор: barabek Apr 15 2010, 06:49

По второй ошибке. Вообще-то тут у уважаемого vadimuzzz опечатка. Нужно в скобках не WR а RD:

Еще, лучше явно не писать адреса, а брать имена, данные sopc bilder из system.h, типа

Однако, почему у Вас появилась ошибка, что якобы IOWR_... не определена, я затрудняюсь ответить.

Автор: Аматер Apr 15 2010, 07:07

Еще, лучше явно не писать адреса, а брать имена, данные sopc bilder из system.h, типа

Однако, почему у Вас появилась ошибка, что якобы IOWR_... не определена, я затрудняюсь ответить.

У меня используются заголовки

#include <stdlib.h>

#include "sys/alt_irq.h"

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

#include "sys/alt_sys_init.h"

и все макросы находятся

С портами общаюсь так

IOWR_ALTERA_AVALON_PIO_DATA(FLASH_RD_BASE, 0);

d_I0 = IORD_ALTERA_AVALON_PIO_DATA(FLASH_DATA_BASE);

Автор: vadimuzzz Apr 15 2010, 08:21

да, это я неудачно скопипастил, правильный код такой:

отсюда же и растут ноги ошибки "error: `IOWR_ALTERA_AVALON_PIO_DATA' undeclared (first use in this function) test_project main.c line 6;

- macro "IOWR_ALTERA_AVALON_PIO_DATA" requires 2 arguments, but only 1 given test_project main.c line 6;" т.к. IOWR_ALTERA_AVALON_PIO_DATA, который объявлен в altera_avalon_pio_regs.h требует 2 аргумента (адрес, данные), а IORD_ALTERA_AVALON_PIO_DATA, который и должен там был стоять изначально - только адрес

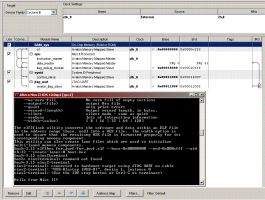

покажите ваш system.h и картинку из SOPC-билдера. пины в квартусе правильно разведены, варнингов при компиляции не кидал про ноги? лог компиляции в квартусе тоже давайте на всякий случай.

Автор: spectr Apr 15 2010, 09:09

Все заработало!

Ошибка была в том, что я использовал неправильные адреса ![]()

Сейчас, как и посоветовали, взял алиасы на них их из system.h (он, как я понимаю, генерится SOPC-билдером, да?) и все заработало.

Ключик "--go" тоже заработал (похоже что он и раньше работал, но т.к. я использовал некорректные адреса - то и не видел ничего).

Разрядность PIO также оказалась рабочей.

В общем, почти все косяки были из-за обращений к некорректным адресам )))

Спасибо за помощь!

Пока что полет нормальный - все работает четко. Начинаю втыкать как использовать загрузку с флэшки.

Автор: spectr Apr 15 2010, 13:25

Что-то аццкий Flash programmer (из IDE) орет на меня (делаю все по доке "Nios II Flash Programmer User Guide"):

#

# This file was automatically generated by the Nios II IDE Flash Programmer.

#

# It will be overwritten when the flash programmer options change.

#

cd E:/FPGA/NIOSII_Projects/test_project/Debug

# Creating .flash file for the FPGA configuration

"$SOPC_KIT_NIOS2/bin/sof2flash" --epcs --input="E:/FPGA/DE2/NIOSII/NIOSII_time_l

imited.sof" --output="NIOSII_time_limited.flash"

Info: *******************************************************************

Info: Running Quartus II Convert_programming_file

Info: Command: quartus_cpf --no_banner --convert --device=EPCS128 --option=NIOSI

I_time_limited.opt E:/FPGA/DE2/NIOSII/NIOSII_time_limited.sof NIOSII_time_limite

d.pof

File E:/FPGA/DE2/NIOSII/NIOSII_time_limited.sof contains one or more time-limite

d megafunctions that support the OpenCore Plus feature that will not work after

the hardware evaluation time expires. Refer to the Messages window for evaluatio

n time details.

Info: SRAM Object File E:/FPGA/DE2/NIOSII/NIOSII_time_limited.sof contains time-

limited megafunction that supports OpenCore Plus feature -- Vendor: 0x6AF7, Prod

uct: 0x00A2

Internal Error: Sub-system: PGMIO, File: /quartus/pgm/pgmio/pgmio_flash_mapping.

cpp, Line: 3714

ranks->size() > 0

Stack Trace:

0x1C496 : PGMIO_PCF_FILE_INFO::operator= + 0x76E6 (pgm_pgmio)

End-trace

Info: *******************************************************************

Info: Running Quartus II Convert_programming_file

Info: Command: quartus_cpf --no_banner --convert NIOSII_time_limited.pof NIOSII_

time_limited.rpd

Error: File name "NIOSII_time_limited.pof" does not exist

Error: Quartus II Convert_programming_file was unsuccessful. 1 error, 0 warnings

Error: Peak virtual memory: 66 megabytes

Error: Processing ended: Thu Apr 15 17:35:42 2010

Error: Elapsed time: 00:00:00

Error: Total CPU time (on all processors): 00:00:00

15.04.2010 17:35:42 - (SEVERE) sof2flash: Read error: File: NIOSII_time_limited.

rpd not found, exiting

15.04.2010 17:35:42 - (SEVERE) sof2flash: Error retrieving data from NIOSII_time

_limited.rpd

# Programming flash with the FPGA configuration

"$SOPC_KIT_NIOS2/bin/nios2-flash-programmer" --epcs --base=0x00009800 --sidp=0x0

000a010 --id=135841862 --timestamp=1271336990 --accept-bad-sysid "NIOSII_time_l

imited.flash"

NIOSII_time_limited.flash: Unable to open input file

Empty flash content cannot be programmed or verified

# Creating .flash file for the project

"$SOPC_KIT_NIOS2/bin/elf2flash" --epcs --after="NIOSII_time_limited.flash" --inp

ut="test_project.elf" --output="epcs_flash_controller.flash"

15.04.2010 17:35:43 - (SEVERE) elf2flash: Data error: File not found: NIOSII_tim

e_limited.flash

15.04.2010 17:35:44 - (SEVERE) elf2flash: Error retrieving data from test_projec

t.elf

# Programming flash with the project

"$SOPC_KIT_NIOS2/bin/nios2-flash-programmer" --epcs --base=0x00009800 --sidp=0x0

000a010 --id=135841862 --timestamp=1271336990 --accept-bad-sysid "epcs_flash_co

ntroller.flash"

epcs_flash_controller.flash: Unable to open input file

Empty flash content cannot be programmed or verified

Это связано с тем, что ядро time-limited? Хотя после загрузки в плату SOF он мне выдает сообщение что "time remaining: unlimited".........

Автор: vadimuzzz Apr 15 2010, 14:20

да, нужна лицензия

Автор: spectr Apr 15 2010, 14:24

Я проверил в Quartus->Tools->License Setup у процессора стоит Expiration: permanent... Это означает что лицензия корректна?

Автор: vadimuzzz Apr 15 2010, 15:29

в логах компиляции поищите "Opencores-бла-бла-бла" - если есть, значит лицензии нету.

Автор: spectr Apr 15 2010, 15:33

Да, есть такое. Курю форум, понимаю что надо пофиксить фичу. Но что-то не пойму как. Просто везде пишут про vendor_string, а в моем .dat'е такого вооооообще нет, зато есть

FEATURE 6AF7_00A2 alterad 2011.11 permanent uncounted HOSTID=0022152f62fe \

ISSUER="ICK&C 2007" SIGN="1234 5678 9ABC DEF0 1234 5678 \

1234 5678 9ABC DEF0 1234 5678 1234 5678 9ABC DEF0 1234 5678 \

1234 5678 9ABC DEF0 1234 5678 1234 5678 9ABC DEF0 1234 5678"

FEATURE 6AF7_00A5 alterad 2011.11 permanent uncounted HOSTID=0022152f62fe \

ISSUER="ICK&C 2007" SIGN="1234 5678 9ABC DEF0 1234 5678 \

1234 5678 9ABC DEF0 1234 5678 1234 5678 9ABC DEF0 1234 5678 \

1234 5678 9ABC DEF0 1234 5678 1234 5678 9ABC DEF0 1234 5678"

. Как быть?

Автор: vadimuzzz Apr 15 2010, 15:46

способа 2 - буржуйский и народный ) если интересует второй, давайте мыло

Автор: spectr Apr 15 2010, 15:47

ilkz (at) yandex.ru

Автор: vadimuzzz Apr 15 2010, 15:54

выслал

Автор: spectr Apr 15 2010, 18:13

Все получил.

Компиляция прошла без упоминаний о триальности опенкорки, так что делаю вывод что все заработает на железке (это проверю завтра).

Спасибо за помощь!

Автор: spectr Apr 19 2010, 11:59

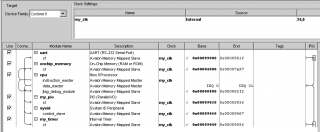

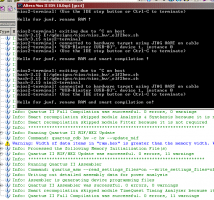

Итак, все заработало как я и ожидал. Программка и Система была простейшая - бегущий светодиод (т.е., On-chip RAM, PIO-out, контроллер EPCS, System ID, CPU). Все работало и зашивалось в EPCS на ура.

Далее я решил поиграться с прерываниями. Всего-лишь в существующую систему добавил PIO-вход (кнопочки), настроил в нем прерывания и автоназначил их в SoPC-билдере. Компилю, зашиваю, делаю в Nios II IDE простейший проект для отработки прерывания, успешно его компилирую, а далее при попытке загрузить его в плату получаю следующее фи:

Pausing target processor: OK

Reading System ID at address 0x0000A020: verified

Initializing CPU cache (if present)

OK

Downloading 00004000 ( 0%)

Downloading 00009820 (96%)

Downloaded 13KB in 0.2s (65.0KB/s)

Verifying 00004000 ( 0%)

Verifying 00009820 (96%)

Verify failed between address 0x9820 and 0x99C7

Leaving target processor paused

Насколько я понял из альтеровских и ниосовских форумов, такая ошибка возникает как правило при неверном pinout, невыполнении таймингов для внешней памяти (но у меня-то вся память - OnChip...), наводках по линии ТCK у JTAG.

В чем может быть дело?

- Pinout (Assignments для всей платы одним файлом) взят с фирменного диска, работал с ним уже сто раз на не-ниосовских проектах - все разведено нормально.

- Никакой внешней памяти кроме EPCS я не использую. Более того, раньше с ней все работало (до того как я добавил в систему PIO-вход).

- Timing Analyzer, конечно, поругивается варнингами про отрицательные слэки, но раньше же все работало. Неужели из-за добавления простого порта все так уехало?

- Вроде как, судя по адресам - это как раз флэшка. Но какого хрена она тогда раньше нормально работала?

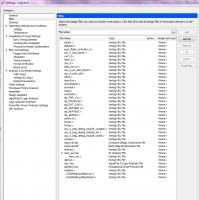

П.С.: на всякий прилагаю скриншот системы

П.П.С.: клок, если что, беру не с PLL, а напрямую с источника на плате (50 МГц).

Автор: vadimuzzz Apr 19 2010, 12:10

такое впечатление, что либо бинарник большой, либо адреса левые. как будто что-то не пересобралось (system library?) куда-то он не туда пишет, ну и проверить естественно не может. выхлоп компилятора покажите

Автор: spectr Apr 19 2010, 12:49

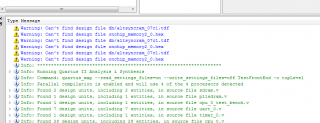

Вот отчет компилятора IDE:

make -s all includes

Compiling main.c...

../main.c: In function `init_button_pio':

../main.c:34: warning: implicit declaration of function `alt_irq_register'

../main.c: At top level:

../main.c:39: warning: return type of 'main' is not `int'

../main.c: In function `main':

../main.c:41: warning: unused variable `value'

Linking test_project.elf...

Info: (test_project.elf) 13 KBytes program size (code + initialized data).

Info: 3120 Bytes free for stack + heap.

Creating generated_app.sh...

Post-processing to create ram_memory.hex

Hardware simulation is not enabled for the target SOPC Builder system.

Skipping creation of hardware simulation model contents and simulation

symbol files. (Note: This does not affect the instruction set simulator.)

Post-processing to create epcs_flash_controller_boot_rom.flash

Build completed in 27.984 seconds

Вот простыня исходника:

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

//--------------------------------------------------------------

void delay(value)

{

int i=0;

for(i=0;i<value;i++);

}

//--------------------------------------------------------------

static void handle_button_interrupts(void* context, alt_u32 id)

{

volatile int* edge_capture_ptr = (volatile int*) context;

*edge_capture_ptr = IORD_ALTERA_AVALON_PIO_EDGE_CAP(BUTTONS_BASE);

IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTONS_BASE,0);

IOWR_ALTERA_AVALON_PIO_IRQ_MASK(BUTTONS_BASE,0xF);

}

//--------------------------------------------------------------

//--------------------------------------------------------------

//--------------------------------------------------------------

//--------------------------------------------------------------

//--------------------------------------------------------------

volatile int edge_capture;

static void init_button_pio()

{

void* edge_capture_ptr = (void*) &edge_capture;

IOWR_ALTERA_AVALON_PIO_IRQ_MASK(BUTTONS_BASE,0xF);

IOWR_ALTERA_AVALON_PIO_EDGE_CAP(BUTTONS_BASE,0);

alt_irq_register(BUTTONS_IRQ,edge_capture_ptr,handle_button_interrupts);

}

//--------------------------------------------------------------

void main(void)

{

int value = 0x00000001;

init_button_pio();

while (1)

{

if(edge_capture!=0)

{

switch(edge_capture)

{

case 0x1:

IOWR_ALTERA_AVALON_PIO_DATA(LEDS_BASE , 0x1);

break;

case 0x2:

IOWR_ALTERA_AVALON_PIO_DATA(LEDS_BASE , 0x2);

break;

case 0x4:

IOWR_ALTERA_AVALON_PIO_DATA(LEDS_BASE , 0x4);

break;

case 0x8:

IOWR_ALTERA_AVALON_PIO_DATA(LEDS_BASE , 0x8);

break;

default:

break;

}

}

}

Если это важно: в свойствах системной библиотеки параметры Program Memory и ReadOnly Memory установлены на On-Chip память.

Еще одно уточнение - процессор по сбросу и исключению уходит в память EPCS. Но в системной библиотеке, как я уже писал выше память программ и ROM-память указывают на OnChip-память. Может из-за этого косячить?

Во! Когда я изменил в свойствах системной библиотеки указание памяти программ и ROM с OnChip на EPCS, то компилятор выдал-таки ошибку, причем как раз с теми адресами, которые он выдавал при верификации:

make -s all includes

Compiling main.c...

../main.c: In function `init_button_pio':

../main.c:34: warning: implicit declaration of function `alt_irq_register'

../main.c: At top level:

../main.c:39: warning: return type of 'main' is not `int'

../main.c: In function `main':

../main.c:41: warning: unused variable `value'

Linking test_project.elf...

/cygdrive/c/altera/81/nios2eds/bin/nios2-gnutools/H-i686-pc-cygwin/bin/../lib/gcc/nios2-elf/3.4.6/../../../../nios2-elf/bin/ld: region epcs_flash_controller is full (test_project.elf section .text). Region needs to be 8908 bytes larger.

/cygdrive/c/altera/81/nios2eds/bin/nios2-gnutools/H-i686-pc-cygwin/bin/../lib/gcc/nios2-elf/3.4.6/../../../../nios2-elf/bin/ld: address 0xa2b4 of test_project.elf section .epcs_flash_controller is not within region epcs_flash_controller

/cygdrive/c/altera/81/nios2eds/bin/nios2-gnutools/H-i686-pc-cygwin/bin/../lib/gcc/nios2-elf/3.4.6/../../../../nios2-elf/bin/ld: section .rodata [00009820 -> 0000984b] overlaps section .exceptions [00009820 -> 000099c7]

/cygdrive/c/altera/81/nios2eds/bin/nios2-gnutools/H-i686-pc-cygwin/bin/../lib/gcc/nios2-elf/3.4.6/../../../../nios2-elf/bin/ld: section .rwdata [0000984c -> 0000a2b3] overlaps section .exceptions [00009820 -> 000099c7]

collect2: ld returned 1 exit status

make: *** [test_project.elf] Error 1

Build completed in 13.921 seconds

Похоже что ему мало памяти...

Автор: Sergey'F Apr 19 2010, 13:26

Я немного не понял, что Вы делаете

Когда при запуске он пытается загрузить программу и пишет:

Downloading 00004000 ( 0%)

Downloading 00009820 (96%)

Downloaded 13KB in 0.2s (65.0KB/s),

он грузит ее как бы в ОЗУ и неудивительно, что при попытке верификации EPCS он выдает ошибки. Для программирования EPCS надо использовать Flash Programmer.

По сути, область памяти от 0x9800, выделенная на EPCS контроллер - это загрузчик, который перекачивает из EPCS в ОЗУ содержимое, зашитое Flash Programmer'ом в EPCS. Тогда при включении системы загрузчик сам перекачает код из EPCS в те секции памяти, которые надо инициализировать (т.е., секции, которые лежат во встроенном ОЗУ, внешнем ОЗУ и т.д.).

Поэтому и код, и exception вектор в настройках ядра процессора кладите в ram_memory, а reset - на EPCS контроллер. Тогда при reset код из EPCS будет загружаться загрузчиком, а при загрузке с кабеля при Run - загружаться в ram_memory через JTAG.

P.S. Это вроде как в теории, сам с системами на кристалле, использующими EPCS не работал.

Автор: vadimuzzz Apr 19 2010, 14:21

Еще одно уточнение - процессор по сбросу и исключению уходит в память EPCS. Но в системной библиотеке, как я уже писал выше память программ и ROM-память указывают на OnChip-память.

на EPCS должен указывать только вектор сброса. как уже писал Sergey'F, по этому адресу живет начальный загрузчик(там маленькое ОЗУ в компонент встроено+контроллер SPI), все остальное (и системная библиотека) должно располагаться в RAM. собственно запуск программы из ниос-иде не затрагивает загрузчик. а по памяти - вроде хватает, еще 3к свободно. хотя для того, что вы привели 13к как-то многовато.

Автор: barabek Apr 19 2010, 21:37

кроме всего вышесказанного предыдущими, при использовании прерываний подключайте файл sys/alt_irq.h

Автор: Porty Apr 30 2010, 07:45

Добрый день,

возникла проблема с средой Eclipse:

Стал изучать NIOSII и начал с этих уроков (на которые ссылается сама альтера) http://electronix.ru/redirect.php?http://www.nioswiki.com/Embedded_Systems_Lab благо плата CII starter kit была в наличии

выполнил согласно их даташиту все шаги но на последнем возникла проблема в том что непонял как залить програму в процессор и запустить, т.е. не смог выполнить:

•

Right click on the software project directory and choose Run As and Nios II Hardware.

•

If the Run Configurations window appears:

Under the Project Tab: Verify Project and elf file name.

Under the Target Connection Tab: Select Refresh Connections

Select Run

т.к. фактически нет в Run Configurations пунктов отвечающих за JTAG програматор и отладчик.

Как его включить так чтоб он в среде програмирования появился?

Автор: vadimuzzz Apr 30 2010, 07:49

зашейте из квартус-программера sof, потом в ниос-иде жмите Run. при включенном jtag`е и правильном sof эклипс увидит циклон и ниос в нем (все настройки в авто). чтобы создать конфигурацию, ткните в пункт Nios II Hardware

Автор: Porty May 4 2010, 05:48

спасибо, запустил, но почему во время отладки при попытке прохода по шагам текущая выполняемая строка по F6 или F5 скачет достаточно странно (то всё линейно исполняется то назад проскакивает и тд)?

Автор: vadimuzzz May 4 2010, 12:47

включена оптимизация кода по размеру (-Os)? для отладки лучше оставить debug (-Og)

Автор: Porty May 6 2010, 06:25

спасибо, ещё вопрос: как освободить усб бластер занятый в среде ниойса для квартуса не выгружая самой среды ниойс еклипс? пробовал нажимать на красный квадрат остановки отладки/запуска не помогает.

Т.е. заливаеш в начале по джитагу прошивку из квартуса через байт бластер, потом запускаеш ниойс эклипс, заливаеш через него программу, останавливаеш выполнение, возврощаешся в квартус и пробуеш перезалить иную версию а он выдаёт:

Error: Application Nios2 on 192.168.1.14 is using the target device

Error: Operation failed

Info: Ended Programmer operation at Thu May 06 10:27:01 2010

и пока среду разработки для ниойса вообще не закроеш квартус будет выдавать такую ошибку.

Автор: vadimuzzz May 6 2010, 07:33

должен освобождаться, если отладчиком не занят. похоже баг. а отладчик что пишет в окне, где процессы висят (там типа ""thread gdb running")? если нажать красную кнопку, там должно писаться "terminated". что за операционка?

Автор: Porty May 6 2010, 08:01

win7 64bit

Автор: Porty May 7 2010, 07:14

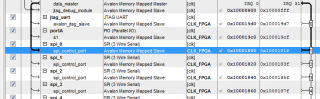

запустил один чип sdram памяти 256мегабит, 16 бит шина данных, но на плате стоит 2 чипа, с общими сигналами управления и адресом, с раздельными шинами данных (32битный модуль памяти в итоге), как их подключить в spoc билдере так чтоб одновременно шло обращение к обоим чипам в 32битном режиме?

просто выставить в настройках custom memory нельзя ибо сигналы маскирования байт будут уже для 32 бит т.е. на 4 байта, а не для 16 бит, объединять через тристейт мост авалона не хочу, т.к. насколько я понимаю они станут как 2 раздельных 16 разрядных банка памяти, а вот как их объединить в один 32битный банк памяти?

Автор: Kuzmi4 May 7 2010, 07:30

2 Porty

http://electronix.ru/forum/index.php?s=&showtopic=68235&view=findpost&p=752536 у вас http://electronix.ru/redirect.php?http://www.altera.com/products/devkits/altera/kit-cyc2-2C20N.html

то там http://electronix.ru/redirect.php?http://www.altera.com/products/devkits/altera/documents/cy2_fpga_starter_board_schematic.pdf сдвоенных SDRAM-ов ![]()

там всего по одной штучке

8-Mb SDRAM

512-Kb SRAM

4-Mb flash

Автор: Porty May 7 2010, 07:35

у меня своя плата, точнее набор. поспешили и сделали задел не продумав всю организацию памяти.

Автор: Kuzmi4 May 7 2010, 07:37

2 Porty

Тогда, наверно, дорога вам ковыряйть альтеровский SDRAM контроллер на свой лад ![]()

Автор: Porty May 7 2010, 14:10

хочу сделать согласно этому рисунку (т.е. все сигналы адреса и управления в том числе и CS запаралелены у обоих модулей):

http://electronix.ru/redirect.php?http://img708.imageshack.us/img708/3314/98895866.jpg

это кстати взято из официальной альтеровской документации (http://www.altera.com/literature/hb/nios2/n2cpu_nii51005.pdf) на sdram контроллер, но как включать такой режим и использовать упоминаний нет, просто сказано что вот он существует.

Автор: vadimuzzz May 7 2010, 14:23

а что мешает взять custom memory и скоммутировать сигналы маскирования?

Автор: Porty May 7 2010, 16:39

чтение понятно как можно скомутировать, а вот чтоб замаскировать запись необходимо либо как то не подавать сигнал записи на сам модуль что вообще невозможно без перепайки (наверное так и сделаю) ибо шины управления запаралелены, даже записывая 1 байт в память А идёт запись того же байта в память Б, т.е. нужно сделать буфер и как то сохранять те значения которые были что крайне сложно, да и смутила оригинальная документация на ip модуль памяти (что я выше выкладывал) по ней выходит что можно сделать средствами самой среды.

Автор: vetal May 7 2010, 18:02

Вы сигналы маскирования объединили или нет?

Автор: vadimuzzz May 8 2010, 05:42

а мне кажется, что просто половину DQMx на один чип завести, половину - на другой. и видиться 2 чипа x16 будут как один x32. разве нет? и во второй чип он не будет писать, если маска не установлена. или у вас на плате сигналы маскирования объединены? тогда - резать

Автор: Reanimator++ May 9 2010, 10:54

Вопрос от совсем начинающего )

Есть плата с Cyclone2, в котором Nios2 и немного логики.

Попробовал собрать и позапускать примеры - работает. Делал по мануалу hardware development tutorial.

Собрал свою систему в которой cpu, onchip_mem, uart, pio и sysid.

Модификацией примера hello_world_small добился что оно начало делать то что мне нужно. Обрадовался что все работает.

Решил добавить epcs_controller_module для того чтобы номер платы сохранять.

Добавил его в SOPC, пересобрал железо в квартусе, залил в плату.

Пересобрал софт, запускаю, IDE говорит что NIOS не отвечает.

Попробовал вернуть обратно, пересобрать заново, все-равно не отвечает. Пробовал разнообразные варианты пересборки и тыкания на все подряд, но пока результата так и не получил.

Собственно, как диагностировать почему IDE не может законнектиться к процу? Чего ему не хватает для счастья?

Автор: vadimuzzz May 9 2010, 13:57

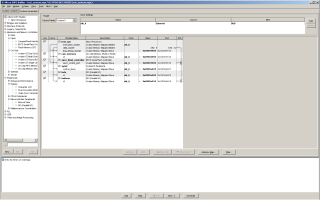

логи покажите (NIOS IDE). картинку из билдера тоже можно.

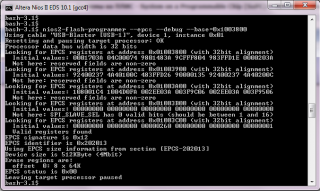

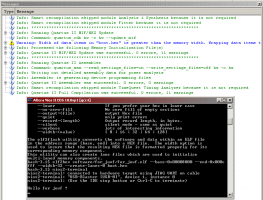

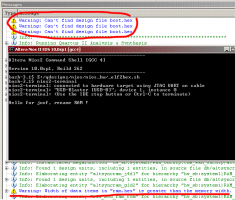

Автор: Reanimator++ May 9 2010, 14:23

Я все облазил но файла с логами IDE не нашел..

Я конфигурирую плис через Quartus Programmer, затем жму на проект Run As Nios 2 Hardware.

после успешной компиляции IDE пишет в консоли -

Using cable "USB-Blaster [USB-0]", device 1, instance 0x00

Pausing target processor: not responding.

Resetting and trying again: FAILED

Leaving target processor paused

Картинка из билдера не очень информативна.. Вложил. Еще вложил успешный лог билдера..

Автор: vadimuzzz May 9 2010, 14:51

попробуйте "Run As..", создать новую конфигурацию, что пишется? если все в "Auto", от должен сначада усб-бластер увидеть, а потом проц, что пишется?

Автор: Reanimator++ May 10 2010, 09:22

Насчет того что вы последний раз написали не совсем понял куда смотреть.

Юсб бластер видится еще когда я Quartus 2 Programmer запускаю чтобы железо проца залить в плату. А вот софт для проца уже не получается загрузить через jtag debugging module.

Я провел следующие эксперименты:

1. В глючный проект железа (не отвечающий проц) пытался залить разные софтовые проекты, в том числе не родные (для другого железа) и точно рабочие.

Результат везде один - проц не отвечает, FAILED. Причем даже до проверки sysid дело не доходит, сразу же вешается.

Сделал вывод что копаться надо в том что квартус создает.

2. Создал заново пустой проект с дефолтными настройками (мало ли что я там натыкал). Скопировал туда единственный верилоговский файлик с моей логикой и инстанциацией (фу, слово-то какое) проца. Создал заново в SOPC (протыкал мышой, а не копировал файлы) проект как на картинке (только без таймера, он мне не нужен).

Откомпилировал, залил в плату.

Создал минимальный тестовый пример из шаблона в NIOS IDE и запустил Run As Nios II Hardware.

Проц нашелся, прога отработала.

Вернулся в квартус, добавил epcs_flash_controller в SOPC, пересобрал, перекомпилировал, перезалил в плату.

В Nios IDE пересобрал тестовый пример, запустил - проц не видится, FAILED.

Вернулся в квартус, удалил epcs_flash_controller в SOPC, пересобрал, перекомпилировал, перезалил в плату.

В Nios IDE пересобрал тестовый пример, запустил - проц нашелся, программа отработала.

Т.е. добавление epcs контроллера в SOPC систему добивает проект.

В принципе меня устраивает и то что сейчас работает, но как-то не нравится мне это все, если добавление одного в принципе несложного компонента приводит к таким непредсказуемым результатам. И самое главное я не знаю как понять чего именно хочет от меня система..

Автор: vadimuzzz May 10 2010, 11:32

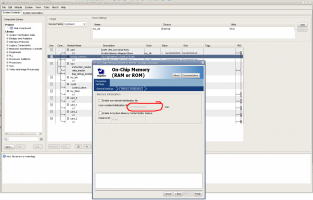

а куда reset/exception указывает (особенно в нерабочем варианте)? как конфигурируется ПЛИС? только через jtag? еще настройки system library покажите

Автор: Reanimator++ May 10 2010, 14:05

Reset - 0x00

Exception - 0x20

оба в onchip_mem, т.к. другой памяти нет. (собсно, у меня только один чип циклона на плате)

настройки system lybrary минимальные, см картинку.

впрочем, опять же я пробовал грузить даже проекты под другое железо, результат тот же, т.е. врядли дело в Nios IDE...

да и разве Jtag Debugging Module не должен отрабатывать не зависимо от того где сейчас проц исполняет код и вообще что бы там с ним ни было?

В окончательном виде платы плис конфигурируется в AS режиме из EPCS4 (к ней доступ и хотел получить для хранения номера платы.).

На время экспериментов она была пустой и все делалось через JTAG.

Автор: vadimuzzz May 10 2010, 14:10

а какая версия квартуса? тут недавно было -> http://electronix.ru/forum/index.php?showtopic=74308 была бага в самом квартусе

Автор: Reanimator++ May 10 2010, 14:15

Собственно, если в плату железо не залить совсем, то IDE ругается громко и красно, что железа нету, настойчиво предлагает сконфигурировать плис и запускает программер.

Думаю, для дальнейшего надо попробовать собрать вообще пустой проект, содержащий только проц и epcs_controller и выложить его...

Quartus II 9.0 build 132 02/25/2009 SJ Full Version, взято с torrents.ru.

Проблем с прошивкой флешки как в той теме нету, сейчас доваял рабочую прогу без доступа к epcs, создал в квартусе jic файл из sof-а, и программером закачал. При включении питания все сразу же запускается и работает.

Автор: vadimuzzz May 10 2010, 14:24

там не с флешкой проблема, а с sof-файлом, если мне память не изменяет (было на alteraforum.com). похоже, что проц даже не инитится. м.б. вдобавок к процу в систему добавить независимый (от проца) блочок, лампочкой помигать, что прошивка прошла

Автор: Reanimator++ May 10 2010, 14:29

хорошая идея ![]() , завтра попробую

, завтра попробую

Автор: Reanimator++ May 13 2010, 14:49

Мучения прервал, наткнувшись на описание своей проблемы в раздачах квартуса на torrens.ru. Человек пробовал 9-й квартус, вплоть до 9.1 SP2. Стабильную работу получил на 8.1. Видимо плохо отломали 9-й... Буду пробовать 8.1.

Автор: vadimuzzz May 13 2010, 15:09

странно, чего там ломать. на всякий случай: у меня в 9.1сп2 таких проблем не было

Автор: styuf Jun 8 2010, 05:59

Доброго времени суток всем. У меня такой вопрос - касательно лицензии - Во сколько станет лицензия на квартус + nios ii + использование uOS + TCP-IP стэк стандартный? И что именно нужно купить, что бы с этим работать? Пробовал писать проекты с крякнутым квартусом - дальше запуска примеров не ушел, так как при добавлении минимальных изменений начинает ругаться на таймлимитед функции.

Ну и естественно, если можно сломать, то я буду рад услышать как.

Автор: vadimuzzz Jun 8 2010, 06:10

по квартусу (может подойти и веб-эдишн)

http://electronix.ru/redirect.php?http://www.altera.ru/cgi-bin/price/price

по мегафункциям

http://electronix.ru/redirect.php?http://www.altera.ru/cgi-bin/go?23#n1

Автор: Iouri Jul 6 2010, 13:03

Господа,

Пытаюсь создать проект под Эклипс пробовал EDS10, with Q10, EDS9.1 with Q9.1, OS Win7.0 32 bit,

получаю собщение

: "Unable to create project" reason Failed to execute ./create -this -app --no-make

далее кликаю на кнопку детали и получаю вот такое сообщение

chmod:changing permissions of ,':Permission deniedchmod: changing permission of"/

create -this-app': Permission denied..

Подскажите в чем может быть поблема, под ХР все работает нормально

Спасибо!

Автор: torik Jul 9 2010, 04:20

Проблема в совместимости, наверное, как обычно. Ставьте Q10.0 или запускайте в режиме совместимости...

Автор: jb83 Jul 22 2010, 05:08

Здравствуйте вам.

Представим себе ситуацию: кристально честный человек ![]() хочет проектировать устройства на основе FPGA фирмы Altera (с использованием NIOS II, а также без оного) - что для этого нужно КУПИТЬ?? Погуляв немного по просторам Altera'шного сайта, я набросал такой список:

хочет проектировать устройства на основе FPGA фирмы Altera (с использованием NIOS II, а также без оного) - что для этого нужно КУПИТЬ?? Погуляв немного по просторам Altera'шного сайта, я набросал такой список:

- Quartus II Subscription Edition.

- Лицензия для NIOS II Core.

- IP МегаКорки по вкусу.

Вопросы:

1) Достаточно ли перечисленного выше набора для полноценной (не time-limited) работы?

2) Какие MegaCores идут в составе Quartus'а (или он поставляется "голый")?

3) Нужно ли в список добавить C2H Compiler (насколько он востребован и можно ли обойтись без него)?

Заранее благодарен.

Автор: des00 Jul 22 2010, 05:22

обратитесь http://electronix.ru/redirect.php?http://altera.ru/ вам дадут полный расклад на лицензионный квартус

Автор: jb83 Jul 22 2010, 08:47

у них это где-то на сайте озвучено (чего-то не по глазам

Автор: Stewart Little Jul 22 2010, 10:32

Что покупать - это зависит от задачи.

В минимальной конфигурации ничего покупать не надо - используйте Quartus II Web Edition и вариант процессорного ядра NiosII/Economy - он бесплатный начиная с версии 9.1 ЕМНИП.

Если задача более сложная, то переходим ко второму вопросу.

- Quartus II Subscription Edition.

- Лицензия для NIOS II Core.

- IP МегаКорки по вкусу.

Вопросы:

1) Достаточно ли перечисленного выше набора для полноценной (не time-limited) работы?

Для "не timelimited" - достаточно. Но полнота этого списка опять-же зависит от задачи.

Во-первых, Quartus II Subscription Edition не является жизненно необходимым. Под большое кол-во задач хватит и Web Edition'а.

Далее - планируете ли Вы моделировать Вашу систему? - Если да, то добавляйте в список ModelSim-Altera Edition (платную версию) или ModelSim-Altera Starter Edition (эта версия бесплатная, но у нее имеется ограничение на кол-во строк симулируемого кода - до 10000 строк, ЕМНИП).

Планируете ли Вы использовать ethernet? Если да, то добавляйте в список стек протоколов InterNiche.

Планируете ли Вы использовать RTOS? Если да, то добавляйте в список ось по Вашему выбору.

И т.д.

Вместе с квартусом инсталлируется вся библиотека альтеровских ip-ядер (полный список см. на сайте у альтеры). Для них требуется приобретение лицензий.

Особая песня - периферийные устройства, входящие в состав библиотеки SOPC Builder'а - они лицензирования не требуют.

Если планируете использовать аппаратное ускорение сишного кода - то включайте. Если нет, то и не надо.

Автор: jb83 Jul 22 2010, 13:54

А если прикрутить один из многочисленных опенсорц TCP/IP стеков (тот же uIP, например)? или это для начинающего слишком замороченная задача?

Автор: vadimuzzz Jul 23 2010, 06:30

можно даже использовать опенсорц IP-ядра, тот же Ethernet MAC. а халявы нигде не будет, чуть дальше "hello world" - придется разбираться.

Автор: Shaggy Aug 3 2010, 13:26

Здравствуйте, подскажите пожалуйста в NIOS возможна ли такая вставка

f=fopen("Massiv.txt","r");

fscanf(f,"%d",&c);

fclose(f);

Необходимо считать данные из файла, чтобы потом погрузить их в ПЛИС. Может быть есть какие-то еще варианты, для того чтобы вытащить из файла данные?

Автор: vadimuzzz Aug 3 2010, 14:13

разумеется, возможно, но:

файловые операции предполагают наличие файловой системы, а конкретно вызовы fopen, fscanf и т.п. - использование библиотеки stdio. что, вообще говоря, для систем с ниосом вовсе не обязательно. из вашего вопроса не ясно где находится файл и кто в ПЛИС является потребителем. телепаты в отпуске, да ![]()

Автор: Shaggy Aug 4 2010, 05:25

с=0;

FILE *f;

f=fopen("D:\Massiv.txt","r");

fscanf(f,"%d",&c);

fclose(f);

Это всего лишь пример... Проблема заключается в том,что в значение переменной не изменяется. Как был 0 так он и остался, в Borland c++ все работает.

Может быть есть еще какие-нибудь варианты чтения из файла???

Автор: vadimuzzz Aug 4 2010, 05:47

используете host-base file system? читайте здесь http://electronix.ru/redirect.php?http://www.altera.com/literature/hb/nios2/n2sw_nii52005.pdf, раздел "Using File Subsystems". там есть нюансы, типа "работает только в режиме отладки". ну и компоненты соответствующий д.б. включены в BSP

Автор: Shaggy Aug 4 2010, 07:00

Спасибо большое за помощь. Расставление галочек эта какая-то беда... Стоило поставить галочку и все заработало.

Автор: Shaggy Aug 4 2010, 13:10

Возник следующий вопрос.

Читаю из текстового файла данные (значения пикселей картинки 256х256) полученные в Borland C++ в массив созданный в NIOS II. Затем этот массив записываю в новый файл. И этот новый файл открываю в Borland. Проблема в скорости чтения/записи данных. Данные в новый файл пишутся несколько минут.

Автор: Shaggy Aug 6 2010, 06:53

Добрый день подскажите пожауйста в SOPC Builder собрал системку, она сгенерировалась без проблем, но при компиляции проекта на стадии анализа выдается ошибка "Data size does not match the number of bytes at line 65537 in Hexademical (Intel-Format) File "onchip_memory2_0.hex"".

Автор: vadimuzzz Aug 6 2010, 07:26

наверное, остался от компиляции программы в эклипсе. можно удалить файл и сгенерить систему заново

Автор: Shaggy Aug 6 2010, 07:56

Подскажите пожалуйста от чего зависит скорость обмена данными между макетом и компьютером. в NIOS II открываю файл fopen(), записываю в массив, затем этот массив при помощи fprintf() записываю в другой файл. Но данный процесс занимает подозрительно много времени. Исходный файл содержит информацию о значении пикселей картинки 256x256, а получаемый файл тоже значения пикселей,только после ДКП-ОДКП. Выполнение преобразования я отключил, так что просто пишу теже данные. Почему процесс чтения-записи происходит так долго?

Автор: vadimuzzz Aug 6 2010, 08:51

долго это сколько? а так, первое что на ум приходит - слишком много уровней абстракции, не все из которых документированы. примерно такая цепочка: драйвер ФС хоста -- библиотека обмена по JTAG -- JTAG -- ФС Ниоса -- библиотека stdio. последние 2 пункта скорости никак не прибавляют.

Автор: Shaggy Aug 6 2010, 08:54

Порядка 2-х 3-х минут.

Автор: _VM Oct 6 2010, 11:48

Всем привет!

В этой теме уже http://electronix.ru/forum/index.php?showtopic=68235&view=findpost&p=745221 вопрос о триальности open-core.

Собственно, я с ним тоже столкнулся.

Ездил на 9.1 все нормально было, пересел на 10.0 и заглох.

Добавлю, генерится time limited sof, который загружается и работает.

При загрузке программером квартуса выводит окно типа: "нажми cancel и у тебя все встанет".

Действительно, прошивка работает (проверяю пингом самодельный TCP/IP стек) пока не нажмешь на кнопку.

Как понимаю предлагается купить ниос .

Мож есть народное средство

Автор: _VM Oct 6 2010, 15:28

В этой теме уже http://electronix.ru/forum/index.php?showtopic=68235&view=findpost&p=745221 вопрос о триальности open-core.

Собственно, я с ним тоже столкнулся.

Ездил на 9.1 все нормально было, пересел на 10.0 и заглох.

Добавлю, генерится time limited sof, который загружается и работает.

При загрузке программером квартуса выводит окно типа: "нажми cancel и у тебя все встанет".

Действительно, прошивка работает (проверяю пингом самодельный TCP/IP стек) пока не нажмешь на кнопку.

Как понимаю предлагается купить ниос .

Мож есть народное средство

Проблема решилась перепиской с участниками форума.

Автор: nkie Oct 19 2010, 06:02

Здравствуйте, господа форумчане. У меня чайниковский вопрос. Тут где-то прочитал, что если программа для ниос не очень большая, то ее можно зашить одновременно с конфигурацией fpga одним pof файлом. Не подскажите как это сделать? Что-то никак не найду. Просто конфигурацию для ПЛИС мы делаем в SOPC билдере, а программу пишем в NIOS EDS, который создает свой файл и не изменяет первичный pof. Разве не так? Или я ошибаюсь...

Автор: vadimuzzz Oct 19 2010, 06:19

при сборке программы создается hex-файл для памяти, его можно вшить в sof(pof). для этого нужно настроить вектор сброса на on-chip memory, туда же слинковать программу. после каждой линковки hex-файл будет обновляться, не забывайте запускать Assembler в квартусе. ну, и вариант с бутлоадером тоже никто не отменял.

Автор: Serhiy_UA Oct 19 2010, 06:35

Все делайте согласно прилагаемого ug_nios2_flash_programmer.pdf, если у Вас QII 7.2

А точнее, раздел "2. Using the Flash Programmer in IDE Mode"

Какой пункт в нем не ясен?

Автор: nkie Oct 19 2010, 06:40

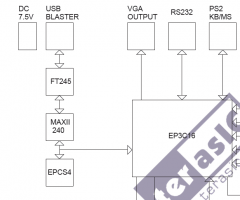

Можно ли такой же финт сделать с rbf файлом? У меня просто несколько странная система. Cyclone грузится rbf файлом из компьютера через MAXII по PS. Т.е. моя собственная прога берет rbf и сует через MAXII в Циклон. На Циклоне не JTAG-а ни чего больше нет. Хочу поиграться с НИОСОМ. Алтеровской платы у меня тоже нет. Развел отдельную плату со всеми возможными интерфейсами конфигурации но пока она в производстве, хочется хоть как-то этот НИОС пощупать... Вот и хочу конфигурационный файл с прошивкой слепить в rbf файл и залить по-старому... Реально ли это?

Автор: vadimuzzz Oct 19 2010, 07:09

а в чем проблема? берете sof, как я выше описывал, конвертируете в rbf

Автор: nkie Oct 19 2010, 07:34

да проблема в том, что в проекте нет никаких flashmemory девайсов да и на плате их нет. А FlashProgrammer матерится на это когда я ему пытаюсь скормить .sopcinfo. Может закинуть какой нибудь флеш контроллер в проект надо... А все вектора в on-chip оставить... ?

Автор: vadimuzzz Oct 19 2010, 07:48

зачем ва флеш-программер, если флеша нет

Автор: nkie Oct 19 2010, 08:23

1. Собираю проект в SOPC-билдере. Самый простой первый туториал, где леды...

в настройках процессора ставлю reset и exception на on-chip

2. Генерю систему, получаю .sopcinfo

3. Компилирую проект в Квартусе, получаю .sof(.pof/.rbf)

4. Открываю NIOS EDS, подключаю там .sopcinfo, открываю пример count_binari, компилю его... получаю .elf

Что куда теперь подсовывать? Опять надо квартовский ассемблер на кого-то натравить? И какое место во всей этой истории занимает Flash Programmer?

Автор: vadimuzzz Oct 19 2010, 08:34

внимательно смотрите выхлоп консоли во время сборки, там пишется какие файлы (в т.ч. hex созданы/обновлены) hex лежит в основной папке проекта, не в software

просто запустите ассемблер, сгенерируется sof, потом конвертируйте его в rbf. флеш-программер вам не нужен

Автор: nkie Oct 19 2010, 09:26

Все, нашел где эти опции замены .hex файла... Спасибо за помощь

Автор: nkie Oct 20 2010, 12:44