Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Mentor PADS _ Hyperlynx FPGA DDR3

Автор: uriy May 1 2018, 18:41

Не проходит Batch simulation в разделе Data read. Пишет Bad signal. Data write проходит и сигнал там заметно лучше.

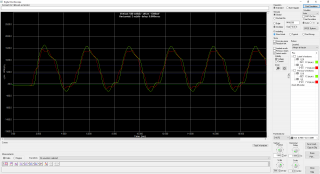

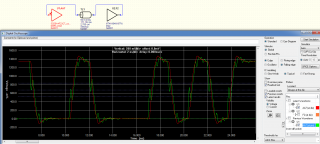

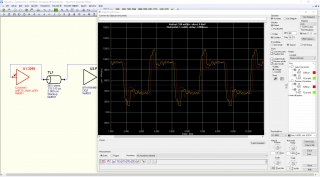

Вот так выглядит сигнал FPGA->DDR (Data write). DDR Batch simulation он проходит.

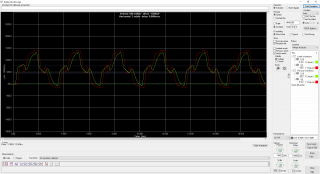

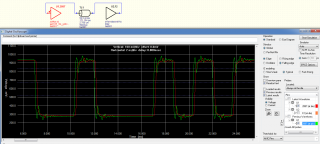

А вот так выглядит та же самая линия в обратном направлении DDR->FPGA (Data read). В DDR Batch simulation пишет Bad signal.

Что с этим делать?

FPGA->DDR (Data write) проходят без проблем все 16 бит шины. В обратную сторону DDR->FPGA (Data read) не проходит ни один.

Автор: Uree May 1 2018, 21:47

А что за модели драйверов выбраны? И клок 300МГц на линии данных - почему?

Автор: uriy May 2 2018, 15:00

Модели прицеплены в архиве.

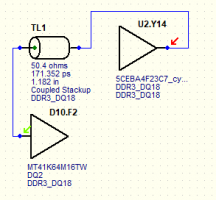

Сигналы, приведенные выше, соответствуют ноге F2 для памяти и Y14 для циклона.

В sweeps я посмотрел все сочетания входов и выходов. Там нет существенных различий.

300 Мгц хочет заказчик. ibis.zip ( 1.35 мегабайт )

: 14

ibis.zip ( 1.35 мегабайт )

: 14

Эквивалентная схема этой линии

Автор: Uree May 2 2018, 21:51

У меня несколько иначе получается.

Запись в память:

Чтение памяти:

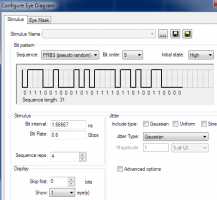

В обоих случаях PRBS 31bit 600Mbps:

Зеленый - сигнал на пине, красный/оранж - на чипе(at die).

На пине выглядит не особо, но на самом приемнике уже вполне ничего.

А вообще странно, что в модели sstl135 для FPGA не упоминается какой величины терминирующий резистор используется. Потому как 34 и 40 Ом это для передачи(последовательный резистор), а на приеме обычно 20-30-40-60-120 доступны, и например для ARRIA10 именно такие драйверы прописаны:

Автор: uriy May 3 2018, 02:26

У вас форма сигнала получилась значительно лучше моих! Может я что-то неправильно делаю.

Может вы какие-то глобальные параметры меняли? Раскажете свой порядок действий?

Модель была взята отсюда http://electronix.ru/redirect.php?https://www.altera.com/support/support-resources/download/board-layout-test/ibis/ibs-ibis_index.html

Но в таком виде Hyperlynx ее не принимал.

Ее товарищ прогнал через Quartus кажется.

Автор: Uree May 3 2018, 05:42

Обычный порядок, поставил два драйвера, назначил их, добавил линию передачи и просимулировал. Дело не в порядке. В Вашей модели и в моей наверняка отличается линия передачи, отсюда и разница возникает.

Но правильнее было бы взять не эту модель для FPGA, а модель с терминацией. Посмотрите "IBIS Models User Guide" - там в начале идет расшифровка обозначений моделей. Для корректной работы такой линии в режиме чтения памяти в FPGA нужна терминация, т.е. в названии модели должно быть что-то из этого:

g20c - 20ohm parallel on-chip Termination with Calibration

g30c - 30ohm parallel on-chip Termination with Calibration

g40c - 40ohm parallel on-chip Termination with Calibration

g50c - 50ohm parallel on-chip Termination with Calibration

g60c - 60ohm parallel on-chip Termination with Calibration

g120c - 120ohm parallel on-chip Termination with Calibration

Использованная модель sstl135_ctpio_r34c_ms5 этой терминации не имеет(по крайней мере исходя из ее названия), отсюда и плохой результат в направлении DDR->FPGA.

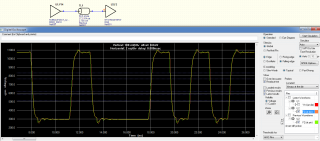

Я пробовал с моделью sstl135_rtio_g40c_r34_lv для ARRIA10 (вряд ли они используют для чипов одного поколения разные драйвера, должно быть то же, что и в CYCLONE V или очень близко к нему) и получил вот такой сигнал:

Как и в предыдущих случаях зеленый - на пине, красный - at die.

В исходнике IBIS для CYCLONE V модели разделены на источники и приемники. Т.е. Вам нужно для записи в память использовать модель sstl135_ctpio_r34c (или _r40c, смотря что лучше), а для чтения из нее sstl135_сtpin_g40c (или _g30c/_g60c опять же по результату моделирования).

Разве что Quartus объединяет io+in, но тогда нужно выяснять какую именно терминацию он включил в использованную sstl135_ctpio_r34c_ms5.

Автор: uriy May 3 2018, 06:00

Я думал вы мои IBIS модели использовали...

Автор: Uree May 3 2018, 07:00

На первых скринах именно они. На последнем - ARRIA. Там же видно, над сигналом схема и названия моделей на ней.

Я просто к тому, что мне кажется модель драйвера пинов FPGA выбрана не совсем правильно. Либо Квартус странно скомпилил целевой IBIS файл.

Автор: fill May 3 2018, 07:29

Если взять модель с согласованием из исходного файла альтеры, то

Форма сигнала очень сильно зависит от выбираемой модели приемника и параметров передающей линии.

Русская версия Invision Power Board (http://www.invisionboard.com)

© Invision Power Services (http://www.invisionpower.com)