Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Работаем с трассировкой _ Рекомендации по трассировке DDR3

Автор: Шухарт Mar 1 2018, 06:15

Добрый день, форумчане.

Возникла необходимость разместить на плате две DDR3 (MT41J128M16JT, площадка под шар - 0.3мм, зазор - 0.5мм) и подключить их к двум банкам процессора XC6SLX75-3FGG484C (площадка под шар 0.4 мм, зазор 0.6мм)

Вообще с DDR раньше не работал, требования к трассировке этого интерфейса (как от микрона так и от ксайлинкса) уже посмотрел. Хотелось бы получить именно рекомендации по стекапу печатной платы и по размещению микросхем друг относительно друга.

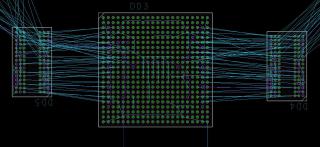

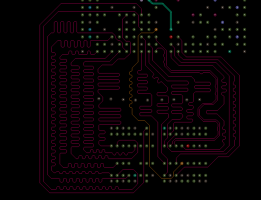

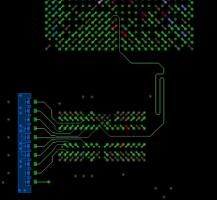

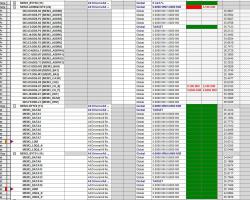

Пока-что прикидочно разместил их как на фото. Резинки, которые тянутся в углы от резисторов, подтянутых к Vtt.

Хочу сделать восьмислойную ПП со сквозными переходными.

1-TOP

2-GND1

3-Int1

4-PWR1

5-PWR2

6-Int2

7-GND2

8-BOT

Автор: Uree Mar 1 2018, 07:52

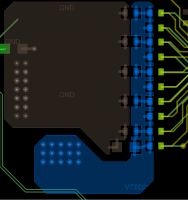

Слоев хватит. Пинаут нужно будет подбирать. А ставить чипы памяти удобней стороной данных к FPGA, так больше доступного места для цепей данных и легче их выравнивание:

Автор: Шухарт Mar 1 2018, 09:47

Спасибо. А что такое пинаут? Fanount знаю, а этот термин впервые услышал

Автор: Uree Mar 1 2018, 10:16

Наверное распиновка будет самым близким понятием. В смысле нужно будет подбирать на какие выводы FPGA какие сигналы памяти нужно подключить. То, что линии связи выглядят "почти прямо" на скриншоте в итоге может слабо соотноситься с тем, как будут лежать трассы этих сигналов.

Автор: EvilWrecker Mar 1 2018, 10:37

Пинаут никто не подбирает, подбирают обычно свапинг наиболее удачный

- наезжания дырки виа прямо на пад?

- разного количества соединения с противоположных электродов bulk cap?

- teardrop к тонкой трассе фанаута идущей с мелких конденсаторов?

Ну и чисто так- а какая, если не секрет, геометрия диффпар на стробы вышла? И сколько "в среднем" зазор вышел между битам?

Если я правильно понимаю вашу картинку у вас планки раскиданы на разные каналы, т.е. шина адресов/команд у них разная. Учитывая возможности спартана есть некоторые сомнения что вешняя терминация тут нужна

Вы лучше сначала остальное на вашей плате раскидайте- трассы, банки на спартан и память, всех соседей и там уже беритесь за ддр.

Автор: Шухарт Mar 1 2018, 11:07

Мне тут как раз недавно дали фото образца с аналогичными микросхемами. Там по бокам и снизу платы есть эти резисторы. Плюс есть схема другого рабочего устройства, и там тоже эти резисторы в наличии

Это по сути самый критичный участок схемы, связи чётко закреплены за ногами спартана, поэтому хотел сразу определиться со стекапом печатной платы, переходными и шириной дорожек

Автор: EvilWrecker Mar 1 2018, 11:24

Нет, конечно если внешняя терминация будет то ничего плохого не случится

Связи закреплены за его контроллером памяти, но биты/байтлейны можно свапить.

Т.е. вы хотите сказать что волновое не считали а просто выбрали количество слоев и все?

А разводка с приложенной картинки очень инновационная- особенно в части зазоров и выравнивания

Автор: Шухарт Mar 1 2018, 11:56

Т.е. вы хотите сказать что волновое не считали а просто выбрали количество слоев и все?

А разводка с приложенной картинки очень инновационная- особенно в части зазоров и выравнивания

По поводу свапа, да, нашёл "DQ bit swapping at the memory interface is permitted to facilitate layout. Swapping should only be done within a data group"

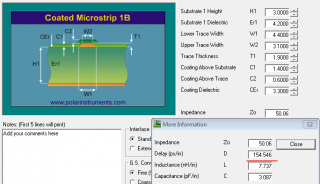

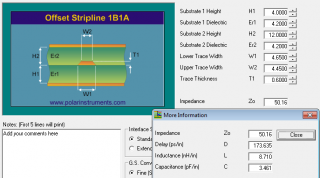

Нет, не считал. Ну я знаю что для адресов он должен быть 40 Ом, но ведь этого можно достичь играясь с толщинами препрегов и ядра, или я чего-то не улавливаю?)

То есть на фото далеко не эталон разводки?)

Автор: EvilWrecker Mar 1 2018, 12:14

Совершенно напрасно.

Знаете откуда?Кто вам такую глупость сказал?

Можно, но еще играются толщинами трасс и Dk- в конце игры может быть как хороший оптимизированный стек, так и то что согласятся делать немногие за приличные деньги

Смотря эталон чего- но если речь "о типа хорошей разводке" то нет, не он

Автор: Шухарт Mar 1 2018, 12:26

Micron TN-41-08: Design Guide for Two DDR3-1066:

Trace width = 5 mils: target 40Ω impedance

Trace space = 12 to 15 mils, reducing to 11.5 mils between the pins of the DIMM

Trace space from DIMM pins = 7 mils

Trace space to other signal groups = 20 to 25 mils

Автор: EvilWrecker Mar 1 2018, 14:49

Т.е. вы считаете что во всех дизайнах один и тот же target impdance?А у вас стало быть UDIMM?

Автор: Uree Mar 1 2018, 20:58

Свапинг - процесс замены, глагол, его делают.

Пинаут ака распиновка - получившаяся в результате свапинга схема подключения.

Автор: EvilWrecker Mar 2 2018, 00:02

Да неее, http://electronix.ru/redirect.php?https://en.wikipedia.org/wiki/Pinout это нечто более жесткое, привязанное к именно к физической структуре камня. Применительно к тому же ддр3, пинаут это то как выглядит схемный символ, а результат свапа это то как легли нетлейблы битов, которые вестимо могут не соответствовать таковым в символе(в чем и есть суть свапа). Т.е. после свапа получается не пинаут а swap table ![]() которая существует обособленно.

которая существует обособленно.

Впрочем черт с ним с этим пинаутом, вы лучше скажите что там с конденсаторами и диффпарами- интересно же.

Автор: Uree Mar 2 2018, 07:54

Ничего там интересного, конденсаторы стоят, диффпары лежат, устройства работают. Мы тут как бы Шухарту помогаем, а не мой дизайн обсуждаем.

Автор: EvilWrecker Mar 2 2018, 08:19

Ага, ясно

Соглашусь, надо пояснить ТС откуда вопрос возник- на основе предыдущих диалогов с Uree у меня сложилось мнение что он большой поборник cost reduction DFx practices(если можно так выразиться) а то что на его картинке, как мне кажется, не совсем этому соответствует. Ну а про конденсаторы интересно в том числе и "во временной области": например, возник ли такой дизайн до или после того, как Tosha1984 развалил все удивительные теории из http://electronix.ru/redirect.php?https://electronix.ru/forum/index.php?showtopic=142825&st=15 ветки

Автор: Uree Mar 2 2018, 10:05

Я не поборник чего-бы то ни было. Есть требования заказчика - дизайн делается согласно ним. Есть требования по цене - надо сделать соответствующе, иначе можно вообще не делать, ибо не купят.

Дизайн на скрине 15-го года. Такой подход к дизайну весьма давний, до 10-го года точно уже так делали.

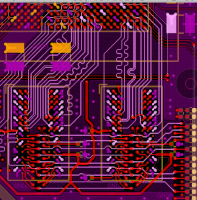

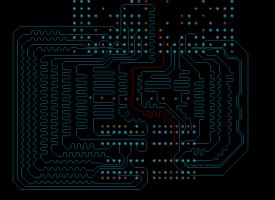

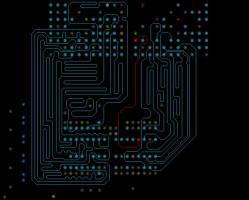

Только и далее непонятно как это относится к теме топика? ТС нужно определиться с числом слоев - для его дизайна предполагаемых восьми должно хватить, хотя к внешним от FPGA рядам пинов подводить сигналы будет неудобно, придется как на фото обводить часть из них вокруг. Это в свою очередь увеличит их длину, и сделает весьма заметной разницу между длинами к пинам на внутренних рядах и на внешних, в итоге нужно будет достаточно сильно морочить себе голову их выравниванием. Именно поэтому и написал о том, что удобнее будет ставить память так, как на моем скриншоте и привел его только как иллюстрацию примера расположения чипов памяти относительно FPGA. Все остальные детали на скрине к данному вопросу не относятся.

Хотя иногда и так как у ТС приходится делать, да еще и с крайне неудачным пинаутом хоста. Но можно. Как-то вот так, на 3-х сигнальных слоях(всего 6-ти слойка плата):

Автор: EvilWrecker Mar 2 2018, 11:25

С моей стороны это не более чем ирония

Бесспорно.

Нет ничего проще- вы привели картинку в рамках аргумента, а я проявил интерес.

Мне кажется что на такой лопате вполне возьмет автомат- тем более что судя по скринам у ТС аллегро. А там автомат далекооо не дохлый, да и вообще- везде где можно выровнять только аккордеонами справится и автомат(из аллегро, подчеркиваю

Я и не скрываю того факта что это сугубо мое любопытство.

Это неплохой пример, но тут вас спасает корпус(бга) и явно "медленная" память. Наверное более удачный пример это всякие Wi-FI SoC для роутеров, у которых и сигналы на фронтенды надо вывести, и ддр(3), а сами они в каком нибудь 2-х-рядном qfn. То есть 4 слоя на все.

Автор: Uree Mar 2 2018, 11:55

Ммм... как-то давно не видел серъезных чипов в не-BGA исполнении, тем более SoC-ов. Слишком уж много пинов у них, чтобы это можно было реализовать в QFNe.

Хотя есть конечно паршивые овцы, типа VSC7511, именно в 2-х рядном uQFN-173(правда это не SoC а всего лишь PHY и там минимум внешних интерфейсов). Плевались от него все, начиная с нас при проектировании платы с ним на борту и заканчивая производством, для которого BGA куда предпочтительнее.

Ну а те SoC-и которые используем не на 4-х, но на тех же 6-ти слойках вполне себе реализуются.

Автор: EvilWrecker Mar 2 2018, 12:08

Ну вам везет значит(без сарказма)- взгляните на какой нибудь IPQ4018. Байтлейны идут нормально а адреса/управление через задницу- там буквально если перекинуть сигналов 5-7 внутри кристалла можно было бы сделать так что все разводилось в одном слое. Но и как есть встает на 4х слоях.

Небось интел или медиатек?

Тут к сожалению(или к счастью) у меня нет особых компетенций- с Vitesse/Microsemi не сказать чтобы много их разводил, все больше марвелы/реалтеки и немного меланоксов. А какие проблемы были с VSC7511?

Автор: Uree Mar 2 2018, 13:16

Интел, именно как Интел очень редко, в основном Broadcom-Xilinx-Altera(которая теперь тоже под вывеской Интел, да).

В проектировании никаких, кроме того, что распиновка дурацкая(засунуть дифпары во внутренний ряд пинов очень "отличное" решение). А в продукции с ними качество пайки хромает, часть плат приходится догревать феном чтобы заработали. Все-таки сочетание огромного термалпада на брюхе и очень мелких(по площади меньше чем у обычного BGA с шагом 1мм) падов в два ряда по периметру неудобное в реализации на продукции.

Автор: EvilWrecker Mar 2 2018, 13:51

Ну это не самый плохой вариант- у интела почти все камни отлично оптимизированы по пинауту, плюс очень и очень неплохие PDG и прочие гайды. Правда надо отметить что дизайн-чек самого интела более менее адекватный в рамках повторения в ключевых областях их референсов(ведь никто не отменяет индусских PhD) но по итогу в плане разводки как таковой там практически нет челенджей, т.к. все сделано уже и так "для людей".

Понятно, по описанию очень похоже на IPQ4018- там тоже многие критические сигналы лежат на втором ряду, но здесь скорее всего имеет место быть расп**во тамошних индусов/китайцев: как правило, то что рекомендует производитель по футпринтам требует некоторой доработки напильником, особенно если речь идет о масс-продакшне. Но тут есть другой момент: многие думают что media SoC и RF SoC используют тот же подход в разводке(что неправда) и то что прокатывало на всяком юниорском мусоре типа сет-топ-боксов прокатит в каком нибудь 5G WiFI

Автор: Uree Mar 2 2018, 14:14

Опять намешали не пойми чего... DFx - это одно, RF-performance - совсем другое. И то и то реализуется параллельно, по возможности без влияния друг на друга. И "юниорски мусорные" СТБ с 2-х диапазонными 4-х канальными WiFi тоже есть. И с перформансом там все в порядке, и продукция не жалуется.

Автор: EvilWrecker Mar 2 2018, 14:27

Да, но бывает так что какие то отдельные аспекты позитивное влияющие на RF perfromance имею негативный отпечаток в DFx. В реально хайспидных дизайнах они почти всегда пересекаются и враждуют в тех или иных областях.

Я видимо неправильно выразился- это разумеется совершенно не выпад конкретно против вас, просто речь о том что STB это одни из наиболее простых задач в части псб дизайна, практически вне какой-либо зависимости от "крутости" начинки. Просто есть люди которые хотя бы единожды реализовав такой хардвар(который в абсолютно подавляющем большинстве случаев сводится к повторению референса "в лоб") имеют неоправданно высокое чсв

Но вернемся к DFX- даже в рамках STB(и не только) многие просто копируют куски дизайна даже на уровне футпринта: а фигли, это же делала известная западная компания

Автор: Uree Mar 2 2018, 14:59

Не очень понимаю, как одно связано с другим(DFx vs performance). Почему они вдруг должны друг другу мешать??? Ну понятно, что сферически идеальный дизайн в вакууме должен быть максимально простым для продукции(возможность спаять-собрать-протестить "на коленке") и при этом обеспечивать параметры максимальные из тех, которые гарантируются производителями отдельных его элементов. Так же понятно, что физически это нереализуемо и каждый дизайн есть компромисом между ценой(DFx где-то здесь как одна из составляющих) и производительностью. Не интересует цена - гоним производительность до макс. достижимого максимума и наоборот, делаем максимально дешево лишь бы не пострадала конечная функциональность.

Но как правило получается сделать и то, и другое, без ущерба друг для друга. Я не вижу тут каких-то противоречий.

Кстати копировать не люблю и всячески пытаюсь против него бороться на нынешнем месте работы. Хотя надо признать - если стоят острые сроки работы то весьма удобное решение![]() , по крайней мере какие-то части референса. С одной стороны быстро, с другой стороны гарантировано будет работать. С третьей стороны остается четкое ощущение, что "не все выжато" из имеющегося дизайна, что-то еще можно было подправить и т.д.

, по крайней мере какие-то части референса. С одной стороны быстро, с другой стороны гарантировано будет работать. С третьей стороны остается четкое ощущение, что "не все выжато" из имеющегося дизайна, что-то еще можно было подправить и т.д.

А что там с конденсаторами такое непонятное?

Дырки на пады не наезжают, они стоят без зазора, но не наезжают, просто на скрине еще солдермаска больше чем медь, она дает такой эффект.

Кол-во соединений одинаково - по одному или по два ВИА на каждый пад до слоя с питанием и соседней ему землей. Термалы к шейпу земли на внешнем слое особо вклада в работу конденсатора не вносят.

Третий вопрс вообще не понял о чем.

Да, и мы опять ушли от темы.

Автор: EvilWrecker Mar 2 2018, 15:17

Немного искусственный пример но тем не менее- чем выше "скорости" в дизайне, тем более он тяготеет к L плотности футпринтов, для снижения емкости емкости. Бывает некоторые заходят в этом начинании так далеко, что взаправду удивляешься их успеху:ультимативно порезанные пады, как запаивают- черт знает.

Это заслуживает уважения.

Так и есть.

Ну то есть край дырки лежит на границе пада?

Нет, может мне мерещится но они же неодинаковые для bulk caps- разное количество на электродах.

UPDATE: да, мне мерещится- беру свои слова обратно

Термалы у вас вполне себе, не прикопаться. Сам бы делал так же примерно

Представьте на секунду что вы внезапно сделали трассу к виа по ширине равное паду этого самого виа. Так и зачем тиардропы?

Автор: Uree Mar 3 2018, 17:22

Примерно так, если совсем точно, то 0.05мм от пада.

Тоже видимо несколько обманный оптический эффект. Тирдропы настроены для переходных(0.5мм диаметр) и линий шириной до 0.25мм.

А на скрине нет линий шире чем 0.35мм и эти линии уже без тирдропов на переходных.

Автор: EvilWrecker Mar 3 2018, 19:28

А зачем? Как выбрано такое расстояние?

Да, видимо так и есть.

Автор: Uree Mar 3 2018, 21:14

Фабрика допускает такое расстояние без тентирования ВИА и без утекания в них пасты. Ну или даже если утекает, то не критично для качества пайки. Им конечно хочется еще дальше, дабы уж совсем безопасно было, мне хочется в центре пада, но как обычно - компромисс.

Автор: Шухарт Apr 19 2018, 07:40

Добрый день. В руководстве на Спартан касательно памяти есть пункт -DQ bit swapping at the memory interface is permitted to facilitate layout. Swapping

should only be done within a data group.

Поясните пожалуйтса. У меня есть данные DQ[0-15]. Правильно ли я понимаю, что я могу внутри DQ[0-7] (и соответственно внутри DQ[8-15]) произвольно менять контакты местами? То есть к примеру DQ2 и DQ5 поменять местами? И это не повлечёт никаких изменений в прошивке и прочем?

Автор: Uree Apr 19 2018, 07:43

Правильно, так и есть. Куда положили бит, оттуда и взяли, а какой у него номер не важно.

Автор: Шухарт Apr 20 2018, 12:11

Спасибо.

Правда мне коллега уверяет что DQ0 и DQ8 нельзя трогать. Он заблуждается или это какое-то исключение?

Автор: Uree Apr 20 2018, 12:30

Это надо проверять по какой линии работает write-leveling в контроллере и в самой памяти. Если строго в нулевом бите - то придется оставлять его на месте и менять только остальные семь.

Автор: Шухарт Apr 20 2018, 13:08

Похоже лучше их не трогать от греха подальше)

Автор: EvilWrecker Apr 20 2018, 13:14

Что за чушь, сколько раз уже было за это http://electronix.ru/redirect.php?https://forums.xilinx.com/t5/Memory-Interfaces/possible-to-swap-pin-at-DDR3-memory-side/td-p/164558- свапьте спокойно, нету там фиксированных битов.

Автор: Шухарт Apr 23 2018, 06:42

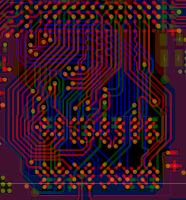

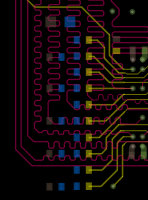

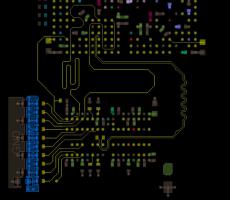

В итоге вышел каменный цветок. Прошу оценить и раскритиковать)

1-TOP

2-GND1

3-Int1

4-PWR1

5-PWR2

6-Int2

7-GND2

8-BOT

На L3 у меня справа Byte0 (32мм), слева- Адреса и команды длиной 62мм

На L6 у меня справа Byte1 (32мм), слева- Адреса и команды длиной 62мм

На топе сигнал RAS и подтягивающие резисторы

Снизу платы дифпара CK, два адреса и RST#, резисторы и кондёры

И сразу вопрос, какой длины надо делать дифпару CK? Сейчас она около 55мм.

У ксайлинкса написано -CK and DQS trace lengths must be matched (±250 mil) to maximize setup and hold

margins. То есть мне её по хорошему надо сократить до 32мм. С другой стороны где-то читал что клок должен быть равен или даже длинее адресов.

Автор: bigor Apr 23 2018, 09:03

Как то слишком много получилось...

Неужели короче нельзя было?

Да и есть ли смысл ровнять на столь малом расстоянии?

И терминаторы с конденсаторами следует заменить на 0402.

Автор: Шухарт Apr 23 2018, 09:17

Неужели короче нельзя было?

Короче? Байты точно нельзя было. Максимальный адрес первоначально был 50мм, пришлось сдвинуть его влево (нарастив на 10мм) чтобы внутри этого кольца дуги других дорожек уместились.

Я не знаю. В рекомендациях Ксайлинкса ничего не увидел про что что на малых расстояниях можно пренебречь разбегом длин

А для чего?

Автор: Aner Apr 23 2018, 09:20

Да что то много, что то не оч вписывается. Длины "большие" против одного "красного". Вы учли длину проводников внутри чипа? В топе мало. Я бы больше трамбонов ставил в таком случае чем гармошек.

на 0402 однозначно!

Автор: ClayMan Apr 23 2018, 09:34

Да, адреса выглядят как-то избыточно длинно. Шаг контроллера похож на 1мм - если так, то теоретически можно протащить две трассы по 100мкм между переходными 0.2х0.5мм в местах, где совсем уж никак по-другому (но на практике зависит от параметров вашей платы конечно). Сейчас из-за пары сигналов группы addr+ctrl, которые не пролезли, пришлось такой огород городить. Терминаторы по идее можно поближе к памяти поставить, зачем увеличивать длину их подключения? Клиренсы между сигналами большие - это хорошо конечно, но как-то уж очень много места съедено. Ну и если уж адреса разбросали между внешними и внутренними слоями (что тоже нежелательно), то при выравнивании обязательно нужно учитывать задержку, а не голую длину - в итоге трассы на внешнем слое физически окажутся длиннее.

Автор: Aner Apr 23 2018, 09:42

Верно подмечено. Если трасса на верху то E~1, если вниутри то E~4 +\- (см точный у материала FR-4 на нужной частоте). То длина внутренней трассы может сократиться вдвое. Ну и в Si9000 проверить можно.

Автор: Uree Apr 23 2018, 09:59

Шутите? Трасса в воздухе зависла или все-таки на плате лежит, да еще и маской прикрыта?

Разница в задержках чуть больше 10% так что никакой 2-кратной разницы в длине не будет.

Автор: Шухарт Apr 23 2018, 10:17

С терминаторами учту..

А чем чревата "размашистость" трассировки DDR3? Место на плате есть. В этих внутренних слоях я мало буду сигналов вести.

Uree, а можно ваше мнение услышать?

И никто не ответил на вопрос. И сразу вопрос, какой длины надо делать дифпару CK? Сейчас она около 55мм.

У ксайлинкса написано -CK and DQS trace lengths must be matched (±250 mil) to maximize setup and hold

margins. То есть мне её по хорошему надо сократить до 32мм. С другой стороны где-то читал что клок должен быть равен или даже длинее адресов.-

Автор: Uree Apr 23 2018, 11:01

А что Вы хотите услышать? Есть место - пусть себе лежат трассы, что тут еще советовать![]() Зазоры между ними есть, зазоры к остальным сигналам есть - и хорошо.

Зазоры между ними есть, зазоры к остальным сигналам есть - и хорошо.

А что Вас смущает с клоком? Если группа клок-адреса-управления выравнена, то требования соблюдены. Со стробами выравнять клок в общем случае практически нереально, но тут write-leveling помогает, поэтому не знаю откуда и к чему требование о "must be matched (±250 mil)".

Автор: Шухарт Apr 23 2018, 11:28

Чисто из объективности хотел вас услышать. Как я понял у вас в трассировке ДДР большой опыт. Ну и вдруг я чего-то не вижу и допустил какую-то грубую ошибку)

Значит надо набрать ещё длины у клоков до 60мм, чтобы дифпара была равна адресам?

Автор: Uree Apr 23 2018, 11:44

Вы думаете это можно определить "на глаз" по скриншотам?

То же самое - по скринам не определить, что конкретно у Вас сделано, а что нет. Но клоки с адресами как правило собирают в одну группу, а требования к ее выравниванию зависят и знаете их Вы, не я

Автор: EvilWrecker Apr 23 2018, 12:35

Безусловно очень занятно наблюдать такую возню вокруг одной планки на шестой спартан, особенно на наличие терминации(и как она сделана), выравнивании ресета, трасс в 60мм и пр. и то как ТС пересчитывает милы в мм ![]() Но особо хочется спросить за терминацию- а как вы выбирали типоразмер? Все что написано про задержки во корпусе, время распространения снаружи/внутри платы все мимо- никаких 2х разницы там не выйдет никогда, а оглядываясь на скорости спартана никаких таймингов не надо прикидывать, достаточно физической длины.

Но особо хочется спросить за терминацию- а как вы выбирали типоразмер? Все что написано про задержки во корпусе, время распространения снаружи/внутри платы все мимо- никаких 2х разницы там не выйдет никогда, а оглядываясь на скорости спартана никаких таймингов не надо прикидывать, достаточно физической длины.

В вашем дизайне спартан встает прекрасно байтлейнами на внешних слоях и частью адресов/команд там же, трассами гораздо короче 60мм(до 2х), без терминирования, без большого количество банок в питании, без пересчета TOF и пр.

Автор: ClayMan Apr 23 2018, 12:47

человек же попросил критики и тп - вот ему и набросали)) это скорее из общих рекоммендаций к улучшению дизайна.

да, 2-х кратной не будет конечно - это уже явный перегиб, Uree верно расписал.

Автор: Шухарт Apr 23 2018, 14:22

Не очень понял, что я не так пересчитываю?

Вы про это: "У ксайлинкса написано -CK and DQS trace lengths must be matched (±250 mil) to maximize setup and hold

margins. То есть мне её по хорошему надо сократить до 32мм" Длина DQS у меня на плате- 32мм, поэтому я и хотел сравнять с ней CK.

Но особо хочется спросить за терминацию- а как вы выбирали типоразмер?

Терминация есть на референсной схеме, поэтому и была сделана.

С корпусами кондеров и резисторов я понял. А что ещё не так?

И что с ресетом?

Автор: EvilWrecker Apr 23 2018, 15:23

250 милсов это 6.35мм- откуда взялось это:

?

Далее:

И что с того?

Не считая подчеркнуто кривого свапа(если он вообще тут есть), в принципе вы допускаете 2 типичных ошибки новичка:

- делаете фанауты короткими догбонами "сразу и прямо" из под микрульки памяти, хотя спокойно можете их разворачивать и даже выносить подальше для пущего удобства и выигрывать место.

- выравниваете большую величину аккордеоном, т.е. наименее эффективным паттерном для большого набега длины

Уносить за километр терминацию, коль решили ее ставить, нет смысла. Лишние банки уберите, поставьте 0402, фанаты сделайте к ним зеркально по длинной стороне(противоположно тому как у вас сейчас), 0603 пару можете оставить на бОльшую емкость.

Ресет не нужно выравнивать

Ну и повторю вопрос- зачем вы сюда закладываете пассив больше чем 0402? Справедливости ради нужно отметить что сама по себе разводка именно меандров у вас вполне себе, не считая крайнего левого проводника на боттоме

Автор: Шухарт Apr 23 2018, 16:10

Спасибо за конструктив)

-В руководстве есть фраза- CK and DQS trace lengths must be matched (±250 mil).... Я её понимаю так- СК и DQS должны иметь одинаковую длину с погрешностью 250мил(6.5мм). Учитывая что длина байтов у меня 32мм то и DQS у меня 32мм, и поэтому я и клок хотел уменьшать с 50 до 32мм

-Раз терминация в образце есть и на нём всё работает, то и я её решил оставить. Как по мне лучше предусмотреть место и если что, потом не запаивать.

Касательно того, что корпуса резисторов большие я уже понял и признал, каюсь. Просто как правило применяю 0603, и тут думал что нет необходимости мельчить. (Плюс читал статью на хабре что идентичный по номиналу и вольтажу кондер по характеристикам лучше в большем корпусе)

Поставлю тогда кондёры 0402 и резисторные сборки и придвину их поближе к памяти

- делаете фанауты короткими догбонами "сразу и прямо" из под микрульки памяти, хотя спокойно можете их разворачивать и даже выносить подальше для пущего удобства и выигрывать место.

- выравниваете большую величину аккордеоном, т.е. наименее эффективным паттерном для большого набега длины

Уносить за километр терминацию, коль решили ее ставить, нет смысла. Лишние банки уберите, поставьте 0402, фанаты сделайте к ним зеркально по длинной стороне(противоположно тому как у вас сейчас), 0603 пару можете оставить на бОльшую емкость.

Ресет не нужно выравнивать

Ну и повторю вопрос- зачем вы сюда закладываете пассив больше чем 0402? Справедливости ради нужно отметить что сама по себе разводка именно меандров у вас вполне себе, не считая крайнего левого проводника на боттоме

-Биты я свапировал. И вроде раскрестил всё что мог. Или и адреса можно свапировать??)) В чём кривизна свапа?

>>Лишние банки уберите, поставьте 0402, фанаты сделайте к ним зеркально по длинной стороне(противоположно тому как у вас сейчас)

-Поясните пожалуйста эту фразу.

>>Ресет не нужно выравнивать

>>не считая крайнего левого проводника на боттоме

По совпадению это как раз RST# ))

Автор: Uree Apr 23 2018, 16:35

На входах адресов встроенной терминации нет, поэтому как минимум не мешает проверить, как будет выглядеть сигнал. Пару часов назад посмотрел - неприятно удивился... без терминации выглядит отвратительно. Но это с моделями, которые были под рукой, целевые могут и по другому себя вести.

Автор: EvilWrecker Apr 23 2018, 16:35

Перечитайте пост №44 и сравните еще раз с тем что пишут хилые.

Нет, безусловно внешней терминацией хуже не сделать

Это где вы такое прочитали? Что насчет вашего дизайна- на картинке хорошо видно что у вас уже заложены 0402 под спартаном, о чем разговор?

В чем смысл свапа- раскидать трассы настолько прямо чтобы разбег длин до таргета был минимальный. У вас же дичайшая накрутка, что намекает о кривизне сапа: трассы идут неоптимально. В контексте вашего вопроса про клок это вполне актуальный момент- решаете проблему которую сами себе и создали

У вас сделано как на картинке слева, имеет смысл делать как справа

http://electronix.ru/redirect.php?https://postimages.org/

Так в том и дело что все зависит от того на какой частоте работает память и какой длины вышли траски- для таких медленных скоростей как раз и нет проблем сделать так чтобы не было нужды во внешней терминации. Здесь в качестве попсового примера можно привести тот же BeagleBone Black.

Автор: Шухарт Apr 23 2018, 17:26

Нет, безусловно внешней терминацией хуже не сделать

Это где вы такое прочитали? Что насчет вашего дизайна- на картинке хорошо видно что у вас уже заложены 0402 под спартаном, о чем разговор?

В чем смысл свапа- раскидать трассы настолько прямо чтобы разбег длин до таргета был минимальный. У вас же дичайшая накрутка, что намекает о кривизне сапа: трассы идут неоптимально. В контексте вашего вопроса про клок это вполне актуальный момент- решаете проблему которую сами себе и создали

У вас сделано как на картинке слева, имеет смысл делать как справа

http://electronix.ru/redirect.php?https://postimages.org/

Так в том и дело что все зависит от того на какой частоте работает память и какой длины вышли траски- для таких медленных скоростей как раз и нет проблем сделать так чтобы не было нужды во внешней терминации. Здесь в качестве попсового примера можно привести тот же BeagleBone Black.

-В посте 44 я отвечал Юрию, который писал что клоки как правило равны адресам. А адреса у меня 60мм, поэтому я спросил- наращивать до адресов-60мм или срезать до DQS -32мм.

К слову, я так и не понял какой длины сделать клок. Или "спартан всё схвает"?))

-Статья о кондёрах - http://electronix.ru/redirect.php?https://geektimes.ru/post/263366/

- Под спартаном пришлось ставить 0402, тк 0603 что-то не влезали совсем)

А в чём смысл изменения подключения кондёров? Уменьшение индуктивности?

Автор: EvilWrecker Apr 23 2018, 17:42

К слову, я так и не понял какой длины сделать клок. Или "спартан всё схвает"?))

Капитан очевидность намекает что нужно сделать как предлагают хилые, и попасть по длине CK vs DQS в промежуток 250милсов.

- Под спартаном пришлось ставить 0402, тк 0603 что-то не влезали совсем)

Вот оно что- ну тогда не мелочитесь, ставьте 1210 в ддр3, чтобы было прямо за-сь

Именно.

Автор: Uree Apr 23 2018, 18:33

По поводу конденсаторов да, есть такой неприятный эффект. Но наиболее критично его проявление на выходах источников, хоть DCDC, хоть LDO(хотя для первого, конечно, важнее набрать нужную емкость). Но в случае декаплинга важнее малые размеры, чем определенная емкость. Так что даже не сомневайтесь - при прочих равных ставьте как можно меньшие корпуса.

Автор: yuri.job Apr 24 2018, 06:06

хотел я картинку вставить по поводу спартана и ддр3, да куда то дел ее, не нашел. в общем, работало, лично видел на столе, с выравниванием меандром с зазорами 1w, так что на самом деле, делать зазоры меандра как у вас, оно конечно правильно, но не нужно. это несколько уплотнит дизайн. еще как то странно конденсаторы ддр3 стоят, мне глез режет, это имхо, я привых ставить суммарно 6шт вдол длинной стороны, соосно чипу. у микрона на эту тему аппликуха есть. и не забывайте, что спартан6, если мне память не изменяет, максимум что умеет, это всего ддр3-800, т.е.400МГц, а это частота, которая может прощать очень многое. В целом все ок, но просто необычно.

Автор: Aner Apr 24 2018, 06:55

Для LVDS 1W не пройдет, нужно как минимум 2.5W, по правилам 3W. Для не LVDS на коротких трассах при большой плтности можно 1W.

ДА ддр3-800, т.е.400МГц, но не нужно забывать про скрорость нарастания фронтов, где требования до 5 и 7 гармоники от ваших 400 доходят.

На тех шинах 400Мгц не максимальная частота, если спектр посмотрите.

Автор: EvilWrecker Apr 24 2018, 07:16

Наиболее правильно отделять не в единицах ширины трассы, а в расстоянии до следующего опорного слоя, т.е. H- итого "безопасность" начинается с 3H, но для спартана можно и 2H спокойно на таких дистанциях. Меньше уже не стоит ![]()

Автор: Uree Apr 24 2018, 07:31

Не имеет значения в чем считать, в ширине или высоте. Они связаны одним и тем же коэффициентом, для внешнего слоя, например, 1.8 (для внутреннего не считал, но тоже какая-то константа). Т.е. для одного и того же импеданса W/H=1.8. Просто в единицах Н получается допустимо меньшее расстояние между трассами, чем в единицах W. В те самые 1.8 раза меньше. И во столько же раз больше места на трассировку![]()

Автор: EvilWrecker Apr 24 2018, 07:40

Да ничего подобного- в расчете кростолка наибольший вклад дает в т.ч. rise time и расстояние до опоры. Разделение же по ширине трасс это rule of thumb из дремучих времен.

Вы помнится упоминали что с приборами интела работаете- посмотрите у них бумаги, там хорошее объяснение присутствует. А вот насчет коэффициента хотелось бы подробнее послушать.

Автор: Шухарт Apr 24 2018, 07:59

Спасибо

После замены с 0603 на 0402 это действительно напрашивается)

Автор: Uree Apr 24 2018, 11:43

Вы помнится упоминали что с приборами интела работаете- посмотрите у них бумаги, там хорошее объяснение присутствует. А вот насчет коэффициента хотелось бы подробнее послушать.

Все так, и с расстоянием до опоры тоже. Просто меняя это расстояние придется менять и ширину трассы, чтобы сохранить нужный импеданс - чем выше до опоры, тем шире трасса. Вот об их соотношении я и написал, но ошибся. Зависимость есть, но оно зависит от многих факторов, и с изменением высоты до опоры ширина меняется, но не совсем линейно и конечно не с соотношением 1:1.8, как написал выше(это был частный случай). Так что комментарий снят, был не прав.

Автор: ClayMan Apr 24 2018, 14:01

Плюсую. Раз уж зашел разговор

Кроме того:

Так что в рассматриваемой конфигурации, когда вся трассировка по сути выполнена на внутренних слоях, для минимальных зазоров вполне можно использовать правило 2W. Но если место позволяет, то можно и больше конечно.

Автор: EvilWrecker Apr 24 2018, 14:43

Если я хорошо помню ту бумажку(примерно такой http://electronix.ru/redirect.php?http://www.edn.com/Pdf/ViewPdf?contentItemId=4417648) там даже есть рисунки на которых видно как при разделении трасс на величины ширины дорог ожидаемо снижается расстояние до опоры. Но вообще разговор вроде шел за то чтобы адекватно использовать внешние слои, т.е. делать микрострипы которые как раз подвержены FEXT. Если я что пропустил то безусловно приношу извинения

Ну, с этим никто не спорит

Я почему упомянул про дремучесть правила в разделении по ширинам трассы: немало "гайдов" применяют это дело к микрострипам. А там как раз надо на расстояние до опоры смотреть.

Ну и интол не зря упомянут- даже в открытом доступе есть вполне годные http://electronix.ru/redirect.php?http://web.cecs.pdx.edu/~muilenta/psev/lecture_10.pdf, в закрытом еще больше.

Автор: ClayMan Apr 25 2018, 10:18

Открыл посмотреть, в самом начале встретил вот такую фразу "In high-speed serial links operating above 10 Gbps, losses are the dominant factor influencing

interconnect design. No matter how low the loss in the dielectric, conductor loss dominates the attenuation". Либо я чего-то не понял, либо тут автор что-то напутал, т.к. в его же книге (и не только в ней) вполне справедливо утверждается обратное и даже есть такой график

http://electronix.ru/redirect.php?https://postimages.org/

Автор: EvilWrecker Apr 25 2018, 10:51

Тут видимо имеется некоторый language barrier, давайте по порядку:

- в 10+G скоростях колхозный фр4 не кладут(нормальные люди), а кладут вестимо материалы с низкими потерями. В тоже самое время, потери есть- например от шероховатости фольги, или в дизайне пара с сильной связью в которой распределение токов идет к тонким краям между плечами, а не по "широкой" стороне. Где-то апликуха была, вспомню- приложу: наглядные картинки присутствовали.

- Богатин подчеркивает в начале предложения

т.е. говоря проще, проблему с потерями в диэлектрике в описываемом примере уже зарешали и к ней в данном случае не возваращаются, т.к. они незначительны на фоне остального.

- в тоже самое время в другом примере с другой задачей который вы привели, где как раз сигнал гоняется по фр4 он собственно и показывает, что как бы кто не изошрялся а проблемы с потерями в диэлектрике на тех частотах не зарулить никак, нужна замена на high-performance materials.

Достаточно грубое объяснение, но думаю понятно что противоречий нет.

Автор: ClayMan Apr 25 2018, 11:23

Да, похоже это и имелось ввиду

Автор: EvilWrecker Apr 25 2018, 12:03

Именно- противоречие было бы если он написал в начале того предложения вместо

вот это

в контексте оглядки на не диэлектрические потери. А так просто разные примеры, из разных миров

Автор: EvilWrecker Apr 25 2018, 23:21

http://electronix.ru/redirect.php?https://postimages.org/

Автор: Шухарт Apr 27 2018, 10:24

Добрый день. Ещё возник вопрос.

Я когда оттрасировал все адреса, не предусмотрел место под переходные для кондёров на землю и питание. А потом ещё вдобавок уменьшил кондёры и резисторы ии сдивнул ближе к ДДР. (см приложение 1)

Теперь при всем желании переходным напрямую я не могу их соединить. Если я сделаю вот такие полигоны в слое BOT (см приложение 2) чтобы подключить землю и питание, это как-то ухудшит работу памяти?

Автор: Uree Apr 27 2018, 10:36

Сам полигон VTT может таким быть, а вот отсутствие переходных на землю близко к конденсаторам VTT... можно сказать, что этих конденсаторов там практически нет.

На работе шины это скажется, конечно, но не фатально.

Автор: EvilWrecker May 3 2018, 16:40

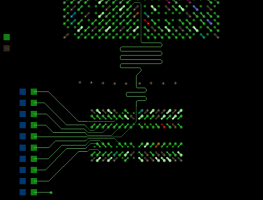

Некоторое время назад я добровольно вызвался показать пример на основе проекта тс- в контексте выравнивания не аккордеонами, с условием выкладывания в эту тему результата. В связи с этим представляю результаты на суд общественности, но перед этим несколько важных моментов:

- оглядываясь на ведение проекта(мне достался именно кусок со спартаном и ддр3 в формате аллегро), есть подозрение что не был настроен свапинг как таковой в самом сапр, т.е. процесс идет перестановкой нетлейблов. Могу ошибаться, но ни свап ни правила у меня в 17.2 не заработали ![]() .

.

- помимо этого, в оригинальном проекте используются сильно зарезанные пады у бга, например для ддр3 пады стоят 0.3мм.

- есть ряд сомнений касаемо расчетов импеданса и пр, т.к. в проекте используется FR4 c Dk=4.

В связи с этим в моем крайне скромном примере(больше пиво пил чем старался ![]() ) соблюдены следующие условия:

) соблюдены следующие условия:

- заимпортировал все в альтиум, т.к. под рукой был и он и библиотеки компонентов

- геометрия трасс взята с оригинального проекта, включая трассы толщиной 0.15мм

- зазор взят по расстоянию между фанаутами от внешних слоев(видно на скриншотах), т.е. более 2х толщин.

- фанауты специально не объединялись и не оттягивались от корпуса

- чтобы равномерно «нарастить мясо» было взято практически то же самое расстояние как и в оригинале, разница буквально пара мм. Для большей разницы в матчгруппе сделан сдвиг планки вбок.

- заложены «острова» под конденсаторы на боттоме со стороны байтлейнов

- пады ддр3 сделаны 0.43мм

- точность выравнивания взята сильно больше чем надо(все подведено под 25мм ровно)

- использовались только trombone, switchback, back-jog и bump. Аккордеоны а с ними и альтиумовский interactive length tuning не использовались, т.е. выравнивание «нарисовано».

Что имел намерение показать на этом примере(в основном сугубо для ТС):

- возможность развести все тромбонами и свичбэками

- возможность развести байтлейны на внешних слоях

- возможность сделать выравнивание существенно компактнее, в частности без заездов в зону адресом и управления

Думаю что хорошо заметно, что выравнивание легко переживет сдвиг вниз ддр3, т.к. основные наросты вертикальные. Поскольку под адреса есть 4 пустых слоя на разводку, отдельно обсуждать их не вижу смысла ![]() .

.

http://electronix.ru/redirect.php?https://postimages.org/

http://electronix.ru/redirect.php?https://postimg.cc/image/uc52pbuqf/

http://electronix.ru/redirect.php?https://postimg.cc/image/4tcqcd8mf/

Автор: Шухарт May 4 2018, 08:19

EvilWrecker, спасибо за наглядный пример по тромбонам.

Так и есть

Это всё обсуждалось со специалистом, который монтирует бга в ИК печке, он рекомендовал пользоваться формулой 2/3*Dшара. Чем это чревато?

Я писал технологам PCBtech, мне выслали табличку с толщинами ядер, препрегов и их Dk, но заверили что всё это ориентировочно и актуально только для конкретного завода. И сколько там ядер и препрегов и каких именно положат китайцы только им известно. Поэтому да, я взял среднюю Dk=4. Если взять Dk=4.2 например, то импеданс изменится для внутреннего слоя на целых 3 Ома, это если считать в Polar. А если вбить все те же параметры в Сатурн, то он выдаст импеданс +-4 Ома от того что вышло в Polar.

- геометрия трасс взята с оригинального проекта, включая трассы толщиной 0.15мм

В Top/Bottom у меня 0.15, а на внутренних -0.11мм

Это всё хорошо, но разговор был изначально про то, что мои адреса можно сократить в два раза:

А вы сократили байты с 32мм, до 25мм. При том что придвинули DDR ближе к Спартану

Автор: EvilWrecker May 4 2018, 08:38

Ну это вы зря- не лень каждый раз заново нетлист подгружать?

Не знаю что это за специалист такой и что у него за формулы, но в случае со скриншота считалось по IPC- при этмо вышло даже чуть больше чем у самого микрона(у него 0.42мм). Самый минимум который использовал в своих дизайнах это 0.4мм- что касается рисков, то они такие же как и в любом другом случае непомерного вырезания падов.

Ну так в приложенном примере и сделано на топе и боттоме- а если бы еще маски лежали удачнее в самом спартане, то и оба можно было бы воткнуть на топе.

Разумеется- и для того чтобы это сделать нужно выделить под них место: в частности сделать так чтобы байтлейны не "раздувало" и они не подпирали бы адреса с командами. У вас таргет на них идет на расстояние половины планки сбоку от ддр3, хотя все должно практически полностью умещаться между ней и спартаном. В случае приведенного примера как раз освобождено полностью все то место которое вы потратили на выравнивание, еще и остается на внешних слоях.

Автор: Шухарт May 4 2018, 11:49

На тот момент не разобрался как потом передавать изменения назад в схему.

Да, не заметил что это топ

Спасибо

Автор: EvilWrecker May 7 2018, 12:24

Еще небольшое дополнение выскажу касаемо тромбонов(а тем более с свичбэков)- как таковое их использование это один из вернейших признаков плотности и сложности дизайна. Очевидно что он больше всего нужен там, где места нет- т.к. такие же длины в той же площади аккордеонами не накрутить: при всем при этом надо понимать, что если в таком то дизайне удалось все заровнять аккордеонами, то с вероятностью близкой к 90% это возьмет автомат(в случае топ сапр). Более того, результат можно достаточно сильно оптимизировать в сторону уменьшения пустых островов, методология очень проста: выравнивание окружается boundary(например любой медный объект, хоть no net trace), далее соответственно они поджимаются в нужных участках и запускается новый проход автомата. Через несколько итераций можно получить результат который далеко не все т.н. синьоры смогут положить. В случае использования дуг все разумеется гораздо сложнее(а чаще и невыполнимо), но вот что касается тромбона и свичбэка то оглядываясь на приведенные ранее скриншоты автоматы так вообще не кладут. Есть и обратная сторона такого выравнивания(тромбонами)- в озвученных условиях это наиболее сложный и рискованный паттерн, в том смысле что очень велика вероятность положить не так таргет с соседями и заблокировать все свободное место. Если скажем делается дизайн аля HPC карточка на плис под PCIe слот и на ней скажем 4 ранка ддр4 уложенные memory down(притом честным флайбаем, без халявы типа кламшелов) то вероятность облажаться с таким выравниванием возрастает на несколько порядков.

Так очень легко оценить уровень дизайнов вообще- если например на плате нету courtyard-to-courtyard плэйсмента, или есть пустые острова от выравнивания, или все сделано аккордеонами то это вообще ни разу не плотный дизайн, сколько бы там ни было слоев и компонентов. Исключением можно назвать разве что некоторые супер оптимизированные корпуса(не надо много крутить выравнивание) а также дизайны типа 80+ слоев и 30к+ компонентов, там конечно уже другая история ![]()

Автор: maple May 10 2018, 09:14

Можете пояснить, за счет чего тромбоны экономичнее аккордеонов? Только за счет срезов (или дуг) на верхушках меандров? Есть еще вариант выигрыша площади в случае одновиткового тромбона с выходом с той же стороны, что и вход, но это редкий частный случай.

Автор: EvilWrecker May 10 2018, 12:18

Сугубо вопрос геометрии, т.к. существенно длиннее сама траектория выравнивания- даже небольшой загиб уже наращивает много длины. Есть хорошие http://electronix.ru/redirect.php?https://www.keysight.com/upload/cmc_upload/All/1AgiAdvanced.pdf, там(22стр) достаточно неплохо видно разницу.

Нет, тут именно фишка в том что проводник как бы повторяет сам себя, "по длинной стороне"- а в показанном примере просто удобнее было сделать дугами.

Не могли бы вы пояснить что имеется в виду?

Автор: EvilWrecker May 11 2018, 12:16

Все также плохой свапинг со стороны байтлейнов(+ также на внутренних слоях) и все такая же кривая раскидка адресов- зачем делать такой таргет?

http://electronix.ru/redirect.php?https://postimages.org/

В принципе, вы можете подзабить и дотянуть до нужного соотношение байтлейны а не адреса, раз такие проблемы именно с их таргетом- но тут все равно шило на мыло ![]()

Автор: Шухарт May 14 2018, 06:51

Не очень понял, на что подзабить?

Автор: EvilWrecker May 14 2018, 12:51

У вас есть целевое соотношение длин от хилых- и поскольку место на адреса/команды вы используете максимально неэффективно, дотягивать до соотношения здесь проще длину байтлейнов. Хотя при таком свапинге и это может быть проблемой

Автор: Шухарт May 14 2018, 14:04

Смог сократить адреса до 38мм, байты остались 25мм.

Что-то не вижу в Spartan-6 FPGA Memory Controller User Guide прямого указания на соотношение байтов и адресов.

Есть два требования:

margins.

• There must be a maximum ±50 ps electrical delay (±300 mil) between any

address/control signals and the associated CK and CK_N differential clock FPGA

output.

Автор: EvilWrecker May 14 2018, 14:13

Капитан очевидность заявляет следующее- по следу бумажки хилых:

- строб находится в матчгруппе в месте с маской и битами

- строб укладывается в соотношение к клоку

- клок связан соотношением с адресами/командами

Т.е в итоге у вас байтлейны имеют косвенную связь с адресами и командами ![]()

Автор: Шухарт May 14 2018, 14:45

- строб находится в матчгруппе в месте с маской и битами

- строб укладывается в соотношение к клоку

- клок связан соотношением с адресами/командами

Т.е в итоге у вас байтлейны имеют косвенную связь с адресами и командами

Получается что с натяжкой я выполняю требования, если клок сделаю 31мм. (При адресах 38 и байтах-25мм)

CK and DQS trace lengths must be matched (±250 mil) to maximize setup and hold margins.

-Исходя из этого требования клок должен быть в интервале (18,65;31,25)

There must be a maximum ±50 ps electrical delay (±300 mil) between anyaddress/control signals and the associated CK and CK_N differential clock FPGAoutput.

-Исходя из этого требования клок должен быть в интервале (30,38;45,62)

Автор: EvilWrecker May 14 2018, 14:50

Вы подождите с вычислениями, а лучше скажите какая у вас актуальная длина клока и обоих стробов?

Автор: Uree May 14 2018, 17:05

Я не очень понимаю откуда берется такая рекомендация, но в общем случае, при числе чипов на шине большем чем один, оно не выполняется в принципе.

Точнее при 2-х чипах еще как-то можно попытаться его выполнить, но это будет весьма непросто, а при 4-х совсем невозможно.

Автор: EvilWrecker May 14 2018, 17:10

Так у спартана 6 далеко не самый могучий контроллер памяти, а что касается именно количества планок vs возможности выдержать эти констрейны, то тут вы конечно правы: в связи с этим на одной 16 битной шине там и сидит сугубо одна 16 битная планка.

Автор: Шухарт May 16 2018, 06:08

LDQS=25.5мм

UDQS=25.3мм

CK сейчас равен 35.1мм

Автор: EvilWrecker May 16 2018, 08:45

UDQS=25.3мм

CK сейчас равен 35.1мм

Понятно- тогда сказанное про нарост байтлейнов(а не адресов) в силе. По вашей картинке судя по всему проще слегка притянуть именно байтлейны.

Автор: Шухарт May 16 2018, 08:57

А мне не очень, зачем их наращивать, если я могу просто сократить клок до 31мм? Тогда требования выполнятся

Автор: EvilWrecker May 16 2018, 09:06

Клок находится в соотношении с командами и адресами, соответственно меняя клок изменятся и они- оглядываясь на то какой у вас там таргет, задача подгонки клока выглядит более трудоемкой чем подгонка байтлейнов. Но если вам проще зарулить именно клок, то нет проблем- возражения с моей стороны невозможны

Автор: Шухарт May 16 2018, 13:43

в этом соотношении?

Автор: EvilWrecker May 16 2018, 14:06

Да, оно самое

Автор: Шухарт May 18 2018, 12:21

А насколько оно жёсткое?

Просто в тех же рекомендациях на Спартан написано:

А вы байты на внешних слоях провели

Автор: EvilWrecker May 18 2018, 17:00

Ну, оглядываясь на число то наверное не очень жесткое, благо 300 мил это не 30

Что из себя представляют рекомендации хилых- там время от времени проскальзывает фраза о том, что они составлены для типа 100% предсказуемо успешного результата в случае их выполнения, т.е. с серьезным запасом. Хорошим примером является требование по количеству конденсаторов в питании для такого-то корпуса, которое по факту завышено в несколько раз. Что касается внешних слоев, то разводить внутри конечно "безопаснее", но если делать правильно на внешних то никакого криминала нет и не может быть: на топе и боттоме разводят гораздо более высокоскоростную память без каких-либо проблем.

Касаемо именно вашего случая: на моей памяти есть люди которые успешно и не очень играли с timing margin в спартане, однако поскольку это ваш явно первый дизайн с ддр3 то лезть в эту тему пока что не рекомендую, тем более что озвученные в бумаге цифры легко реализуемы.

Автор: Шухарт May 20 2018, 20:08

Что из себя представляют рекомендации хилых- там время от времени проскальзывает фраза о том, что они составлены для типа 100% предсказуемо успешного результата в случае их выполнения, т.е. с серьезным запасом. Хорошим примером является требование по количеству конденсаторов в питании для такого-то корпуса, которое по факту завышено в несколько раз. Что касается внешних слоев, то разводить внутри конечно "безопаснее", но если делать правильно на внешних то никакого криминала нет и не может быть: на топе и боттоме разводят гораздо более высокоскоростную память без каких-либо проблем.

Касаемо именно вашего случая: на моей памяти есть люди которые успешно и не очень играли с timing margin в спартане, однако поскольку это ваш явно первый дизайн с ддр3 то лезть в эту тему пока что не рекомендую, тем более что озвученные в бумаге цифры легко реализуемы.

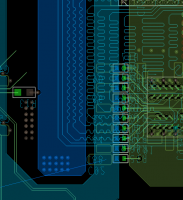

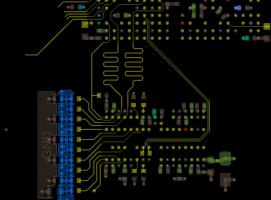

В итоге получилось что байты около 25мм, Адреса-35мм, а клок 31мм. В интервал уложился. Просто было интересно, не зря ли заморачивался.

Автор: EvilWrecker May 20 2018, 20:20

Если стробы в обоих байтах 25мм то да, уложились практически впритык

А есть картинки?

Автор: Шухарт May 21 2018, 06:56

А есть картинки?

Вот.

(Кстати, у второй памяти смог адреса с клоком сделать 31мм, а байты -25)

Автор: EvilWrecker May 21 2018, 09:27

Мне вот интересно стало- вы приводите круглые числа, в ноль что ли выравниваете? Точно нету никакого tolerance?

Некоторый прогресс в геометрии есть, хотя конечно суть та же самая- но главное что в числа уложились

Автор: Шухарт May 21 2018, 10:33

Вот, если интересно.

CK+ и CK- я друг с другом ещё не равнял. Они у меня сейчас в группу к адресам закинуты

Автор: EvilWrecker May 21 2018, 11:13

Насколько можно понять в соотношения от хилых вы уложись, включая строб к клоку.

Автор: vladec May 22 2018, 06:09

To Шухарт

При выравнивании Вы учитываете задержку сигналов внутри корпуса микросхемы ПЛИС для разных выводов? Там у Xilinx в некоторых корпусах бывает большой разброс.

Автор: Шухарт May 24 2018, 12:02

При выравнивании Вы учитываете задержку сигналов внутри корпуса микросхемы ПЛИС для разных выводов? Там у Xilinx в некоторых корпусах бывает большой разброс.

Добрый день. Нет, не учитывал. А вы не подскажете, где с ними можно ознакомиться? в UG385 (Spartan-6 FPGA Packaging and Pinouts) ничего подобного не нашёл.

Автор: Corvus May 24 2018, 13:16

ЕМНИП, по Spartan-6 такой инфы нет. Да и не нужна она там, не те скорости и длины.

Русская версия Invision Power Board (http://www.invisionboard.com)

© Invision Power Services (http://www.invisionpower.com)