| |

|

|

DDR3: Терминация сигналов CK DDR3: Терминация сигналов CK, Выбор топологии |

|

|

|

|

May 31 2018, 04:03 May 31 2018, 04:03

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Сейчас проблема именно в модели и именно с сигналом СК:

1. Фронты спада длиннее фронтов нарастания.

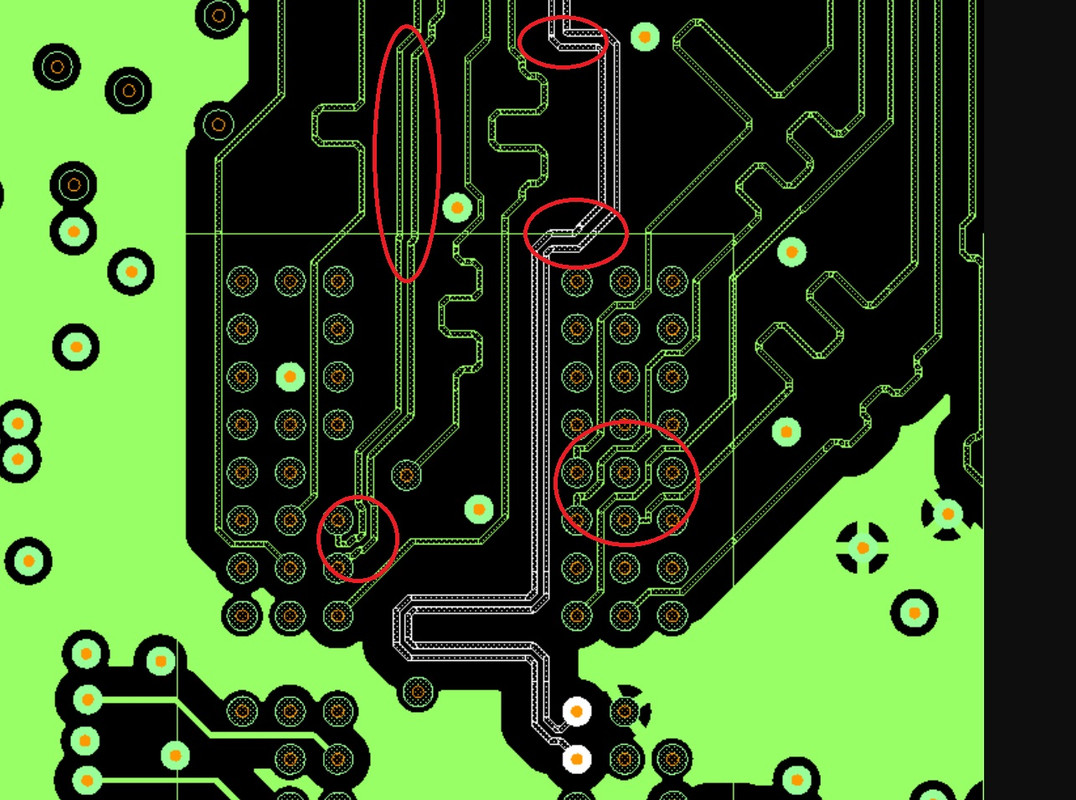

2. Изменение схемы терминации цепи СК дало положительный, но недостаточный эффект . Есть конечно немало вопросов с оглядкой на эту тему, где есть уже ряд ваших рассуждения касаемо разводки и наличия моделей к артиксу, но это пока/уже оставим. Тут все гораздо проще чем кажется- нужно просто начать проектировать и разводить не через задницу, а хотя бы нормально  Цитата Предлагаю закрыть вопрос термобарьеров, т. к. их исключение не поможет решить исходную проблему с цепью СК. Вы можете сколько угодно фантазировать на тему отсутствия влияния термалов в виа в хайспидных дизайнах, но на всякий случай напоминаю что у вас прежде всего кривая, ущербная разводка сигналов.  Опять же, насколько можно понять вы не удаляете неиспользуемые пады, стало быть проблема многократного antipad void crossing имеет место быть- это хорошо видно по вашим картинкам. Ну и учитывая кучу изломов, прямых углов, накрутку в антипадах, разный зазор между плечами диффпар при одинаковой их ширине и сильной связи в самой паре и еще кое-чего до кучи как минимум ясно две вещи: - вы "моделируете" что угодно, кроме своего дизайна, т.к. у вас при таких вводных вообще ни разу не uniform transmission line, сетап неверный. - вы упорно игнорируете целостность сигнала в рамках одного набора как такового. Поэтому обсуждать тут особенно нечего потому как в самом худшем и неочевидном случае представляется логичным сперва отлечивать все найденные проблемы какие есть в дизайне, пусть вам и ошибочно кажется что они якобы не относятся к "генеральной линии". Говоря проще, вы кладете болт на свой дизайн а потом втаптываете его в землю

|

|

|

|

|

|

|

|

May 31 2018, 07:54 May 31 2018, 07:54

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

QUOTE (Stepanich @ May 31 2018, 00:46)  Aner, спасибо за ответ. Мы обязательно поставим на место всех уборщиц и монтажников. Вы же не будете возражать, что наличие термобарьеров никак не сказывается на асимметрии сигнала СК? Ну хотя бы в модели?

Сейчас проблема именно в модели и именно с сигналом СК:

1. Фронты спада длиннее фронтов нарастания.

2. Изменение схемы терминации цепи СК дало положительный, но недостаточный эффект. Промоделируйте в гиперлинксе наличие термобарьеров увидите как скажется на асимметрии сигнала СК. Ну вашим монтажникам под маской эти термобарьеры ничего не дадут. То что термобарьер навредит это точно. Как рассуждаю с точки зрения спектрального анализа на разные скорости нарастания, спада ваших фронтов. У вас в спектре появляются чётные N-ные гармоники. Их происхождение от неравномерного волнового по диф паре, ее перегибам, окружению, переходам, земляным переходникам по ходу трассы. Все можно исправить, гиперлинкс покажет.

|

|

|

|

|

|

|

|

May 31 2018, 10:45 May 31 2018, 10:45

|

Знающий

Группа: Свой

Сообщений: 825

Регистрация: 28-11-07

Из: г.Винница, Украина

Пользователь №: 32 762

|

Цитата(Stepanich @ May 30 2018, 23:24)  Если суть замечаний - в наличии термического барьера, то это изменить нельзя, т. к. есть требования на качество пайки. Нет таких требований ни в одном стандарте. Никак термалы на переходных не скажутся на паяемость BGA. Даже теоретически. Тем более на плате, которая имеет 16 слоев, из которых половина, наверняка - сплошная медь. Вы хоть представляете какая у такой платы "тепловая масса"? Сколько тепла нужно, что бы прогреть такую плату и она нормалькно спаялась? Каким образом те нещастные термалы на переходных как-то повлияют на качество пайки BGA? Смотрите в суть явлений и не обращайте внимание на маловразумительные требования... P.S. Вы попробуйте помоделировать влияние термалов на пути обратных токов в хайспид дизайне - будете удивлены. Цитата(Stepanich @ May 30 2018, 23:24)  Если суть замечаний - в наличии гарантийных поясков в слоях, где нет подключения к полигонам или проводникам, то это изменить нельзя, т. к. это требование стандарта IPC-3 (см. сообщение 21). Кроме того, их наличие не влияет на описанную проблему с цепью CK. Еще как можно изменить. На внутренних слоях отсутствие гарантийных поясков для преходных на слое где нет подключения - норма. Читайте стандарт IPC-A-600, IPC-6011, IPC-6012, например, и связанные с ними. Особенно те стандарты, которые относятися к проектированию скоротных плат . И это не зависит от класса надежности платы. Любой пятак на переходном - увеличение его паразитной емкости, увеличение влияние на трассу, которая возле этого пятака проходит на малом расстоянии... А наличие дополнительных емкостей, влияющих на импеданс линии - это как раз путь к уменьшению крутизны сигналов. Кроме того, открою вам "Страшную тайну" - многие производители печатных плат по умолчанию убирают пятаки на внутренних слоях где нет подключения к переходным отверстиям. Если, конечно, явно не запретить им этого. Для того в САМ-редакторах и существуют инструменты, позволяющие делать подобные манипуляции с дизайном. Цитата(Stepanich @ May 30 2018, 23:39)  Если переходное отверстие, к которому подключён контакт, соединено с массивной областью меди (полигоном), то при оплавлении паяльной пасты тепло может от контакта "перейти" к полигону, что снизит воздействующую на пасту температуру и не позволит получить надёжное паяное соединение. Для снижения риска этого эффекта добавляют термический барьер. Наличие термического барьера в данном случае - требование монтажного цеха, и отступать от него нельзя. Гнать ссаными тряпками техногов, дающих подобные советы. Бред полный. А как же переходные непосредственно в паде, переходные для отвода тепла от "пуза" различных LCC, QFN, от площадок LGA и прочих D2PAK-ов? Оно же местами работать не будет, от слова вообще, если тармалов на такие переходные накидать... ИМХО, подобные советы могут давать только монтажники, которые сами не пониманимают техпроцесса пайки, начитались где то мануалов 20-летней давности и патаются переложить все возможные проблемы на конструктора, создавая тому лишние сложности.

--------------------

Тезис первый: Не ошибается лишь тот, кто ничего не делает.

Тезис второй: Опыт - великое дело, его не пропьёшь :).

|

|

|

|

|

|

|

|

May 31 2018, 12:41 May 31 2018, 12:41

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

7 Series FPGAs SelectIO Resources User GuideThe memory interface related I/O standards such as SSTL and HSTL now support the SLEW attribute, and are selectable between both FAST and SLOW edge rates. The default SLEW for all I/O standards is SLOW, which has been the case for all I/O standards that supported the SLEW attribute in all previous FPGA families (namely LVCMOS and LVTTL). However, because this attribute is a new addition to the memory interface standards, if left unchanged (not specified in the RTL, UCF file, or I/O planning software), the default slew rates for these for these standards will result in much slower slew rates than in previous families. To achieve similar slew rates as in previous families, new designs now require the SLEW attribute to be specified and set

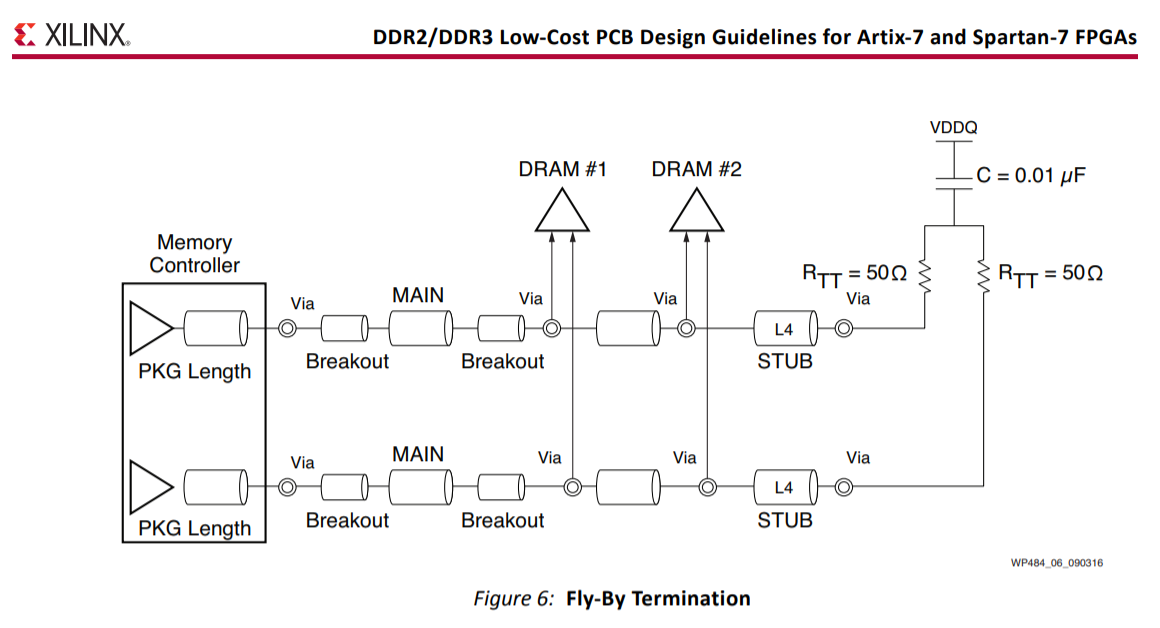

to FAST. Убедитесь что у вас не выбран reduced-strength driver - DIFF_SSTL15_R. Насколько можно понять по скринам, у вас для каждой микросхемы памяти отдельная шина адреса. Это вам действительно необходимо? Если нет - лучше используйте fly-by топологию.

Разрывать так плейны очень плохо. В Editor Control -> Tunning Patterns устанавите Miter ratio. То как вы подключаете low ESL кондеры, у вас похоже стоят 0306, нивелирует их характеристики. Да тут и не нужны 0306. Хотите понтов - ставте уже тогда NFM ы вдобавок к основным 0402. Только правильно их подключите. Да и так трассировать, в 16 слоях... Мой вам совет - откройте референс боард Кслаинкса и посмотрите как люди трассируют, тот же флай бай.

|

|

|

|

|

|

|

|

May 31 2018, 13:20 May 31 2018, 13:20

|

Гуру

Группа: Модераторы

Сообщений: 4 361

Регистрация: 17-08-04

Из: КП Две Поляны

Пользователь №: 512

|

Цитата(EvilWrecker @ May 30 2018, 21:12)  Это которая "export coupled segments"? Да. Цитата(EvilWrecker @ May 30 2018, 21:12)  Я может что-то в ветке пропустил, но у вас совершенно другая модель линии(в частности без виа)- особенно неясно почему нет TL между ддр3 и терминаторами, зато есть в самой терминации. Overshoot/pre-shoot как у ТС у вас нет, параметры TL между контролером и ддр3 разобрать нереально, но похоже что они одинаковые- что моделируется в этом сетапе?  Перечитайте мою фразу еще раз. Я удалил все лишние линии между передатчиком и приемником, чтобы показать что и в идеальном случае проблема останется. Цитата(EvilWrecker @ May 30 2018, 21:12)  Как вы себе это представляете? Например вот так

Играя номиналами резисторов можно управлять точкой пересечения фронтов.

--------------------

Чем больше познаю, тем больше понимаю ... насколько мало я все таки знаю. www.megratec.ru |

|

|

|

|

|

|

|

May 31 2018, 13:31 May 31 2018, 13:31

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Да. Понятно, спасибо- тогда позвольте уточняющий вопрос: это единственная галка которая управляет механизмом разбивки? О чем речь: соединение TL "бесшовное"в показанном ТС случае, но очевидно что при прямых(а тем более острых) углах, накрутке в антипаде и пр. соединение бесшовным быть не должно- т.е. в лучшем случае само число TL не будет равно числу сегментов трасс. Как происходит разделение? Цитата Перечитайте мою фразу еще раз. Я удалил все лишние линии между передатчиком и приемником, чтобы показать что и в идеальном случае проблема останется. Я понимаю о чем вы говорите  Мой посыл заключается в том, что не нужно лечить в одном месте- вот вы пишите: Цитата Например вот так Играя номиналами резисторов можно управлять точкой пересечения фронтов. можете гарантировать такой же эффект со стабильным повторением в оригинальной плате ТС- вестимо со всеми озвученными ранее проблемами? Это все хорошо работает, когда в остальных местах "проблем нет"  . Плюс overshoot у вас также остается(слегка переделанный проект ТС?)

|

|

|

|

|

|

|

|

May 31 2018, 14:02 May 31 2018, 14:02

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Он вас спрашивал только о том как решить проблему Vix. А вы вместо предложения решения уже 3 страницы обсуждаете его топологию. А что тут неясного? По умолчанию контроллер генерирует условно "нормальный" сигнал, ведь он сам по себе JEDEC- compliant, вы помните?  Стало быть, проблема как минимум в интерконнектах- минимум, потому что термалы в reutrn path дают массу неочевидных проблем, и это не касаясь темы PI. Что спрашивали, то и ответили  Цитата По поводу предложенной мной схемы согласования есть какие-то конкретные мысли? Желательно без словоблудия. Кроме факта того что она никоим образом не связана с платой ТС- никаких  Терминация клока сама по себе должна работать без всяких ухищрений в виде дополнительных согласований, все проблемы решаются или в интерконнектах или в настройках контроллера. Ваша модель имеет сугубо умозрительную ценность.

|

|

|

|

|

|

|

|

May 31 2018, 14:14 May 31 2018, 14:14

|

Местный

Группа: Свой

Сообщений: 284

Регистрация: 21-01-05

Пользователь №: 2 104

|

вот еще, в коллекцию. "Termination to GND is recommended for the clock signals to provide a good path for common mode noise." Не понимаю я смысл. В IBIS есть возможность выбора - SLOW, FAST. Ксайлинкс пишет что необходимо установить FAST. Так зачем в Hyperlynx менять? Ведь по установке этих галочек, Hyperlynx выбирает соответствующий режим в IBIS. Но мы же его сами должны установить DIFF_SSTL15_F(AST)_HR

|

|

|

|

|

|

|

|

May 31 2018, 14:59 May 31 2018, 14:59

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата "Termination to GND is recommended for the clock signals to provide a good path for common mode noise." Есть неплохие презентации( 1, 2), в которой перечислены причины возникновения CM noise в диффпаре(для тех кто не знает  )- так вот суть в том, что если в хайспидах внезапно в диффпаре много CM noise, то это означает что либо это не вполне диффпара, либо она говно  Цитата Так логичнее исправлять источник проблемы, а не бороться с последствиями. Именно.

|

|

|

|

|

|

|

|

May 31 2018, 15:16 May 31 2018, 15:16

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Всем доброго дня. 1. Ошибка с различным расстоянием между проводниками устранена.

Выполнено сравнительное моделирование "ДО" и "ПОСЛЕ".

Бирюзовый и фиолетовый - "до". Красный и зелёный - "после". Разница практически отсутствует. 2. IBIS модель драйвера: SSTL15_F_HR (прикладываю):  SSTL15_F_HR.txt

SSTL15_F_HR.txt ( 38.17 килобайт )

Кол-во скачиваний: 163. Посадочное место под конденсаторы LLL153C70G474ME17:

|

|

|

|

|

|

|

|

May 31 2018, 15:48 May 31 2018, 15:48

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Выполнено сравнительное моделирование "ДО" и "ПОСЛЕ". По правде говоря учитывая все ваши промахи до этого видится затруднительным верить результатам моделирования под вашим авторством- есть стойкое мнение что вы это делаете не лучше чем разводите  С "моделью" ситуация аналогичная. К слову еще раз про терминацию- хилые тоже недалеко ушли от стандартного пути   Но вот что интересно стало-насколько понять, у вас ниже артикса 2 микрульки ддр3: они же на разные контроллеры заведены? Ну так, на всякий  Цитата Посадочное место под конденсаторы LLL153C70G474ME17 И что вы хотите этим сказать? В документе даны диапазоны, а у вас конкретные фиксированные числа- вот их и назовите.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|