Здравствуйте уважаемые форумчане!

Изучаю систему Cadence, в частности NC-Verilog и Genus

Синтезирую под библиотеку Silterra 180nm CL180G

Вот модуль 8-бит умножителя, который хорошо работает на частоте 130 Mhz

Код

module multik (clk, A, B, out, reset);

input clk;

input reset;

input [7:0] A;

input [7:0] B;

output [15:0] out;

reg [7:0] Ar,Br;

reg [15:0] out_r;

reg [7:0] helpers16 [40:0];

reg [15:0] helpers31 [40:0];

integer i;

always @ (posedge clk)

begin

Ar<=A;

Br<=B;

helpers31[0]<=Ar*Br;

for(i=1; i<10; i=i+1)

helpers31 [i] <= helpers31[i-1];

end

assign out=helpers31[i-1];

endmodule

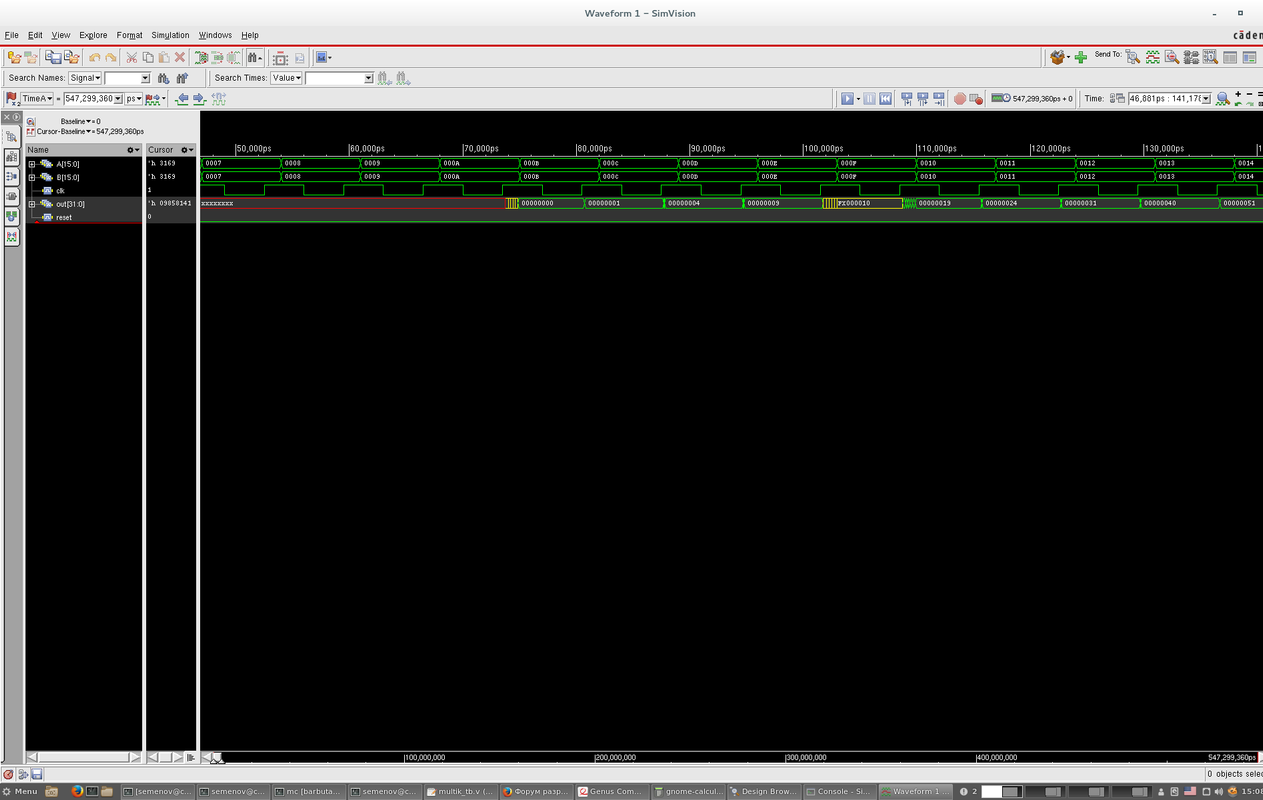

Вот код умножителя на 16-бит, который "захлебывается", т.е. периодически показывает неверные значения на частоте 130 Mhz. Во вложении скрин, там где желтые значения.

Код

module multik (clk, A, B, out, reset);

input clk;

input reset;

input [15:0] A;

input [15:0] B;

output [31:0] out;

reg [15:0] Ar,Br;

reg [31:0] out_r;

reg [15:0] helpers16 [40:0];

reg [31:0] helpers31 [40:0];

integer i;

always @ (posedge clk)

begin

Ar<=A;

Br<=B;

helpers31[0]<=Ar*Br;

for(i=1; i<10; i=i+1)

helpers31 [i] <= helpers31[i-1];

end

assign out=helpers31[i-1];

endmodule

Пробовал

retime -prepare

retime -min_delay

в надежде что генус раскидает регистры, и все заработает, но не вышло.

Отсюда возникает 2 вопроса

- какая существует тактика для перемножения больших чисел на больших частотах?

- как пользоваться командой генуса - retime?

Заранее спасибо за любые рекомендации!