Доброго всем времени суток!

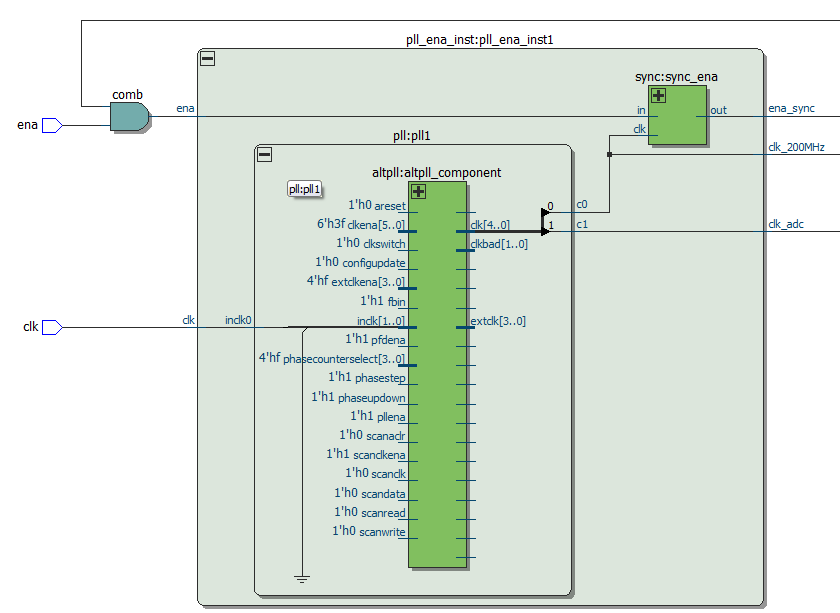

Делал проект на Cyclone III в Quartus 9.1, затем потребовалось перенести его на Cyclone IV EP4CE6E22I7, сейчас работаю в Quartus 15.0.0. pll добавлял из IP catalog, все настройки ставил по дефолту: один входной клок: 8МГц и два выходных: 200МГц и 32МГц. На вкладке "Operation mode" выбрал "Normal mode".

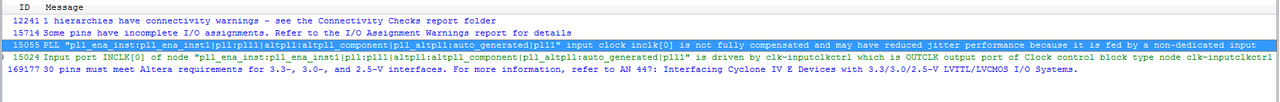

И вроде все нормально, камни очень похожие, но при компиляции появляется варнинг такого содержания:

RTL симуляция выглядит так:

Сигнал, поступающий на вход (inclk0 8МГц) объявлен как Global Clock и определен на ногу 23. Тактирование идет с микроконтроллера.

В констрейнах объявляю клоки следующим образом:

Код

create_clock -name clk -period 8MHz [get_ports {clk}]

create_generated_clock -name clk_200MHz -source [get_ports {clk}] -multiply_by 25 [get_nets {pll_ena_inst1|pll1|altpll_component|auto_generated|wire_pll1_clk[0]}]

create_generated_clock -name clk_adc -source [get_ports {clk}] -multiply_by 4 [get_nets {pll_ena_inst1|pll1|altpll_component|auto_generated|wire_pll1_clk[1]}]

Прошу совета - насколько критичен этот варнинг?

Заранее спасибо!

Сообщение отредактировал Sprite - Sep 27 2018, 13:34