Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Примеры _ Трассировка SDRAM

Автор: n_bogoyavlensky May 4 2010, 15:03

Здравствуйте!

Прошу покритиковать, выслушаю конкретные рекомендации.

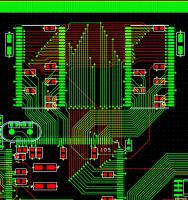

САПР - OrCAD.

ПП - 4 слоя (внутренние слои - общая цепь и питание +3.3 В, на рисунке не показаны).

Дорожки - 8 мил.

Дорожки цепей питания и общей - 11 мил.

Зазоры - 8 мил.

Трасировка шины данных - точка-точка, шины адреса и линий управления - Т-образная.

SDRAM - MT48LC16M16A2P-75IT.

МК - AT91SAM9XE512-QU.

Хотелось бы как-нибудь обжать трассировку памяти и микроконтроллера, чтобы меньше места она занимала.

Последовательные резисторы и терминирующие резисторы в цепи МК-память пока не поставил.

Насколько это принципиально? Как зависит от частоты и длины трасс необходимость их присутствия?

Рядом с МС памяти - электролиты 10 мкФ. Нормально ли я их расположил с точки зрения выполняемых ими функций?

Благодарю заранее!

Автор: Uree May 4 2010, 20:12

Нормальная такая трассировка, особо ее не ужмешь. Ну и на таких длинах имхо последовательные резисторы еще не нужны.

Автор: aaarrr May 4 2010, 20:38

Подключение земли у 28-го вывода правой СДРАМины выполнено в стиле "ужас-ужас". Да, и обязательно ли было все конденсаторы ставить на BOT'е, когда TOP свободен практически? Плата, как я вижу, не плотная, обычно в таких случаях я стараюсь использовать только одну сторону под компоненты - так удобнее и при ручном, и при автоматизированном монтаже.

Ну и последний штрих - внизу справа у микросхемы в SOIC8 (по всей видимости это 24xx) очень некрасиво соединены выводы прямо через центры площадок.

Автор: dch May 5 2010, 00:58

иногда проводники ведут от пина к пину, не допуская тобразных разветвлений и на сдраме конденсаторов помоему больше.

Автор: AlexN May 5 2010, 02:39

про 28 ногу провой sdram согласен с aaarrr, лучше сделать как у левой. Кашерность T-соединения лучше промоделировать в гиперлинксе, у оркада вроде есть туда экспорт. Важно: правильный стэк печатной платы, а именно расстояние от слоев разводки до слоя земли/питания для обеспечения целостности сигналов и импедансов. Для ваших ширин (8mil) 0.178мм даст примерно 60 ом, что вполне допустимо, 0.127мм - 50ом, что "типа идеально". Общюю необходимую толщину платы подгоняете толщиной core (между двумя внутренними слоями).

последовательный резистор в цепи клоков - обязателен, в остальных - "не повредит" - точно. И еще, для полного счастья зазор от линии клоков до соседних делается 2x от ширины проводника - для уменьшения crosstalk от соседей.

В целом, если первый раз - очень неплохо.

Автор: Secter May 5 2010, 03:03

"Обжать" трассировку, сдвинув правый (рис) корпус SDRAM влево убрав линию переходных отв.между корпусами. К примеру http://electronix.ru/redirect.php?http://www.mentorel.ru/images/sbc-9263t_big.jpg

Автор: AlexN May 5 2010, 03:33

в вашем примере технологические нормы гораздо жестче, как минимум 5mil/5mil

Автор: Secter May 5 2010, 05:09

Нормы проектирования здесь не причем... Правая сторона ARMа (рис) так и просится в разводку не через множественные-лишние переходные, а именно сдвинув SDRAM влево. Сразу ложатся на "правильной" стороне конденсаторы по питанию памяти. Конденсаторы по питанию ARMа тоже не на месте...спрашивается: зачем питание проца и граунд рядом?!...если кондер по питанию имеет "СВОЮ" землю?!

Автор: Uree May 5 2010, 07:12

Не те здесь еще скорости, чтоб без моделирования не работало. Они даже на обычном ДДРе еще не будут "теми", так что можно не напрягаться.

Что-то Вы здесь не то насчитали. Для начала 8мил равно не 0.178мм, а 0.203мм. Во-вторых уменьшение ширины трассы при неизменном стэке работает с точностью до наоборот - уменьшая ширину увеличиваем импеданс трассы, а у Вас он почему-то уменьшается(кстати поэтому питания лучше делать как можно шире). В-третьих 50 Ом совсем и не требуется для СДРАМа, это строгое требование для ДДР2, причем уже для быстрых. А здесь 55-65 Ом обычно применяется.

Ну просится, да. Распиновка явно рассчитана на последовательную трассировку шины адресов. Но человек принципиально делал Т-образную. А я советуя вначале понятия не имел о распиновке проца

Автор: AlexN May 5 2010, 11:28

речь шла о расстоянии до слоя земли - 0.178мм и 0.203мм, почему такие числа - видимо это стандартные толщины препрегов

Автор: Uree May 5 2010, 12:10

Ааа, тогда сорри. Хотя стандартные препреги тоже немного другой толщины... Но всегда есть возможность "ужать" посильнее![]()

Автор: Jul May 5 2010, 17:31

Переходные, поставленные плотным рядком, обеспечат разрыв в полигоне возвратных токов.

Соединение соседних площадок (Soic-8) - должны быть вне зоны пайки.

Кварц "нависает" над выводами микросхемы. Конденсаторы около кварца расположены не на той стороне.

Шелкография тантала как-то "узковата" - в реальности пошире будет.

Переходные отверстия, при наличии свободного места, не стоит загонять под корпуса микросхем.

Автор: Secter May 6 2010, 08:55

Есть похожий проект на AT91SAM9XE512-QU , но без динамики. Может что ВАМ пригодится-поможет. Материал TG170 (описание стека прилагаю), нормы проектирования 6/6mil, с количеством слоев не жался по причине мизерной стоимости ПП на выходе (10 ам.президентов за штуку).

http://electronix.ru/redirect.php?http://radikal.ru/F/i038.radikal.ru/1005/3e/a6d0d6898414.jpg.htmlhttp://electronix.ru/redirect.php?http://radikal.ru/F/s56.radikal.ru/i154/1005/b9/b84f4752a90c.jpg.htmlhttp://electronix.ru/redirect.php?http://radikal.ru/F/s52.radikal.ru/i136/1005/cd/b767ac40b39a.jpg.htmlhttp://electronix.ru/redirect.php?http://radikal.ru/F/s45.radikal.ru/i108/1005/14/ef70fa2d6733.jpg.htmlhttp://electronix.ru/redirect.php?http://radikal.ru/F/s61.radikal.ru/i173/1005/a8/468cc016cf66.jpg.htmlhttp://electronix.ru/redirect.php?http://radikal.ru/F/s16.radikal.ru/i191/1005/f8/a1413b09602d.jpg.htmlhttp://electronix.ru/redirect.php?http://radikal.ru/F/s43.radikal.ru/i100/1005/c7/7cece5215940.jpg.html

Автор: n_bogoyavlensky May 8 2010, 08:30

Сгенерил отчёт по длинам цепей.

Результаты следующие.

Для DO-D15: 22...35 мм. Разница приблизительно в 1.6 раза.

Для D16-D32: 12...25 мм.. Разница приблизительно в 2.1 раза.

Как посчитать время прохождения сигнала по трассе с известными параметрами?

Возможно, но это, я смотрю, спорный вопрос...

Вообще, может, и до моделирования когда доберусь

Плату сделаем, посмотрим.

Надо будет оттестировать память на максимальной частоте. И в требуемом температурном диапазоне (хотя бы пару точек взять крайних или около того).

Хотя, конечно, предполагается, что память будет работать на достаточно низкой частоте.

Лучше пользовать какой-нибудь готовый тест для линуха типа Memtest86?

Полностью согласен! Фанауты стараюсь делать с наикоротчайшими стрингерами

Пофиксил давно.

Плата не очень плотная... особенно рядом с SDRAM. Это сделано преднамерено, дабы трассировку SDRAM выполнить максимально близко к рекомендациям... и всё равно не удалось сделать всё правильно на 100%

Слева от левой микросхемы и справа от правой место для конденсаторов, конечно есть. А вот между микросхемами конденсаторы при такой трассировке поставить уже весьма проблематично, придётся и микросхемы раздвигать и дорожки растаскивать... Хотя виасы в цепи блокировочных конденсаторов тоже плохо... как там, дополнительно 0.5-1 нГн в цепи

На одной стороне все компоненты расположить не получится для данных габаритов платы и 4 слоёв... на нижнем слое ещё много чего расположено.

До сих пор понять не могу, почему некрасиво? Очень аккуратно, компактно, красиво

Кстати, DRC тоже ругался (bad pad exit).

Пофиксил, но не вижу пока в этом острой необходимости. Буду рад, если разъясните

Хм... для линий адреса и управляющих мне порекомендовали Т-образную трассировку.

Для линий данных - точка-точка.

http://electronix.ru/forum/index.php?showtopic=75593&view=findpost&p=750191

Т-образные разветвления, как я понимаю, вносят дополнительную неоднородность для сигнала, нехорошо, конечно...

Ну а если шлейфом вести от микросхемы к микросхеме? Длина линий увеличится...

Кстати, изначально я думал об этом... если смотреть на мой рисунок, то можно было бы петлёй справа от процессора вывести эти линии и соединить с правой микросхемой, а далее - пустить на левую...

Но меня остановило существенное увеличение длины линий, увеличение площади трассировки и... рекомендации, данные производителем и читателями форума

7 штук. По числу выводов питания.

Я ещё по одному танталлу поставил... как рекомендует производитель

Сделал почти как у левой... вверх стрингер отвёл (правда подлиннее, чем у левой получилось раза в 2-3).

Может, конечно, следовало сделать вточности как у левой... и линии адреса просто раздвинуть, для того чтобы виас туда влез...

Надеюсь, со временем доберусь до этого

Сложно там моделировать?

Согласен... не учёл этого, каюсь, каюсь...

Хотя видел рекомендации где-то по обеспечению сопротивления вообще всех трасс 50 Ом.

Но это, актуально, конечно, в большей степени только для трасс памяти (и других ВЧ).

0.127 мм - для импеданса хорошо, но тонковаты, конечно. Не каждый производитель ПП сможет...

Хотя ориентировались на ТеПро сначала (потом, правда не срослось с ним), который обещает 0.1 мм, что-то меня удержало сделать толщину трасс в 5 мил

Для SDCK?

Как я понимаю, ставится он ближе к источнику сигнала (процу) и служит для уменьшения "звона" в цепи? Типа ослабляется отражённый сигнал? И фронты немного "размазываются"?

Ну вообще да, производитель рекомендует зазоры между всеми группами сигналов делать...

ARM9 & SDRAM - первый раз

В следующий раз, постараюсь всё учесть полностью

Автор: n_bogoyavlensky May 8 2010, 10:03

Класс точности у Вас-то повыше будет!

И слоёв, думаю, 6 минимум...

А вот у нас бюджет существенно обрезан...

Согласен. Надо будет попробовать в следующем релизе осуществить... но не знаю, уместится ли столько виасов нормально под правой микросхемой...

Конденсаторы, как я понимаю, у Вас тоже на обеих сторонах расположены...

Как я понимаю, располагать конденсаторы на обратной стороне не есть слишком плохо.

Хотя, конечно, виас добавляет индуктивности паразитной...

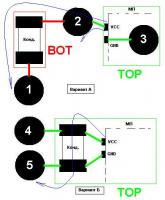

Хм... т. е., Вы хотите сказать, что общую цепь развязывающего конденсатора надо непосредственно соединять с общей цепью микропроцессора (GND)?

Рисунок ниже. Набросал по-быстрому для прояснения ситуации

В данный момент большая часть соединениий выполнена по варианту "А".

Конденсатор и процессор на разных сторонах платы.

ВЧ-ток через конденсатор и виас 1 уходит в плэйн-слой GND. Частично, конечно попадает через виас 2 в плэйн-слой питания.

Вы, как я понимаю, рекомендуете вариант "Б"?

Конденсатор и процессор на одной стороне платы.

Меньшая часть ВЧ-тока попадает в плайн-слой питания.

Можно сэкономить на одном виасе, да.

Но не подбросит ли ВЧ-ток, проходящий через конденсатор и виас 5, потенциал на выводе процессора GND?

Хм... интересно, можно ли это всё смоделировать в каком-нибудь гиперлинксе?

Автор: aaarrr May 8 2010, 10:09

ИМХО, Вы слишком переживаете. Здесь далеко еще не те частоты и длины цепей, чтобы убиваться из-за разводки.

Так это и будет "сопля" при монтаже, а оно надо?

Автор: n_bogoyavlensky May 8 2010, 10:18

Понятное дело

Но трассировать проще.

Виасы ставить подальше друг от друга?

Почему?

Не нависает. Он установлен с другой стороны платы

На той

Хм... взял стандартный корпус под тантал "A".

http://electronix.ru/redirect.php?http://lib.chipdip.ru/074/DOC000074919.pdf

Ширина корпуса - 1.6 мм.

У меня - 2.2 мм.

Мало?

Из тех соображений, что переходные отверстия могут быть неметаллизированы и их придётся пропаивать?

Автор: n_bogoyavlensky May 8 2010, 13:41

Ок

Практика покажет.

Неа

А если их ещё и порезать впоследствии придётся... то снаружи удобнее.

Спасибо. Посмотреть интересно

Я смотрю, Вы использовали выравнивание длины некоторых трасс (процессор-PHY) для PHY? Насколько это критично?

Под разъёмом Ethernet, как я вижу, у вас полигоны заземления во всех слоях?

Имеется ли у вас высоковольтный конденсатор между этим заземлением и общей цепью платы?

В некоторых местах у Вас развязка состоит из двух запараллеленных конденсаторов (0.1 и 0.01) как я понимаю? В каких местах?

Автор: Secter May 8 2010, 16:02

Под разъёмом Ethernet, как я вижу, у вас полигоны заземления во всех слоях?

Имеется ли у вас высоковольтный конденсатор между этим заземлением и общей цепью платы?

В некоторых местах у Вас развязка состоит из двух запараллеленных конденсаторов (0.1 и 0.01) как я понимаю? В каких местах?

Руководствовался исключительно рекомендациями http://electronix.ru/redirect.php?http://www.eltech.spb.ru/micrel_ethernet.html?id=20 , раз ТРЕБУЮТ значит нада!!! По поводу керамики на выводах QFP208 есть хороший пример-рекомендации по трассировке Fujitsu MB91F362, после праздников поищу. С параллельными конденсаторами, все правильно 0.1uF, 10nF,1nF, 1uF + bead+ тантал case A... усе согласно даташиту, равномерно распределил по корпусу...

Автор: n_bogoyavlensky May 8 2010, 18:10

Буду ждать

Основной даташит на проц?

Какой использовали?

Автор: Secter May 11 2010, 14:13

К вопросу о конденсаторах http://electronix.ru/redirect.php?http://depositfiles.com/files/g89slzvbx , развернутые рекомендации-пояснения использовал в проекте, лет пять взад...

http://electronix.ru/redirect.php?http://radikal.ru/F/s44.radikal.ru/i105/1005/98/8be8b50f0f78.jpg.html .

Предполагаю ЧТО с рекомендациями doc6385, ВЫ знакомы... в принципе интересующий Вас вопрос в необходимом объеме рассмотрен... http://electronix.ru/redirect.php?http://www.atmel.com/dyn/resources/prod_documents/doc6386.pdf

Автор: dch May 12 2010, 01:32

Для линий данных - точка-точка.

для точки проще считается, пальцевый расчет прост - завал фронта на единицу длины проводника умноженное на суммарную длину проводника достаточно хорошо отражает картину

Автор: n_bogoyavlensky May 14 2010, 17:03

Может быть задержка фронта (распространения сигнала), а не завал фронта?

Т. е., т. о. мы получаем задержку сигнала цепью. Это понятно

Автор: dch May 15 2010, 02:44

сигнал обыно быстро идет :-), считайте для простоты фронт заваливается.

Автор: n_bogoyavlensky May 23 2010, 19:43

Ну вообще да, так правильнее.

Именно завал фронтов (так как имеется ёмкость монтажа), как следствие - задержка

Русская версия Invision Power Board (http://www.invisionboard.com)

© Invision Power Services (http://www.invisionpower.com)