Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Zuken CADSTAR _ Zuken & FPGA

Автор: Frederic Dec 8 2012, 22:39

бегло просмотрел рекламу по Zuken CADSTAR и возник вопрос - как построена работа с FPGA ?

на уровне Pcad2006 или на других принципах ?

Автор: Yuri Potapoff Dec 9 2012, 15:51

Так как "на уровне Pcad2006" - это означает "никак", то правильно будет ответить "на двугих принципах".

Принцип этот заключается в интеграции со специализированным продуктом Aldec Active-HDL.

Здесь все написано:

http://electronix.ru/redirect.php?http://www.zuken.com/en/products/pcb-design/cadstar/downloads/fpga

Автор: Frederic Dec 10 2012, 21:52

....

Здесь все написано:

http://electronix.ru/redirect.php?http://www.zuken.com/en/products/pcb-design/cadstar/downloads/fpga

достойный ответ

скачал, почитал, посмотрел zuken.com/.../downloads/movies в части FPGA и возникли вопросы чисто теоричческого характера, т.к изучать глубоко Zuken нет времени, остаюсь фанатом IOD

понравилось, что работа идет только в SCH-PCB, но есть не понятные моменты в идеологии работы:

1.символы FPGA берутся из lib (как в Pcad), но я хочу иметь один сивол на всю FPGA за исключением символа питания (символы генерятся автоматом под конкретный проект и раскладку для каждой FPGA)

2.лень подключать шину 64bit к каждому pin символа (хотя есть механизм подключения показанный в Add Bus) - возможно подключит шину к pin с функцией шины (это вытекеат из п.1)

3.где задаются эквалентность пинов для каждого банка и для всей FPGA

4.не понял где находится автоматическая оптимизация шины по пинам (показали ручную по пинам с флажками)

может есть фильм продвинутого пользовате Zuken где показан весь цикл SCH-FPGA-PCB с FA&BA?

Автор: Yuri Potapoff Dec 12 2012, 13:38

не разбирался с этим подробно, пишу, как сам понял

символ не берется из библиотеки, а создается по файлу распиновки из альдека.

не очень понял, что имеется в виду. но если шину прицепить к символу и отодвинуть, то все прицепится само.

как я понимаю, эквивалентность возникает в генераторе символов по инфомации из альдековского файла распиновки.

не очень понял о чем речь. подозреваю это делает автотрассировщик. ручной процесс показан для наглядности.

Автор: Frederic Dec 16 2012, 20:15

символ не берется из библиотеки, а создается по файлу распиновки из альдека

....

ок, получили распиновку из альдека

хотя смутно представляю как в альдеке предусмотреть раскладку шины под будущую разводку на плате

да ладно, как говорится вернемся к нашим баранам

кратко основные шаги в IOD:

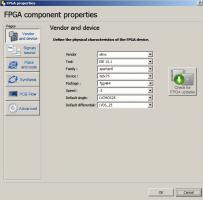

1.выбрал FPGA из базы рис. Symbol_Xilinx

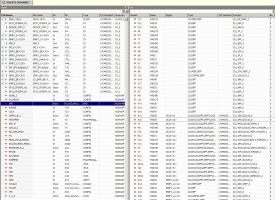

2.руками набил сигналы (или импорт) - раскидал сигналы по pin (рис. Signal-Pin)

уже в данном процессе проводится ручная оптимизация раскладки сигналов по пинам.

при не достаточном кол-ве пинов с фунцией IO из свободных пинов с другим типом например Clock/Diff/IO выставляется IO

указываю эквивалентность в каждом банке и в целом по всей FPGA

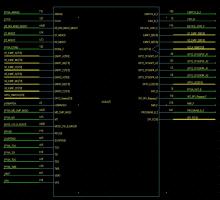

3.сгенерил символ (мне нравится функциональный, удобно работать с ним) рис. Symbol_FPGA

4.после экспорта символа в схему и далее в плату возможно сделать импорт размещения элементов на плате в IOD для проведения процесса "распутывания" цепей

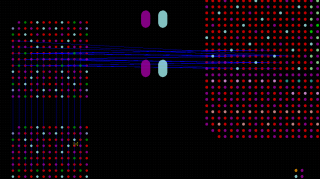

т.е. выделяется шина и выбирается процесс "распутывания" цепей и получется примерно так рис. Optima

далее update или повторная генерация символа и экспорт в схему

P.S. просто у меня маленький раслабон на пару дней и решил расширить кругозор

Автор: Uree Dec 16 2012, 23:50

Всегда глядя на такие картинки возникал только один вопрос - а как можно учесть фактический вывод трасс, а не просто красивые и упорядоченные линии связи?

Ну получил я какую-то вот такую картинку:

и что? Сильно по ней понятно КАК ИМЕННО должны быть раскиданы сигналы по пинам? Я и так знаю, что они должны быть в одном банке, но детали, где детали? Откуда я(или софт?!) знаю, как нужно вывести все эти сигналы, чтобы развелись в одном слое???

Вот здесь уже понятно, как оно получилось с обоих сторон и как их нужно было просвапить, чтобы все легло трасса в трассу:

А теперь у меня вопрос - так в чем глубокая ценность IOD в Mentor, FPGA System Planner в Cadence, механизма в CADSTAR(не знаю, как он называется) и подобных? Пока ничего, кроме возможности сгенерить символ на основе базы предусмотренной в этом софте не вижу... Не туда смотрю?

Автор: Frederic Dec 17 2012, 06:34

......

полностью с вами согласен, но имея уже такую картинку (а не пересекающие связи) в Ехр уже проще делать своп пинов для разводки шины в одном слое

А теперь у меня вопрос - так в чем глубокая ценность IOD в Mentor, FPGA System Planner в Cadence, механизма в CADSTAR(не знаю, как он называется) и подобных?

к сожалению не знаю как работает "...FPGA System Planner в Cadence, механизма в CADSTAR....", по этому решил задать этот вопрос

да, смотрите очень узко (очень наглядно процесс работы в IOD показан в фильмах у fill)

могу сказать только про IOD

генерация символа это просто вершина айсберга, хотя и на этом экономия времени существенное

P.S. жаль, что в ветке по Zuken нет гуру

может Юрий запросит у японцев фильм минут на 10....12 показывающий полный цикл работы с FPGA

Автор: Uree Dec 17 2012, 07:56

Вот я и спрашиваю - так что же там под водой? Можно на словах, без фильмиков.

ЗЫ Фильмики смотрел, вопрос по теме остался.

ЗЫЫ FPGA SP от Cadence - брат-близнец IOD, даже выглядит очень похоже.

Автор: Yuri Potapoff Dec 19 2012, 06:31

Причем здесь японцы? Софт пишется в Бристоле.

Русская версия Invision Power Board (http://www.invisionboard.com)

© Invision Power Services (http://www.invisionpower.com)