Версия для печати темы

Нажмите сюда для просмотра этой темы в обычном формате

Форум разработчиков электроники ELECTRONIX.ru _ Работаем с трассировкой _ Трассировка DDR3

Автор: HFSS Sep 15 2017, 04:40

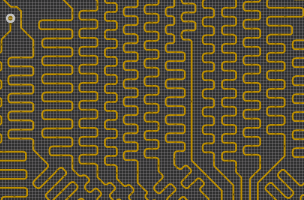

Как считаете не слишком ли близко расположены трассы шины данных DDR3 ?

Ширина дорожек 0,075 мм, расстояние меджу дорожками не менее 0,21 мм.

Автор: makc Sep 15 2017, 05:43

У производителей есть рекомендации по этой части. Посмотрите, например, от Xilinx  ddr3_layout.pdf ( 109.11 килобайт )

: 515

ddr3_layout.pdf ( 109.11 килобайт )

: 515

Автор: HFSS Sep 15 2017, 06:46

Спасибо.

В других анлогичных документах тоже рекомендуют выдерживать расстояние меджу трассами 3 ширины дорожки, но мне интересен опыт тех кто более плотно укладывал трассы.

Например, 2 ширины.

Автор: makc Sep 15 2017, 06:57

Например, 2 ширины.

Можно попробовать уложить и плотнее, но дальше все будет зависеть от везения, т.к. рекомендации написаны в расчете на общий случай. В качестве альтернативы могу лишь предложить попробовать промоделировать отдельный кусок в HyperLynx, но моделирование все равно не даст полной гарантии работоспособности во всем диапазоне внешних условий.

Автор: HFSS Sep 15 2017, 07:04

Maks, в вашем докементе есть рекомендация слок и стробы даннных выровнять до +\- 250 мил, я правильно это понял?

Просто в документе от микрон TN-41-08 , не сказано что клок и стробы надо между собой выравнивать.

Где правда?

Указано у микрона что шину адреса ровнять с клоком. Или я что то не так понял...

Автор: Uree Sep 15 2017, 07:07

Не знаю о чем именно в этом аппноте написано, но есть ощущение, что о "вообще". Ни слова о fly-by топологии при которой выравнивание Clock-to-DQS теряет смысл. Клок выравнивается к адресам/командам, но не к данным.

Автор: HFSS Sep 15 2017, 07:10

Uree, спасибо.

А то что то уже сомневаться начал.

Автор: makc Sep 15 2017, 07:23

Здесь, на сколько я понимаю, это требование обусловлено возможностями компенсации задержек в самом контроллере после калибровки. Поэтому этот параметр логичнее смотреть у разработчика контроллера DDR3, а не у производителя микросхем.

Не о "вообще", а в частности о ряде требований, которые обуславливаются физическими возможностями контроллера Spartan-6 (MCB). Но ряд требований относится к общим параметрам трассировки. А в комплексе это рекомендации, которые я привел для примера.

Автор: bloody-wolf Sep 16 2017, 08:39

требование расстояния меджу тррассами минимум в 3ширины дороги а лучше в 5, оно принципиально для ддр, которая например на 1866 работает. для вшивенького цинка или какого нибудь и.мх6 легко и не принужденно можно делать зазоры в 1.5 - 2 ширины и этого будет достаточно, ибо встроенные контроллеры памяти редко где могут в принципе работать быстрее, чем ддр 800.

вот если речь идет о плисовом МИГе, который треба стабильно раскочегарить на ддр1866 и более, там да, минимум 3, а лучше 5 ширин.

по пободу выравнивания, байты данных ровняют с соответствующим байтовым клоком довольно точно, я например делаю констрейны на 5 пс по плате. адреса и управление ровняют с просто клоком, я не заморачиваюсь и тоже делаю порядка 5пс.

а вот клоки данных и клок команд друг относительно друга можно выравнивать в верхнем пределе вроде бы до 250пс, у меня в констрейнах обычно 50пс

если смотреть в длинах проводников, хоть это и не правильно, то внутри групп до 0.1мм, от группы к группе до 1мм.

Автор: vvvv Sep 16 2017, 12:03

В других анлогичных документах тоже рекомендуют выдерживать расстояние меджу трассами 3 ширины дорожки, но мне интересен опыт тех кто более плотно укладывал трассы.

Например, 2 ширины.

А почему бы Вам не использовать тот самый HFSS и не вытащить s параметры в модель и засунуть ее в любой симулятор, а затем загнать тесты

по полной программе с IBIS моделями приемников и передатчиков, и вытащить eye diagram, ssn, выбросы, crosstalk, и посмотреть результаты тестов.

Модель можно погонять в различных режимах и с высокой вероятностью получить информацию о том можно или нельзя.

На практике ни одной ошибки в модели означает примерно 20% запас на практике, но это мое личное мнение.

Автор: bloody-wolf Sep 16 2017, 16:53

кстати еще рекомендуют совсем хай спид ровннять тромбоном, иногда кстати это даже не так уж и сильно площадь съедает. аргумент в пользу тромбона и против серпантина в том, что каждый угол, т.е.изгиб трассы являет собой излучатель вч, т.е. на изгибах трассы возникает местное сильное э.м.поле, и всяческие переотражения в том числе, т.е.по русски в тромбонах меньже изгибови лучше целостность сигнала. но это все скорее применимо к мегтрону/роджерсу и рокетам на частоты от 5-6 гигов. на обычном ддр3 1866 это даже и не видно.

ну и плюс слои сессна надо выбирать правильно, чтоб стабы поменьше были, ну и импедансы всеже 40 ом, ане 50, как многие делают.

многое зависьт от контроллера памяти еще, например марвелл в своей армаде нормальный контроллер памяти запилить не смог, поэтому номинально ддр3 поддерживался, но работал исключительно в режиме дерева ддр2 и никак иначе. потом, через несколько ревизий силикона, они таки запилили нормальный контроллер памяти и появился режим флайбай и остальные плюшки ддр3

Автор: HFSS Sep 18 2017, 03:41

по полной программе с IBIS моделями приемников и передатчиков, и вытащить eye diagram, ssn, выбросы, crosstalk, и посмотреть результаты тестов.

Модель можно погонять в различных режимах и с высокой вероятностью получить информацию о том можно или нельзя.

На практике ни одной ошибки в модели означает примерно 20% запас на практике, но это мое личное мнение.

К сожалению IBIS моделей нету. Да и времени на моделирование пока тоже нет.

Автор: _Sergey_ Sep 20 2017, 11:46

Ширина дорожек 0,075 мм, расстояние меджу дорожками не менее 0,21 мм.

Выглядит вполне себе приемлемо.

Я пользовался рекомендациями камрада Uree для байт-лэйна, правда по возможности увеличивал зазоры. Работает.

Автор: EvilWrecker Sep 28 2017, 06:31

Зазор измеряемый в ширинах трасс вполне себе рабочий и распространенный(использую сам время от времени), но самое лучшее значение это расстояние до опорного полигона- вот как раз тут 3H(Н - толщина между ближайшим медным слоем) вполне себе прекрасное значение. Опять же, уместно вспомнить что в расчет кросталков ключевой вклад дают в т.ч. rise/fall time и близость к опорному слою.

Для особо жестких и чувствительных сигналов зазор кладут более чем 7 толщин ![]() На рисунке ТС сигналы еще и лежат во внутренних слоях- нормальный зазор и нормальные меандры вполне.

На рисунке ТС сигналы еще и лежат во внутренних слоях- нормальный зазор и нормальные меандры вполне.

Сначала приведу ссылку на http://electronix.ru/redirect.php?http://www.keysight.com/upload/cmc_upload/All/1AgiAdvanced.pdf(стр.22)- что касается описанного вами: "излучение" это все очень относительно- излучает все, другой вопрос что является значимым в контексте задачи. Однако сам тромбон и тем более свичбэк являются очень полезными паттернами, потому как дают несравненно больший прирост длинны нежели аккордеон, да притом в меньших размерах на плате. Вместе с тем тромбон гораздо сложнее в реализации на плотных бордах, а свчибэк- самый сложный. Но этому имеет смысл научиться т.к. можно втаскивать невероятные дизайны.

Очень ситуативно

Автор: _alex__ Oct 3 2017, 20:29

Что такое "свичбэк" ?

Автор: EvilWrecker Oct 4 2017, 04:19

Грубо говоря, тромбон в один виток- который может идти по всей траектории движения проводника. Аккордеон наращивается "перпендикулярно" трассе, тромбон "параллельно"- оба на конкретный сегмент трассы, а свичбэк может выходить за пределы сегмента- "обтекает траекторию", примерно как на картинке.

http://electronix.ru/redirect.php?https://postimages.org/

Ясное дело свичбэк можно вытянуть из сегментов уже положенного аккордеона и тромбона.

Автор: MaxiZ Oct 4 2017, 09:47

Это (утрированно) одиночный тромбон.

Автор: EvilWrecker Oct 4 2017, 11:33

Именно.

Автор: _alex__ Oct 6 2017, 19:08

а в простейшем случае: микроконтроллер - одна микросхема ddr3, в идеале выравнивать нужно вообще все?

т.е. что б все проводники между микроконтроллером и микросхемой ddr3 давали одинаковую задержку?

Автор: EvilWrecker Oct 7 2017, 08:36

Ну у вас не мк(у них не бывает ддр3 контроллера

Я так понимаю вы даташиты не читали на камень? Это ваш первый дизайн с ддр3?

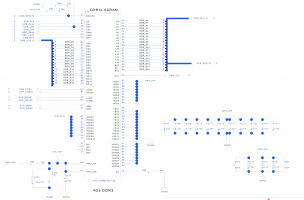

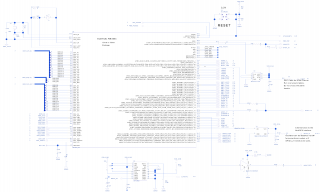

ПС. Не узнаю сапр- в чем схема сделана? И как вы можете читать текст при такой гамме?

Автор: _alex__ Oct 7 2017, 17:52

PoP это Point to Point?

Это вот отсюда схема:

http://electronix.ru/redirect.php?https://www.mentor.com/pcb/reference-designs/bb-bblk-000

Меня вот что интересует. Пускай между какими-то двумя микросхемами(не важно какими) есть некоторые high speed проводники.

Самый часто распространенный вариант это когда требуется выравнивать задержку всех проводников?

А реже когда нужно специально по каким-то отдельным проводникам выставлять запаздывание/опережение?

В каких интерфейсах(помимо подключения группы микросхем ddr) применяется не сплошное выравнивание?

Автор: EvilWrecker Oct 7 2017, 17:59

Это Package on Package.

Пфф, биглбон

Я не понял вопрос поэтому отмечу в общем ключе- есть матч группа, в которой выравнивается все: там могут быть и SE, и диффпары и комбо. В некоторых случаях есть зависимости между разными матчгруппами.

Несплошное выравнивание не осилил

Автор: _alex__ Oct 7 2017, 18:13

Пфф, биглбон

Я не понял вопрос поэтому отмечу в общем ключе- есть матч группа, в которой выравнивается все: там могут быть и SE, и диффпары и комбо. В некоторых случаях есть зависимости между разными матчгруппами.

Несплошное выравнивание не осилил

"не сплошное" выравнивание это я имел ввиду часто ли встречается необходимость выставления определенной разницы в задержках между проводниками(группами проводников)?

Автор: EvilWrecker Oct 7 2017, 18:15

В мире хайспидов это обыденность.

Автор: _alex__ Oct 7 2017, 18:50

приведите примеры интерфейсов(помимо ddr dimm), где между некоторыми проводниками этого интерфейса требуется выставлять определенную разницу в задержках.

Наверно PCI? Что еще?

Что б был понятнее мой вопрос, приведу примеры, где никакие разницы в задержках не нужны: USB, flash SPI.

Автор: EvilWrecker Oct 7 2017, 18:59

Наверно PCI? Что еще?

Зачем так скромно- просите(нет- требуйте!) сразу личную аудиенцию с обучением. Надо еще отдельного синьора позвать чтобы гуглил.

С чего вы взяли что в усб не важны задержки?

Автор: _alex__ Oct 7 2017, 20:43

а в usb требуется разность в задержках по сигнальным проводникам?

я прошу аббревиатуры интерфейсов привести где такое используется.

Автор: vladec Oct 9 2017, 09:44

Да хоть обычный Ethernet.

Автор: DieseL Nov 3 2017, 19:34

Всем привет. Решил тоже заглянуть и поприставать к Вам (ко всем) с вопросами по трассировке DDR. Кто ответит - буду весьма признателен.

Вот вопросы:

1. Подскажите, из всех цепей групп адресов, клока, даннх, команд какие цепи должны быть самые длинные? Цепи клока? Если да, то на сколько длиннее самой длинной цепи в пределах одного байта?

2. Слышал что у клока есть требование к определенной длине линий, например 2,25 дюйма (информация с IMX6DQ6SDLHDG.pdf) Хотя это может быть требование именно для клока с применением процессора IMX6DQ6SDLHDG

3. Обязательна ли трассировка всех цепей одного байта в одном слое для DDR3? Или можно в смежных слоях с общим опорным слоем делать и достаточно?

4. Что если в части опорного слоя применить плейн питания, можно так (я по краям плейна 0,01 мкФ конденсаторы по всему плейну постовлю от перепадов напряжения по плейну)

Автор: Inpharhus Jan 22 2018, 11:33

1. Обычно даётся разбежка плюс-минус относительно клока, либо разница между максимальной и минимальной длинами сигналов в группе байт+строб, у меня часто самыми длинными оказываются адреса. В одном из частных случаев например 9пс максимальная разница в группе байт+строб.

2. Скорее всего частный случай указанного процессора.

3. Можно в смежных, обычно так и делаю.

4. Скорее всего да, но никогда так не делал.

Автор: PCBtech Jan 29 2018, 09:38

Вот вопросы:

1. Подскажите, из всех цепей групп адресов, клока, даннх, команд какие цепи должны быть самые длинные? Цепи клока? Если да, то на сколько длиннее самой длинной цепи в пределах одного байта?

2. Слышал что у клока есть требование к определенной длине линий, например 2,25 дюйма (информация с IMX6DQ6SDLHDG.pdf) Хотя это может быть требование именно для клока с применением процессора IMX6DQ6SDLHDG

3. Обязательна ли трассировка всех цепей одного байта в одном слое для DDR3? Или можно в смежных слоях с общим опорным слоем делать и достаточно?

4. Что если в части опорного слоя применить плейн питания, можно так (я по краям плейна 0,01 мкФ конденсаторы по всему плейну постовлю от перепадов напряжения по плейну)

А у вас есть наша презентация с рекомендациями по проектированию плат с DDR?

Автор: Michkov May 25 2018, 10:58

Презентация Акулин А. "Проектирование многослойных плат с DDR" лист 41 Меандр или тромбон? электрические длины равны, а физическая- тромбон короче на 2 мм. Я правильно понимаю, что есть смысл перегонять разводку из Альтиума в Sigrity или Hiperlinx для моделирования и определения эл.длин?

p.s. если есть у когонить инструкция как это делается (пусть даже приблизительная, чтоб я понял куда "копать") поделитесь. Сам пока не определился какой пакет облегчит жизнь, пока подбираю инфу.

Автор: EvilWrecker May 25 2018, 11:20

Очень интересно- где бы почитать это дело? Это закрытый/платный документ?

Если дизайн и скорости того требуют- вполне.

В общем случае если нет прямого порта к формату файлов конкретного сапра, то следующим в списке импорт идет через ODB++. На прежде чем дойти до этого момента лучше определиться со следующим: что Вам удастся найти по документации(самостоятельно же осваиваете?), затачиваете ли знание под конкретного работодателя/работодателей, насколько глубоко хотите нырять в тему. Потому как на Sigrity и Hyperlynx свет клином не сошелся

Автор: Michkov May 25 2018, 12:51

да, конкретного нет , возможно что-нибудь найдется в сети. Нужно научиться моделировать , а не просто как художник зная общие принципы, аккуратно рисовать пп. Хотя если на самом деле моделирование будет слишком приближенным, может и не стоит -).

Автор: EvilWrecker May 25 2018, 13:01

Тут есть важный момент- если Вам необходимо решать "околотиповые" задачи в "околотиповых" дизайнах, то достаточно освоить методичку и набить потом руку. Если нужно глубокое понимание результата и серьезная работа с инструментом, то тут конечно мало знать сам софт- нужна подготовка в плане SI/PI теории(т.е. электродинамика), что в частности может означать фокус в сторону пакетов типа HFSS/ADS.

Вы какие задачи хотите решать? Какая сложность дизайнов?

Автор: Michkov May 25 2018, 13:19

Вы какие задачи хотите решать? Какая сложность дизайнов?

Для ddr3-4, да, "околотипичные", хочу методичку -)

Товарищ тут считает антены в HFSS,..но я не он -)

Автор: EvilWrecker May 25 2018, 13:39

В таком случае нет особой разницы какой симулятор для платок выбирать, однако скорее всего проще будет стартовать с Hyperlynx- у мегратека есть вполне хорошие(для старта)русскоязычные бумаги. На сигрити ничего подобного в открытом доступе никогда не видел ![]()

Ну и конечно же если будет интерес обратите внимание на ANSYS SIwave- да и собственно вообще на сам ANSYS HFSS.

Автор: Aner May 25 2018, 18:25

Юзал также CST pcb studio также очень полезная прога, из семейства проверки целостноси сигналов, цепей.

Автор: uriy May 25 2018, 18:29

Altium напрямую экспортирует в Hyperlynx.

С моделированием DSP+DDR обычно все проходит гладко.

С моделированием ПЛИС я встретил массу проблем. Для ПЛИС нет готового IBIS файла. Его надо сперва сконфигурировать назначив нужную функцию на пин.

Автор: Aner May 25 2018, 20:15

Стоит отметить что прямой импорт из Оркада, Экспедишина, Падса только. Была потребность из альтия, пришлось конвертнуть в Оркад.

Русская версия Invision Power Board (http://www.invisionboard.com)

© Invision Power Services (http://www.invisionpower.com)