Доброго всем.

Стоит задача сравнения результатов моделирования пакетов различных производителей.

Берём простейший testbench:

Код

`timescale 1ns / 100ps //

`define PERIOD_OF_CLK 10 // 100MHz => 10ns with respect to timebase (1ns)

`define HALF_PERIOD_OF_CLK (`PERIOD_OF_CLK / 2)

`define END_TIME 50 // 50ns

module test_tb;

reg clk_tb = 1'b0;

initial begin

$dumpfile("test_tb.vcd");

$dumpvars( 1, clk_tb);

end

initial begin

#0 clk_tb = 1'b0;

forever

#`HALF_PERIOD_OF_CLK clk_tb = !clk_tb;

end

initial begin

#`END_TIME $finish;

end

endmodule

И моделируем там и там.

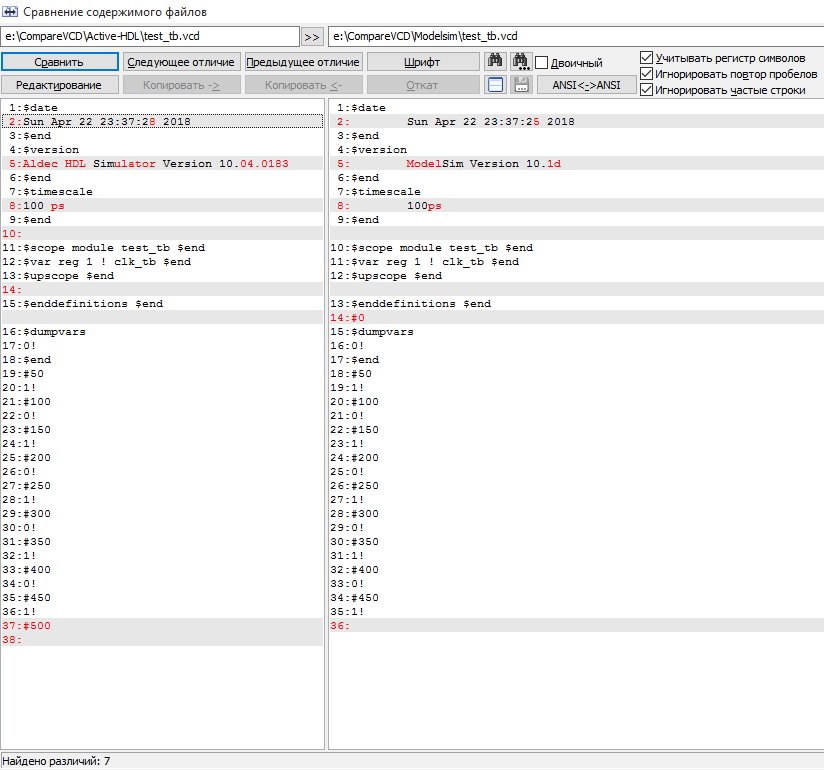

В результате получаем два vcd, сравнивая которые видим два существенных отличия:

1 в vcd от Aldec-а в последней строке есть временная метка #500 (файл от Mentor-а оканчивается на предыдущей строке) и

2 в vcd от Mentor-а в строке 14 есть временная метка #0 (файл от Aldec-а этой метки не имеет).

Поясните, плиз, кто может.

Для примера прилагаю проект с каталогами скриптов Mentor-а, Aldec-а и найденный в интернете java-скрипт сравнения двух vcd, вокруг которого всё и крутится (на исполнения запускается CompareVCD\comparevcd.cmd, в котором прописать две переменные с путями к исполняемым файлам Mentor-а и Aldec-а:

set Mentor_bin_path=d:\altera\13.0sp1\modelsim_ase\win32aloem

set Active_HDL_bin_path=C:\Aldec\Active-HDL-10.4\bin

)