Развел плату с несколькими процами.

TMS320 + DDR3 и OMAP L138 + DDR2.

Моделирование DDR3 прошло на ура. Вот картинки

Нажмите для просмотра прикрепленного файла

Нажмите для просмотра прикрепленного файла

DDR2 все плохо

Нажмите для просмотра прикрепленного файла

форма сигнала:

Нажмите для просмотра прикрепленного файла

Что в нем плохого? Мне он кажется вполне приемлемым. И что делать с платой? Или я что-то неверно задаю в hyperlynx?

Полная версия этой страницы: Hyperlynx DDR batch simulation

Форум разработчиков электроники ELECTRONIX.ru > Печатные платы (PCB) > Разрабатываем ПП в САПР - PCB development > Mentor PADS

В разделе Data Read тоже самое? А в модели на OMAP есть селектор выбора буффера? Если есть, то можно попробовать там поиграться.

В Data Read тоже bad signal по всем пунктам.

Нажмите для просмотра прикрепленного файла

Решил все начать с самого начала. Смутило вот это:

The following controller nets have inconsistent differential pins attached, based on IBIS modeling:

Сигналы DQS у OMAP и правда не дифференциальные. А вот с CLK похоже проблема.

Открываю ibis на TMS320 - есть раздел diffpin

Нажмите для просмотра прикрепленного файла

Открываю ibis на OMAP раздела diffpin не вообще

Нажмите для просмотра прикрепленного файла

Да действительно IBIS файл на OMAP L138 кривой https://e2e.ti.com/support/dsp/omap_applica...s/f/42/t/235021 и похоже TI не собирается его дополнять.

Добавил в IBIS:

Остаются еще вот такие предупреждения

Нажмите для просмотра прикрепленного файла

Data read и data write по прежнему bad signal, на зато теперь появилась вкладка Address где все сигналы Pass.

Нажмите для просмотра прикрепленного файла

Цитата

А в модели на OMAP есть селектор выбора буффера? Если есть, то можно попробовать там поиграться.

Есть. Только два варианта. Пробовал оба. Всегда bad signal.Нажмите для просмотра прикрепленного файла

Решил все начать с самого начала. Смутило вот это:

The following controller nets have inconsistent differential pins attached, based on IBIS modeling:

Код

Clock Net: DDR_CK_N ---

Pin: D1.K8 (-) IBIS Signal: u69a.ibs [MT47H128M16RT] CK#

Pin: U1.W7 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_CLKN

Clock Net: DDR_CK_P ---

Pin: D1.J8 (+) IBIS Signal: u69a.ibs [MT47H128M16RT] CK

Pin: U1.W8 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_CLKP

Data Strobe Net: DDR_LDQS ---

Pin: D1.F7 (+) IBIS Signal: u69a.ibs [MT47H128M16RT] LDQS

Pin: U1.T14 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_DQS0

Data Strobe Net: DDR_UDQS ---

Pin: D1.B7 (+) IBIS Signal: u69a.ibs [MT47H128M16RT] UDQS

Pin: U1.V11 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_DQS1

Pin: D1.K8 (-) IBIS Signal: u69a.ibs [MT47H128M16RT] CK#

Pin: U1.W7 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_CLKN

Clock Net: DDR_CK_P ---

Pin: D1.J8 (+) IBIS Signal: u69a.ibs [MT47H128M16RT] CK

Pin: U1.W8 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_CLKP

Data Strobe Net: DDR_LDQS ---

Pin: D1.F7 (+) IBIS Signal: u69a.ibs [MT47H128M16RT] LDQS

Pin: U1.T14 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_DQS0

Data Strobe Net: DDR_UDQS ---

Pin: D1.B7 (+) IBIS Signal: u69a.ibs [MT47H128M16RT] UDQS

Pin: U1.V11 (not differential) IBIS Signal: omapl138_zwt.ibs [OMAP-L138ZWT] DDR_DQS1

Сигналы DQS у OMAP и правда не дифференциальные. А вот с CLK похоже проблема.

Открываю ibis на TMS320 - есть раздел diffpin

Нажмите для просмотра прикрепленного файла

Открываю ibis на OMAP раздела diffpin не вообще

Нажмите для просмотра прикрепленного файла

Да действительно IBIS файл на OMAP L138 кривой https://e2e.ti.com/support/dsp/omap_applica...s/f/42/t/235021 и похоже TI не собирается его дополнять.

Добавил в IBIS:

Код

[font="Courier New"]|******************** DIFF PIN *******************************

[Diff_pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

W8 W7 NA NA NA NA || DDR_CLKP & DDR_CLKN[/font]

[Diff_pin] inv_pin vdiff tdelay_typ tdelay_min tdelay_max

W8 W7 NA NA NA NA || DDR_CLKP & DDR_CLKN[/font]

Остаются еще вот такие предупреждения

Нажмите для просмотра прикрепленного файла

Data read и data write по прежнему bad signal, на зато теперь появилась вкладка Address где все сигналы Pass.

Нажмите для просмотра прикрепленного файла

похожий вопрос про i.mx6

модели с ODT только входы (вроде кажется вполне разумным такое - что выход без ODT работает, но я не уверен), при этом если их ставить в ODT models / ODT enabled - hyperlinx ругается

Controller pin: U1003.G3 (DRAM_SDBA0) --Model is input only, but needs to be output or I/O

Model:

\ibis\mx6sx_bga17x17NP_autmtv.ibs[mx6sx_bga17x17NP] ddr3lodt_t60_sel11_mi

список моделей из файла ниже

с моделью самой памяти все нормально - там ODT модели вход-выход

в принципе ни разводка ни стекап платы не менялись (то есть есть очень похожая плата с рабочей DDR3 из которой кусок скопипасчен), но гиперлинк говорит, что работать не будет

когда я задаю модель *mi на ODT и игногрирую предупреждение гиперлинкса - получается вообще все плохо, когда задаю вместо ODT mio модель чуть лучше, но все-равно достаточно большое количество ошибок и в обе стороны (read/write)

сильно хотелось бы разобраться с этими ошибками/моделями, прежде чем отдавать плату в производство

но при этом хотелось бы получить это "искоропки" - так как Mentor рекламирует это DDR batch simulation

если это возможно и я просто не ту кнопку жму - спасайте

модели с ODT только входы (вроде кажется вполне разумным такое - что выход без ODT работает, но я не уверен), при этом если их ставить в ODT models / ODT enabled - hyperlinx ругается

Controller pin: U1003.G3 (DRAM_SDBA0) --Model is input only, but needs to be output or I/O

Model:

\ibis\mx6sx_bga17x17NP_autmtv.ibs[mx6sx_bga17x17NP] ddr3lodt_t60_sel11_mi

список моделей из файла ниже

с моделью самой памяти все нормально - там ODT модели вход-выход

в принципе ни разводка ни стекап платы не менялись (то есть есть очень похожая плата с рабочей DDR3 из которой кусок скопипасчен), но гиперлинк говорит, что работать не будет

когда я задаю модель *mi на ODT и игногрирую предупреждение гиперлинкса - получается вообще все плохо, когда задаю вместо ODT mio модель чуть лучше, но все-равно достаточно большое количество ошибок и в обе стороны (read/write)

сильно хотелось бы разобраться с этими ошибками/моделями, прежде чем отдавать плату в производство

но при этом хотелось бы получить это "искоропки" - так как Mentor рекламирует это DDR batch simulation

если это возможно и я просто не ту кнопку жму - спасайте

Код

[Model Selector] ddr

ddr3_sel11_ds111_mio DDR, 1.5V, ddr3 mode, 34 Ohm driver impedance

ddr3_sel11_ds110_mio DDR, 1.5V, ddr3 mode, 40 Ohm driver impedance

ddr3_sel11_ds101_mio DDR, 1.5V, ddr3 mode, 48 Ohm driver impedance

ddr3_sel11_ds100_mio DDR, 1.5V, ddr3 mode, 60 Ohm driver impedance

ddr3_sel11_ds011_mio DDR, 1.5V, ddr3 mode, 80 Ohm driver impedance

ddr3_sel11_ds010_mio DDR, 1.5V, ddr3 mode, 120 Ohm driver impedance

ddr3_sel11_ds001_mio DDR, 1.5V, ddr3 mode, 240 Ohm driver impedance

ddr3l_sel11_ds111_mio DDR, 1.35V, ddr3l mode, 34 Ohm driver impedance

ddr3l_sel11_ds110_mio DDR, 1.35V, ddr3l mode, 40 Ohm driver impedance

ddr3l_sel11_ds101_mio DDR, 1.35V, ddr3l mode, 48 Ohm driver impedance

ddr3l_sel11_ds100_mio DDR, 1.35V, ddr3l mode, 60 Ohm driver impedance

ddr3l_sel11_ds011_mio DDR, 1.35V, ddr3l mode, 80 Ohm driver impedance

ddr3l_sel11_ds010_mio DDR, 1.35V, ddr3l mode, 120 Ohm driver impedance

ddr3l_sel11_ds001_mio DDR, 1.35V, ddr3l mode, 240 Ohm driver impedance

ddr3odt_t17_sel11_mi DDR, 1.5V, ddr3 mode, 17 Ohm ODT

ddr3odt_t20_sel11_mi DDR, 1.5V, ddr3 mode, 20 Ohm ODT

ddr3odt_t24_sel11_mi DDR, 1.5V, ddr3 mode, 24 Ohm ODT

ddr3odt_t30_sel11_mi DDR, 1.5V, ddr3 mode, 30 Ohm ODT

ddr3odt_t40_sel11_mi DDR, 1.5V, ddr3 mode, 40 Ohm ODT

ddr3odt_t60_sel11_mi DDR, 1.5V, ddr3 mode, 60 Ohm ODT

ddr3odt_t120_sel11_mi DDR, 1.5V, ddr3 mode, 120 Ohm ODT

ddr3lodt_t17_sel11_mi DDR, 1.35V, ddr3l mode, 17 Ohm ODT

ddr3lodt_t20_sel11_mi DDR, 1.35V, ddr3l mode, 20 Ohm ODT

ddr3lodt_t24_sel11_mi DDR, 1.35V, ddr3l mode, 24 Ohm ODT

ddr3lodt_t30_sel11_mi DDR, 1.35V, ddr3l mode, 30 Ohm ODT

ddr3lodt_t40_sel11_mi DDR, 1.35V, ddr3l mode, 40 Ohm ODT

ddr3lodt_t60_sel11_mi DDR, 1.35V, ddr3l mode, 60 Ohm ODT

ddr3lodt_t120_sel11_mi DDR, 1.35V, ddr3l mode, 120 Ohm ODT

lpddr2_sel10_ds111_mio LPDDR, 1.2V, lpddr2 mode, 34 Ohm driver impedance

lpddr2_sel10_ds110_mio LPDDR, 1.2V, lpddr2 mode, 40 Ohm driver impedance

lpddr2_sel10_ds101_mio LPDDR, 1.2V, lpddr2 mode, 48 Ohm driver impedance

lpddr2_sel10_ds100_mio LPDDR, 1.2V, lpddr2 mode, 60 Ohm driver impedance

lpddr2_sel10_ds011_mio LPDDR, 1.2V, lpddr2 mode, 80 Ohm driver impedance

lpddr2_sel10_ds010_mio LPDDR, 1.2V, lpddr2 mode, 120 Ohm driver impedance

lpddr2_sel10_ds001_mio LPDDR, 1.2V, lpddr2 mode, 240 Ohm driver impedance

ddr3_sel11_ds111_mio DDR, 1.5V, ddr3 mode, 34 Ohm driver impedance

ddr3_sel11_ds110_mio DDR, 1.5V, ddr3 mode, 40 Ohm driver impedance

ddr3_sel11_ds101_mio DDR, 1.5V, ddr3 mode, 48 Ohm driver impedance

ddr3_sel11_ds100_mio DDR, 1.5V, ddr3 mode, 60 Ohm driver impedance

ddr3_sel11_ds011_mio DDR, 1.5V, ddr3 mode, 80 Ohm driver impedance

ddr3_sel11_ds010_mio DDR, 1.5V, ddr3 mode, 120 Ohm driver impedance

ddr3_sel11_ds001_mio DDR, 1.5V, ddr3 mode, 240 Ohm driver impedance

ddr3l_sel11_ds111_mio DDR, 1.35V, ddr3l mode, 34 Ohm driver impedance

ddr3l_sel11_ds110_mio DDR, 1.35V, ddr3l mode, 40 Ohm driver impedance

ddr3l_sel11_ds101_mio DDR, 1.35V, ddr3l mode, 48 Ohm driver impedance

ddr3l_sel11_ds100_mio DDR, 1.35V, ddr3l mode, 60 Ohm driver impedance

ddr3l_sel11_ds011_mio DDR, 1.35V, ddr3l mode, 80 Ohm driver impedance

ddr3l_sel11_ds010_mio DDR, 1.35V, ddr3l mode, 120 Ohm driver impedance

ddr3l_sel11_ds001_mio DDR, 1.35V, ddr3l mode, 240 Ohm driver impedance

ddr3odt_t17_sel11_mi DDR, 1.5V, ddr3 mode, 17 Ohm ODT

ddr3odt_t20_sel11_mi DDR, 1.5V, ddr3 mode, 20 Ohm ODT

ddr3odt_t24_sel11_mi DDR, 1.5V, ddr3 mode, 24 Ohm ODT

ddr3odt_t30_sel11_mi DDR, 1.5V, ddr3 mode, 30 Ohm ODT

ddr3odt_t40_sel11_mi DDR, 1.5V, ddr3 mode, 40 Ohm ODT

ddr3odt_t60_sel11_mi DDR, 1.5V, ddr3 mode, 60 Ohm ODT

ddr3odt_t120_sel11_mi DDR, 1.5V, ddr3 mode, 120 Ohm ODT

ddr3lodt_t17_sel11_mi DDR, 1.35V, ddr3l mode, 17 Ohm ODT

ddr3lodt_t20_sel11_mi DDR, 1.35V, ddr3l mode, 20 Ohm ODT

ddr3lodt_t24_sel11_mi DDR, 1.35V, ddr3l mode, 24 Ohm ODT

ddr3lodt_t30_sel11_mi DDR, 1.35V, ddr3l mode, 30 Ohm ODT

ddr3lodt_t40_sel11_mi DDR, 1.35V, ddr3l mode, 40 Ohm ODT

ddr3lodt_t60_sel11_mi DDR, 1.35V, ddr3l mode, 60 Ohm ODT

ddr3lodt_t120_sel11_mi DDR, 1.35V, ddr3l mode, 120 Ohm ODT

lpddr2_sel10_ds111_mio LPDDR, 1.2V, lpddr2 mode, 34 Ohm driver impedance

lpddr2_sel10_ds110_mio LPDDR, 1.2V, lpddr2 mode, 40 Ohm driver impedance

lpddr2_sel10_ds101_mio LPDDR, 1.2V, lpddr2 mode, 48 Ohm driver impedance

lpddr2_sel10_ds100_mio LPDDR, 1.2V, lpddr2 mode, 60 Ohm driver impedance

lpddr2_sel10_ds011_mio LPDDR, 1.2V, lpddr2 mode, 80 Ohm driver impedance

lpddr2_sel10_ds010_mio LPDDR, 1.2V, lpddr2 mode, 120 Ohm driver impedance

lpddr2_sel10_ds001_mio LPDDR, 1.2V, lpddr2 mode, 240 Ohm driver impedance

Модель контроллера я скачал.

Если пришлете или укажите ссылку на модель вашей памяти.

То могу попробовать поиграться в предтопологическом режиме.

Если пришлете топологию в HL с вашей настройкой визарда, то будет еще проще и быстрее понять проблему.

Если пришлете или укажите ссылку на модель вашей памяти.

То могу попробовать поиграться в предтопологическом режиме.

Если пришлете топологию в HL с вашей настройкой визарда, то будет еще проще и быстрее понять проблему.

спасибо.

я тему еще одну создал, но спрошу и тут - а нет ли возможности выжать из проекта топологии представление в виде линий задержек и абстрактной пасивки как в проекте linesim? топологию я пересылать "как есть" боюсь, чтобы не поиметь неприятностей по работе

если нельзя - то почищу все кроме этих двух микросхем и перешлю

прикладываю память и ddr визард

MT41K64M16TW

----------

upd: есть подозрение, что разводчик поменял топологию DDR - то есть я еще проверю формально по длинам проводников. но чтоб было - выкладываю редуцированый проект, там стекап из-за радио достаточно странный, но так надо - прошу обратить внимание на Zo по слоям где разведена DDR - по-моему, какое-то странное это Zo - посмотрите и на это, пожалуйста (по заявлениям мануфактуры должно быть 50 Ом)

- выкладываю редуцированый проект, там стекап из-за радио достаточно странный, но так надо - прошу обратить внимание на Zo по слоям где разведена DDR - по-моему, какое-то странное это Zo - посмотрите и на это, пожалуйста (по заявлениям мануфактуры должно быть 50 Ом)

---------

upd2: поправил стекап - задал plane-ы по слоям с землей - импедансы стали больше похожи на требуемые, но симуляция все-равно fail

также смотрю на задержки в linesim после экспорта - вроде бы разброс в допустимых ps

я тему еще одну создал, но спрошу и тут - а нет ли возможности выжать из проекта топологии представление в виде линий задержек и абстрактной пасивки как в проекте linesim? топологию я пересылать "как есть" боюсь, чтобы не поиметь неприятностей по работе

если нельзя - то почищу все кроме этих двух микросхем и перешлю

прикладываю память и ddr визард

MT41K64M16TW

----------

upd: есть подозрение, что разводчик поменял топологию DDR - то есть я еще проверю формально по длинам проводников. но чтоб было

---------

upd2: поправил стекап - задал plane-ы по слоям с землей - импедансы стали больше похожи на требуемые, но симуляция все-равно fail

также смотрю на задержки в linesim после экспорта - вроде бы разброс в допустимых ps

спасибо.

я тему еще одну создал, но спрошу и тут - а нет ли возможности выжать из проекта топологии представление в виде линий задержек и абстрактной пасивки как в проекте linesim? топологию я пересылать "как есть" боюсь, чтобы не поиметь неприятностей по работе

если нельзя - то почищу все кроме этих двух микросхем и перешлю

прикладываю память и ddr визард

MT41K64M16TW

----------

upd: есть подозрение, что разводчик поменял топологию DDR - то есть я еще проверю формально по длинам проводников. но чтоб было - выкладываю редуцированый проект, там стекап из-за радио достаточно странный, но так надо - прошу обратить внимание на Zo по слоям где разведена DDR - по-моему, какое-то странное это Zo - посмотрите и на это, пожалуйста (по заявлениям мануфактуры должно быть 50 Ом)

- выкладываю редуцированый проект, там стекап из-за радио достаточно странный, но так надо - прошу обратить внимание на Zo по слоям где разведена DDR - по-моему, какое-то странное это Zo - посмотрите и на это, пожалуйста (по заявлениям мануфактуры должно быть 50 Ом)

---------

upd2: поправил стекап - задал plane-ы по слоям с землей - импедансы стали больше похожи на требуемые, но симуляция все-равно fail

я тему еще одну создал, но спрошу и тут - а нет ли возможности выжать из проекта топологии представление в виде линий задержек и абстрактной пасивки как в проекте linesim? топологию я пересылать "как есть" боюсь, чтобы не поиметь неприятностей по работе

если нельзя - то почищу все кроме этих двух микросхем и перешлю

прикладываю память и ddr визард

MT41K64M16TW

----------

upd: есть подозрение, что разводчик поменял топологию DDR - то есть я еще проверю формально по длинам проводников. но чтоб было

---------

upd2: поправил стекап - задал plane-ы по слоям с землей - импедансы стали больше похожи на требуемые, но симуляция все-равно fail

А параметры стека правильные? Я поставил плейнами 2, 4, 6, 7, 9 и 11. Но просто смотрю получившийся импеданс на адресах и данных и он всего 36-38 Ом.Нажмите для просмотра прикрепленного файла

Вот при таком стекеНажмите для просмотра прикрепленного файла получим нужный импеданс.

можно предположить (другой информации у меня нет) если производитель говорит, что с такой толщиной препрегов требуется 0.08мм ширина дорожки для 50Ом и они будут контролировать импеданс - то может эпсилон у материала меньше. я с производством плат (и подготовкой документации для этого) имею дело не часто. но вот если прижмет, то приходится разбираться.

я ставил Er=3 и получал Zo 45-50 ОМ

непонятный кстати момент - почему при симметричном стекапе на симметричных слоях у меня получается разный Zo ??

но все-равно симуляция (с 40 Ом драйверами в моделях) не проходит, хотя ошибок меньше.

я так понимаю, что 40 Ом драйвера в моделях/микросхемах лучше согласованы будут - но нужно будет в linesim для отдельных цепей посмотреть...

я ставил Er=3 и получал Zo 45-50 ОМ

непонятный кстати момент - почему при симметричном стекапе на симметричных слоях у меня получается разный Zo ??

но все-равно симуляция (с 40 Ом драйверами в моделях) не проходит, хотя ошибок меньше.

я так понимаю, что 40 Ом драйвера в моделях/микросхемах лучше согласованы будут - но нужно будет в linesim для отдельных цепей посмотреть...

можно предположить (другой информации у меня нет) если производитель говорит, что с такой толщиной препрегов требуется 0.08мм ширина дорожки для 50Ом и они будут контролировать импеданс - то может эпсилон у материала меньше. я с производством плат (и подготовкой документации для этого) имею дело не часто. но вот если прижмет, то приходится разбираться.

я ставил Er=3 и получал Zo 45-50 ОМ

непонятный кстати момент - почему при симметричном стекапе на симметричных слоях у меня получается разный Zo ??

но все-равно симуляция (с 40 Ом драйверами в моделях) не проходит, хотя ошибок меньше.

я так понимаю, что 40 Ом драйвера в моделях/микросхемах лучше согласованы будут - но нужно будет в linesim для отдельных цепей посмотреть...

я ставил Er=3 и получал Zo 45-50 ОМ

непонятный кстати момент - почему при симметричном стекапе на симметричных слоях у меня получается разный Zo ??

но все-равно симуляция (с 40 Ом драйверами в моделях) не проходит, хотя ошибок меньше.

я так понимаю, что 40 Ом драйвера в моделях/микросхемах лучше согласованы будут - но нужно будет в linesim для отдельных цепей посмотреть...

Откуда взята такая цифра Er=3? Вы поинтересуйтесь у производителя плат, они же делают и знают. А только затем закладывайте в проект. У таких призводителей обычно есть опция измерения импеданса.

Просто вот интересно если это не роджерс, то что за препреги с таким эпсилон у вас?

можно предположить (другой информации у меня нет) если производитель говорит, что с такой толщиной препрегов требуется 0.08мм ширина дорожки для 50Ом и они будут контролировать импеданс - то может эпсилон у материала меньше. я с производством плат (и подготовкой документации для этого) имею дело не часто. но вот если прижмет, то приходится разбираться.

я ставил Er=3 и получал Zo 45-50 ОМ

непонятный кстати момент - почему при симметричном стекапе на симметричных слоях у меня получается разный Zo ??

но все-равно симуляция (с 40 Ом драйверами в моделях) не проходит, хотя ошибок меньше.

я так понимаю, что 40 Ом драйвера в моделях/микросхемах лучше согласованы будут - но нужно будет в linesim для отдельных цепей посмотреть...

я ставил Er=3 и получал Zo 45-50 ОМ

непонятный кстати момент - почему при симметричном стекапе на симметричных слоях у меня получается разный Zo ??

но все-равно симуляция (с 40 Ом драйверами в моделях) не проходит, хотя ошибок меньше.

я так понимаю, что 40 Ом драйвера в моделях/микросхемах лучше согласованы будут - но нужно будет в linesim для отдельных цепей посмотреть...

При такой настройке Нажмите для просмотра прикрепленного файла стека и визарда, ошибок в моделировании нет.

У меня импеданс одинаковый, просто в присланном вами, слой 2 не был плейном, поэтому и разница в Zo.

Чтобы быть уверенным в результатах моделирования нужно чтобы все параметры стека были близкими к тому что будет на производстве. Ведь все это влияет на время прохождения сигналов и их форму.

Я вижу что в топологии есть трассы (идущие на память) шириной 90мкм, 80мкм, и даже 75мкм.

Это вариант визарда Нажмите для просмотра прикрепленного файла тоже работает

огромное спасибо.

но, по-моему, дизайн плохой - CK короче DQS-ов,

то есть write leveling работать не будет. нужен ли этот write leveling для point-to-point непонятно, но вроде как формальное требование нарушено (а в рабочем дизайне, на который я сослался этого нарушения нет)

то есть придется с ddr разбираться, а настройки я сейчас проверю.

Er=3 это мои фантазии - то есть взяв толщины препрегов и ширины проводников как константы, подобрал, чтобы было близко к 50 Ом (ну чтобы проверить влияние на результат симуляции)

то есть у меня есть эксельная табличка от производителя, где стекап и толщины проводников для 50 Ом по разным слоям

материал не роджерс, текстолит, но там весьма хитрое производство (NEC) поэтому может и не FR-4, но из-за сложности общения я выяснять не буду

но, по-моему, дизайн плохой - CK короче DQS-ов,

то есть write leveling работать не будет. нужен ли этот write leveling для point-to-point непонятно, но вроде как формальное требование нарушено (а в рабочем дизайне, на который я сослался этого нарушения нет)

то есть придется с ddr разбираться, а настройки я сейчас проверю.

Откуда взята такая цифра Er=3? Вы поинтересуйтесь у производителя плат, они же делают и знают. А только затем закладывайте в проект. У таких призводителей обычно есть опция измерения импеданса.

Просто вот интересно если это не роджерс, то что за препреги с таким эпсилон у вас?

Просто вот интересно если это не роджерс, то что за препреги с таким эпсилон у вас?

Er=3 это мои фантазии - то есть взяв толщины препрегов и ширины проводников как константы, подобрал, чтобы было близко к 50 Ом (ну чтобы проверить влияние на результат симуляции)

то есть у меня есть эксельная табличка от производителя, где стекап и толщины проводников для 50 Ом по разным слоям

материал не роджерс, текстолит, но там весьма хитрое производство (NEC) поэтому может и не FR-4, но из-за сложности общения я выяснять не буду

Ну у вас всё с ног на голову поставлено. Потому, что никак не нужно подбирать Er, его должны дать для различных материалов он разный. Под FR-4 кучи различных материалов есть, но с 3 никогда не встречал, обычно от 4.2 до 5.2. И там особый момент это анизотропность. В даташитах это по вертикале материала FR-4, если он расположен горизонтально. А горизонтальный Er= 2.9 ... 4.0, но с частот выше определенной. Часто делают ошибки не зная о анизотропности на скоростых трассах применяя марки FR-4.

CK короче DQS-ов может быть читайте AN вашего DDR3L. write leveling может и не работать вовсе на низких скоростях, где оч большие задержки допустимы.

От тактовой зависит. У вас вроде не особо с быстрые чипы. Начиная с DDR3 и выше, у них оч навороченные лог-автоматы, самостоятельно принимают многие решения, как по синхронизации так и по тактированию, итд.

С DDR3, DDR3L всегда обходился 100, 70 микронными трассами, не приходилось уменьшать или использовать другие. Платы были 8-12 слойки. Но тут от стека, препрега выбор тоже зависим.

CK короче DQS-ов может быть читайте AN вашего DDR3L. write leveling может и не работать вовсе на низких скоростях, где оч большие задержки допустимы.

От тактовой зависит. У вас вроде не особо с быстрые чипы. Начиная с DDR3 и выше, у них оч навороченные лог-автоматы, самостоятельно принимают многие решения, как по синхронизации так и по тактированию, итд.

С DDR3, DDR3L всегда обходился 100, 70 микронными трассами, не приходилось уменьшать или использовать другие. Платы были 8-12 слойки. Но тут от стека, препрега выбор тоже зависим.

Ну у вас всё с ног на голову поставлено.

да, есть такое. но у меня была еще задача разобраться с гиперлинксом (все-таки инструмент крайне редко мной используемый), то есть хотелось иметь как успешные, так и неуспешные результаты ddr batch, сравнить их с linesim-ом для отдельных проводов/различных импедансов ibis моделей и т.д.

по поводу этой платы - выяснилось, что стекап мне прислали не тот - то есть в результате взаимодействия собственно разработчика платы и производства было несколько итераций и толщина препрегов менялась, то есть в финальной версии эти проводники 0.08/0.09 на разных слоях дают примерно 50 Ом

Как учитывается (и учитывается ли) Pin Delay при моделировании вообще и в DDR Batch Simulation в частности? Насколько вижу никак не учитывается, отсюда вопрос - а как учесть?

Как учитывается (и учитывается ли) Pin Delay при моделировании вообще и в DDR Batch Simulation в частности? Насколько вижу никак не учитывается, отсюда вопрос - а как учесть?

Нажмите для просмотра прикрепленного файла

Видел я этот файл и его содержимое... вот только данные в нем не особо соотносятся с тем, что есть в плате. Собственно поэтому и вопрос возник.

предполагаю, что это должно быть в ibis модели.

также есть такой параметр как speed grade (или как-то так, сейчас нет гиперлинкса под рукой) микросхем и он влияет на результаты симуляции - времена (вычисление бюджета) и fail/pass соответственно

также есть такой параметр как speed grade (или как-то так, сейчас нет гиперлинкса под рукой) микросхем и он влияет на результаты симуляции - времена (вычисление бюджета) и fail/pass соответственно

Нет, в ИБИСе непосредственных данных о pin delay нет.

А по поводу speed grade могу ошибаться, но там скорее речь о внутренних скоростных возможностях чипа идет(FPGA, памяти). Но на модель буфера(драйвера) оно не влияет. Да и нет в списке моделей поделенных на разные скорости, только тип буфера/драйвера, напряжение, токовые возможности, сопротивления... Еще slew rate есть, но там без вариантов - для DDR3 только fast может быть.

А по поводу speed grade могу ошибаться, но там скорее речь о внутренних скоростных возможностях чипа идет(FPGA, памяти). Но на модель буфера(драйвера) оно не влияет. Да и нет в списке моделей поделенных на разные скорости, только тип буфера/драйвера, напряжение, токовые возможности, сопротивления... Еще slew rate есть, но там без вариантов - для DDR3 только fast может быть.

Нет, в ИБИСе непосредственных данных о pin delay нет.

А по поводу speed grade могу ошибаться, но там скорее речь о внутренних скоростных возможностях чипа идет(FPGA, памяти). Но на модель буфера(драйвера) оно не влияет. Да и нет в списке моделей поделенных на разные скорости, только тип буфера/драйвера, напряжение, токовые возможности, сопротивления... Еще slew rate есть, но там без вариантов - для DDR3 только fast может быть.

А по поводу speed grade могу ошибаться, но там скорее речь о внутренних скоростных возможностях чипа идет(FPGA, памяти). Но на модель буфера(драйвера) оно не влияет. Да и нет в списке моделей поделенных на разные скорости, только тип буфера/драйвера, напряжение, токовые возможности, сопротивления... Еще slew rate есть, но там без вариантов - для DDR3 только fast может быть.

Разве недостаточно по DDR3/3L/4... в JEDEC Standard описано? Мне как то хватает. Или у вас DDR3 не по стандарту выполнен? Вряд ли.

По требованиям Альтеры все сделано. И оно работает и тесты проходит, в смысле измерения сделаны и они Pass. А вот DDR3 batch утверждает, что это Bad signal

Не знаю, может быть *.v файлы нужно править под наш контроллер, чтобы анализатор правильно все проверил.

Не знаю, может быть *.v файлы нужно править под наш контроллер, чтобы анализатор правильно все проверил.

Нет, в ИБИСе непосредственных данных о pin delay нет.

А по поводу speed grade могу ошибаться, но там скорее речь о внутренних скоростных возможностях чипа идет(FPGA, памяти).

А по поводу speed grade могу ошибаться, но там скорее речь о внутренних скоростных возможностях чипа идет(FPGA, памяти).

ну а разве это не является pin delay-ем? то есть имеем три задержки fast, typ, slow (если они не в модели, то значит их знает сам гиперлинкс - вариантов не много и они стандартизированы) в зависимости от условий (угла) берем нужную задержку и вычитаем из бюджета - я так понимаю, что смысл этого ddr batch mode в том и состоит, что результаты симуляции сравниваются с бюджетом, учитывающим задержки в микросхемах, автоматически, а не пользователем вручную на калькуляторе

знать задержки может для микросхем памяти, а контроллер ПЛИС/процессор - видимо нужно как-то добавлять, тут я еще не разобрался

Видел я этот файл и его содержимое... вот только данные в нем не особо соотносятся с тем, что есть в плате. Собственно поэтому и вопрос возник.

1. Почитайте внимательно документацию, там явно написано что стандартный файл формируется софтом самостоятельно и перезаписывается при каждом старте, но если создать файл с собственным именем, то задержки будут браться из него и он не перезаписывается.

2. Я не сильный спец. по SI, но мыслим логически

- как правило IBIS файл создается на основе измерений реальной микросхемы, т.е. содержащиеся там значения получаются непосредственно на выводах корпуса микросхемы, соответственно уже учитывают внутреннюю задержку проводков от кристалла до вывода корпуса.

- в IBIS есть также есть значения R\L\C для каждого пина, что тоже, насколько я понимаю, должно формировать некоторые задержки фронтов.

Нажмите для просмотра прикрепленного файла

3. В конце концов можно перейти в LineSim и добавить передающую линию (Simple) введя нужные параметры задержки.

По требованиям Альтеры все сделано. И оно работает и тесты проходит, в смысле измерения сделаны и они Pass. А вот DDR3 batch утверждает, что это Bad signal

Если считает это проблема в Hyperlynx DDR batch simulation, и у вас лицензия то должны ответить в течении 3 дней. Все может быть просто, в Hyperlynx в той версии у вас, не выполнил в полном объёме JEDEC.

...

- в IBIS есть также есть значения R\L\C для каждого пина, что тоже, насколько я понимаю, должно формировать некоторые задержки фронтов.

- в IBIS есть также есть значения R\L\C для каждого пина, что тоже, насколько я понимаю, должно формировать некоторые задержки фронтов.

да, эта задержка вычисляется как корень квадратный из С*L.

ну а разве это не является pin delay-ем? то есть имеем три задержки fast, typ, slow (если они не в модели, то значит их знает сам гиперлинкс - вариантов не много и они стандартизированы) в зависимости от условий (угла) берем нужную задержку и вычитаем из бюджета - я так понимаю, что смысл этого ddr batch mode в том и состоит, что результаты симуляции сравниваются с бюджетом, учитывающим задержки в микросхемах, автоматически, а не пользователем вручную на калькуляторе

Нет, это именно slew rate, т.е. скоростные возможности драйвера, время нарастания/спада сигнала. К доп. задержке на конкретном пине отношения не имеющие.

fill

1. Идею с DDR3Delays_autogenerated.txt я понял, но разбираться нет смысла - идея была попробовать этот автомат "как есть". Если нужно "допиливать", то обойдемся, на это в скедуле время не предусмотрено.

2. Да, по правильному IBIS должен генериться Quartus-ом(в данном конкретном случае) как результат проекта. Но проект этот делается не нами, а самим клиентом(мы как hardware ODM в данном случае выступаем), поэтому целевого IBIS-a у меня нет. Я его вручную составил, прописав таблицу пинов и собрав драйвера к ним. Поэтому же нет RLC-параметров для каждого пина, а есть только typical для этого корпуса. Но Pin Delay прописаны в проекте PCB, и у меня такое впечатление, что они не видны в HL, но учитываются в зависимости от используемого симулятора - при просмотре сигналов простым скопом видна отчетливая разница между данными на приемнике(т.е. просчитывается только задержка на трассе), а вот в EZwave сигналы собраны как и положено, с расбросом менее 10пс (т.е. просчитана сумма трасса + Pin Delay). Ну и в EZwave я смотрю сигналы на die, чего нет в скопе(да, в нем тоже можно выбирать тип симулятора, но специально этого не делал используя настройки по умолчанию).

3. Согласен, можно много чего помоделить, и даже пощупал такую возможность, но времени на это уходит порядочно, по крайней мере поначалу.

Идея была посмотреть на возможности Hyperlynx, время на это необходимое и подумать о его дальнейшем использовании. Так что офф. саппорт на данный момент в расчет не берется...

да, эта задержка вычисляется как корень квадратный из С*L.

В общем случае из этих параметров можно посчитать импеданс линии, а вот длину не получится - не хватает данных.

...

Идея была посмотреть на возможности Hyperlynx, время на это необходимое и подумать о его дальнейшем использовании. Так что офф. саппорт на данный момент в расчет не берется...

В общем случае из этих параметров можно посчитать импеданс линии, а вот длину не получится - не хватает данных.

Идея была посмотреть на возможности Hyperlynx, время на это необходимое и подумать о его дальнейшем использовании. Так что офф. саппорт на данный момент в расчет не берется...

В общем случае из этих параметров можно посчитать импеданс линии, а вот длину не получится - не хватает данных.

может я вашу мысль потерял уже... Какую длину выхотите посчитать? Если при выравнивании, то у FPGA/SoC от кристала до шарика все дает производитель. Для чипов памяти DDR3* этого не требуется, у них все приведено к шарикам по нулям. А что еще нужно?

Не вдаваясь в комментирование основного вопроса(в теме начисто отсутствуют люди которые серьезно занимаются и понимают софт под SI  ), хочу обратиться к Uree- насколько я могу понять, вы работаете в аллегро и референсы у вас интеловские/альтеровские. Это значит что имеет большой смысл взглянуть на HFSS/Siwave- там прямой порт на уровне .brd плюс интерфейс такого уровня проработки что как минимум основу можно понять методом тыка. Что характерно, там удобно сделано все- и SI и PI и тепло.

), хочу обратиться к Uree- насколько я могу понять, вы работаете в аллегро и референсы у вас интеловские/альтеровские. Это значит что имеет большой смысл взглянуть на HFSS/Siwave- там прямой порт на уровне .brd плюс интерфейс такого уровня проработки что как минимум основу можно понять методом тыка. Что характерно, там удобно сделано все- и SI и PI и тепло.

Можно глянуть в сторону ADS, но как по мне он более полезен для профессий типа Sr. Backplane Architect и Principal SI Engineer, причем более на "верхнем"(системном) уровне проектирования.

Для остальных, на всякий случай хороший документ

Можно глянуть в сторону ADS, но как по мне он более полезен для профессий типа Sr. Backplane Architect и Principal SI Engineer, причем более на "верхнем"(системном) уровне проектирования.

Для остальных, на всякий случай хороший документ

Будет время - буду смотреть и на другой софт. Пока начал с HL, потому как уже имел с ним дело раньше, ну и хотелось посмотреть, что он может сейчас.

А с документа этого вчера и начинал поиск инфы о подробностях IBIS моделей.

А с документа этого вчера и начинал поиск инфы о подробностях IBIS моделей.

Цитата

В общем случае из этих параметров можно посчитать импеданс линии, а вот длину не получится - не хватает данных.

Так длину учитывать это вообще бессмысленно. Посмотрите на пример Нажмите для просмотра прикрепленного файла

длина одинаковая, но задержка то разная. Причем если по трассам платы задержку можно посчитать в анализаторе, то во что превращается длина внутри корпуса с точки зрения задержки знает только производитель. Ну добавили вы 10мм как длину пина и что? Как это отразится сточки зрения конкретного времени прихода сигнала на приемник?

Цитата

Так длину учитывать это вообще бессмысленно.

+

Цитата

Ну добавили вы 10мм как длину пина и что? Как это отразится сточки зрения конкретного времени прихода сигнала на приемник?

Ну ясно

Цитата

А с документа этого вчера и начинал поиск инфы о подробностях IBIS моделей.

Так я потому и написал для "остальных", да и вконце концов с тем же документом в результатах поиска идут намеки

Так в том и дело, что на один пин добавляется 10мм, а на другой 20мм. В итоге 10пс разницы в дизайне превращаются в 70-80пс разницы в Hyperlynx-e.

Ладно, может позже будет время-возможность поковырять этот вопрос. Сейчас поезд уже ушел

Ладно, может позже будет время-возможность поковырять этот вопрос. Сейчас поезд уже ушел

Раз уж затронули тему. Касательно DDR Wizard и адекватности его расчетов у меня вопрос попроще. Насколько я понимаю при моделировании этот инструмент не учитывает возвратные токи и реальные шэйпы референсных слоев, т.е. по сути любой полигон он считает идеальным и неразрывным. Как в таком случае можно полагаться на его результаты? Поправьте, если не прав.

Ну я бы сказал, что это не его задача. Если дизайнер не обеспечил целостности полигонов земли/питания интерфейса, то к машинке претензий быть не должно. Ее задача проверить тайминги интерфейса как целого, а не подробный анализ качества сигнала в каждой из линий.

Да нет, это как раз его(софта) задача- особенно если речь идет о локализуемых/нелокализуемых структурах. Все дело в том, что любой общий пакет "для электродинамики" рвет и дерет абсолютно любой "симулятор для плат". Хотя бы потому что второе максимум может являться подмножеством первого, но разумеется никак наоборот  . Кроме того, как по вашему тогда люди моделят структуры с defected ground structures?

. Кроме того, как по вашему тогда люди моделят структуры с defected ground structures?

Нет ничего удивительного в том что в абсолютно подавляющем большинстве случаев вакансии типа SI Engineer непременно содержат слова HFSS и ADS, и где то там, очень редко, где-то в secondary может промелькнуть софт для платок.

Ну и насчет возвратных токов, опор и пр. очень рекомендую посмотреть презентации Юрия Шлепнева,(а заодно и Simberian)- который к слов как раз принимал участие в разработке гиперлинкса(мягко говоря). Очень занятно и полезно Как правило разрыв седалища у гур начинается с этих двух бумаг, раз два. Но ясное дело, там и про опоры и есть и пр.

Как правило разрыв седалища у гур начинается с этих двух бумаг, раз два. Но ясное дело, там и про опоры и есть и пр.

Нет ничего удивительного в том что в абсолютно подавляющем большинстве случаев вакансии типа SI Engineer непременно содержат слова HFSS и ADS, и где то там, очень редко, где-то в secondary может промелькнуть софт для платок.

Ну и насчет возвратных токов, опор и пр. очень рекомендую посмотреть презентации Юрия Шлепнева,(а заодно и Simberian)- который к слов как раз принимал участие в разработке гиперлинкса(мягко говоря). Очень занятно и полезно

Софта Hyperlynx - да, его задача. Функции DDR Batch Simulation - нет, у нее ограниченная функциональность в части именно SI и расширенная в части таймингов сигналов и зависимостей между ними.

Так что если закладываем разрывы плэйнов в этом интерфейсе, то надо брать линии на которых ожидаем проблемы и моделировать более глубоко, с учетом всего, что можно.

По крайней мере таким выглядит подход к реализации DDR Batch Simulation в Hyperlynx.

Так что если закладываем разрывы плэйнов в этом интерфейсе, то надо брать линии на которых ожидаем проблемы и моделировать более глубоко, с учетом всего, что можно.

По крайней мере таким выглядит подход к реализации DDR Batch Simulation в Hyperlynx.

Ну я бы сказал, что это не его задача. Если дизайнер не обеспечил целостности полигонов земли/питания интерфейса, то к машинке претензий быть не должно. Ее задача проверить тайминги интерфейса как целого, а не подробный анализ качества сигнала в каждой из линий.

Так ведь "целостность полигонов земли/питания интерфейса" повлияет в тч и на тайминги. Hyperlynx - это 2D солвер по сути, т.е. имхо необходимо делать оговорку и понимать, что его DDR Wizard - не панацея и слепо на него полагаться нельзя. При откровенно плохом дизайне результат проверки таймингов этим инструментом будет неадекватный. Кроме того, для корректного моделирования нужно еще и кастомную тайминг-модель для контроллера создавать, не всегда это тривиальная задача.

Цитата

Ну и насчет возвратных токов, опор и пр. очень рекомендую посмотреть презентации Юрия Шлепнева,(а заодно и Simberian)

Да, видел его сайт со множеством демо о моделировании 3D-структур. Это конечно софт другого уровня (если сравнивать с HL).

Цитата

Как правило разрыв седалища у гур начинается с этих двух бумаг, раз два.

Хм, а от чего конкретно "разрывает"? Вроде по делу все изложено.

Цитата

Так ведь "целостность полигонов земли/питания интерфейса" повлияет в тч и на тайминги.

Именно- в связи с чем просмотр так сказать "таймингов в вакууме"(без нарушения правил форума не знаю как лучше сказать

Цитата

При откровенно плохом дизайне результат проверки таймингов этим инструментом будет неадекватный.

Именно- причем бывают гораздо более серьезные причины, например PI. В симуляции на SI это разумеется никто не увидит, другое дело когда плата запаяна

Цитата

Да, видел его сайт со множеством демо о моделировании 3D-структур. Это конечно софт другого уровня (если сравнивать с HL).

Так и есть.

Цитата

Хм, а от чего конкретно "разрывает"? Вроде по делу все изложено.

По делу, да- но тут есть два лагеря:

- т.н. псб дизайнеры и рф инженеры которые всерьез утверждают что нельзя так угол резать как в случае chamfered path, и обязательно надо 45гр. Про величину dist среди них ясное дело никто не говорит.

- остальные гуру которые в абсолютно любом дизайне при абсолютно любой скорости(как правило ниже чем в презентации

У вас же вопрос возникает по причине того что вы явно не из таких, а судя по всему вполне здоровый человек

Цитата

- т.н. псб дизайнеры и рф инженеры которые всерьез утверждают что нельзя так угол резать как в случае chamfered path, и обязательно надо 45гр

Помню, как сам учил именно так делать. Но там было всё проще - это был самый простой штатный способ фаску срезать. Отдельных "галочек" и других настроек в инструменте не было.

Цитата

- остальные гуру которые в абсолютно любом дизайне при абсолютно любой скорости(как правило ниже чем в презентации biggrin.gif ) втирают за опасность 90гр поворотов.

Не могу судить, но мне кажется это уже особо никого в заблуждение не вводит. Про углы 90-градусов даже в литературе попроще (а-ля Lee Ritchey "Right the first time") написано, что для большниства реальных приложений и скоростей они опасности не представляют. Другое дело, что под 45-градусов трассировать эстетически приятнее и удобнее))

Цитата

Именно- причем бывают гораздо более серьезные причины, например PI. В симуляции на SI это разумеется никто не увидит, другое дело когда плата запаяна

Представители Cadence утверждают, что их Sigrity способен учитывать все эти эффекты при моделировании DDR. Сам никогда не пользовался - не знаю.

Цитата

Помню, как сам учил именно так делать.

Дык оно и понятно- chamfered path незаменимый инструмент в тех ситуациях когда надо повернуть RF трассу в ограниченном(да и не только) пространстве. Просто речь шла о том, что некоторые гуру говорят будто это "ужасно портит сигнал таким большим срезом, надо резать меньше"

Цитата

Не могу судить, но мне кажется это уже особо никого в заблуждение не вводит.

Вы чудовищно переоцениваете людей

Цитата

Другое дело, что под 45-градусов трассировать эстетически приятнее и удобнее))

Разумеется- хотя конечно есть и случае где удобнее дугами, а если SIP то вполне могут быть и настоящие 90гр.

Раз уж затронули тему. Касательно DDR Wizard и адекватности его расчетов у меня вопрос попроще. Насколько я понимаю при моделировании этот инструмент не учитывает возвратные токи и реальные шэйпы референсных слоев, т.е. по сути любой полигон он считает идеальным и неразрывным. Как в таком случае можно полагаться на его результаты? Поправьте, если не прав.

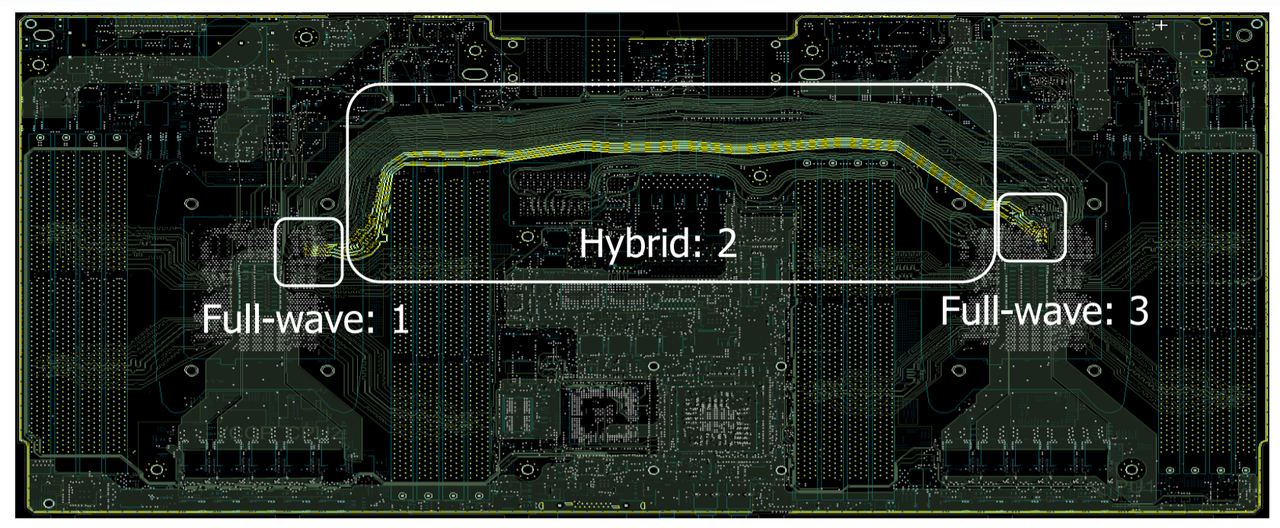

1.Вообще-то полигоны уже учитываются.

2. Если нужна повышенная точность, то:

а) выбирается область для передачи в FullWave Solver

Нажмите для просмотра прикрепленного файла

затем полученная модель поведения данной области может использоваться при общем моделировании цепей,

кроме того есть алгоритм поиска подобных областей, т.е. к ним будет применена такая же, уже рассчитанная ранее модель поведения

б) можно загнать в FullWave Solver или Hybryd Solver хоть всю плату, но это будет более накладно по времени и ресурсам

Нажмите для просмотра прикрепленного файла

Цитата

Если нужна повышенная точность, то:

А нет ли ссылки на полную презентацию? Хотя бы посмотреть на пример, где потребовались HPC и указанное время.

А нет ли ссылки на полную презентацию? Хотя бы посмотреть на пример, где потребовались HPC и указанное время.

тыц

Премного благодарен, любопытный документ- если не возражаете позвольте поинтересоваться:

- что означает "Time Per Frequency", как оно считается и что тогда "Total time"

- надо отметить что очень хороший и правильный пример взят(из мира серверов), но как определены области под каждый совлер/метод и что там происходит на границе?

Хорошо что метод солвера приведен, интересно почитать.

Софта Hyperlynx - да, его задача. Функции DDR Batch Simulation - нет, у нее ограниченная функциональность в части именно SI и расширенная в части таймингов сигналов и зависимостей между ними.

Так что если закладываем разрывы плэйнов в этом интерфейсе, то надо брать линии на которых ожидаем проблемы и моделировать более глубоко, с учетом всего, что можно.

По крайней мере таким выглядит подход к реализации DDR Batch Simulation в Hyperlynx.

Так что если закладываем разрывы плэйнов в этом интерфейсе, то надо брать линии на которых ожидаем проблемы и моделировать более глубоко, с учетом всего, что можно.

По крайней мере таким выглядит подход к реализации DDR Batch Simulation в Hyperlynx.

Согласен с выше сказанным.

HyperLynx это набор инструментов который можно использовать на разных стадиях решения задачи:

1. В HL DRC можно легко и быстро найти возможные проблемные области

2. В HL Advance Solvers можно провести детальный анализ этих областей для установления степени их проблемности и получения модели их поведения для применения в общем моделировании

3. В HL PI провести анализ плейнов питаний, падения напряжения, шумов, развязки, анализ возвратных токов.

4. Ну и наконец в HL SI провести окончательное моделирование\анализ всех цепей платы. В том числе можно провести и смешанный анализ SI\PI\Thermal.

Премного благодарен, любопытный документ- если не возражаете позвольте поинтересоваться:

- что означает "Time Per Frequency", как оно считается и что тогда "Total time"

- надо отметить что очень хороший и правильный пример взят(из мира серверов), но как определены области под каждый совлер/метод и что там происходит на границе?

Хорошо что метод солвера приведен, интересно почитать.

- что означает "Time Per Frequency", как оно считается и что тогда "Total time"

- надо отметить что очень хороший и правильный пример взят(из мира серверов), но как определены области под каждый совлер/метод и что там происходит на границе?

Хорошо что метод солвера приведен, интересно почитать.

В данном случае, насколько я понимаю, время и потребляемая память приведены были просто для наглядного отображения относительной разницы между двумя подходами решения задачи - считать все в Full или разделить расчет на части, там где необходима повышенная точность в Full, а где ее можно уменьшить без существенных искажений в Hybdrid.

Цитата

1.Вообще-то полигоны уже учитываются.

Цитата

а) выбирается область для передачи в FullWave Solver

Да, я видел этот прикрученный 3D-редактор. Но насколько я понял, этот инструмент ориентирован в первую чередь на SERDES интерфейсы и неоднородности в их трассировке - не на обширные параллельные интерфейсы а-ля DDR.

Да, я видел этот прикрученный 3D-редактор. Но насколько я понял, этот инструмент ориентирован в первую чередь на SERDES интерфейсы и неоднородности в их трассировке - не на обширные параллельные интерфейсы а-ля DDR.

А теперь посмотрите на слайд от Сигрити и убедитесь в точно таком же пути решения задачи. Не выбирают всю плату со всеми цепями для точного моделирования.

Нажмите для просмотра прикрепленного файла

И поймите наконец, что чтобы получить решение в реальные по времени сроки (и на обычном железе) приходится пока использовать смешанные расчеты. И не важно SERDES это или DDR.

Да я вобщем-то с этим и не спорю, мы же конкретно визард обсуждали.

По поводу DDR - есть вот такое рекламное видео от Sigrity. Если тут есть те, кто использовал этот инструмент в реальных условиях - было бы интересно услышать впечатления.

По поводу DDR - есть вот такое рекламное видео от Sigrity. Если тут есть те, кто использовал этот инструмент в реальных условиях - было бы интересно услышать впечатления.

Да я вобщем-то с этим и не спорю, мы же конкретно визард обсуждали.

По поводу DDR - есть вот такое рекламное видео от Sigrity. Если тут есть те, кто использовал этот инструмент в реальных условиях - было бы интересно услышать впечатления.

По поводу DDR - есть вот такое рекламное видео от Sigrity. Если тут есть те, кто использовал этот инструмент в реальных условиях - было бы интересно услышать впечатления.

Ну так в этом видео сразу заявляют что счет идет в Hybrid симуляторе использующем FDTD, а не Full.

Нажмите для просмотра прикрепленного файла

А при извлечении моделей вообще фигурирует "ideal PDN", т.е. рассматривается относительно идеального плейн.

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.