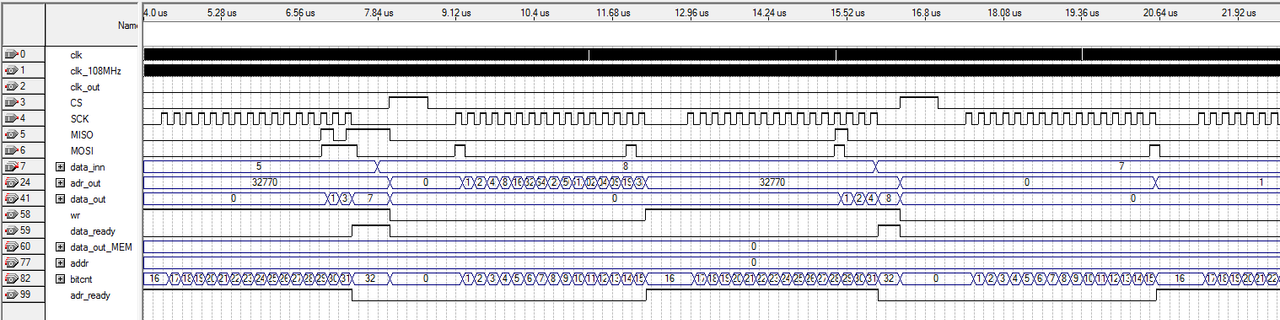

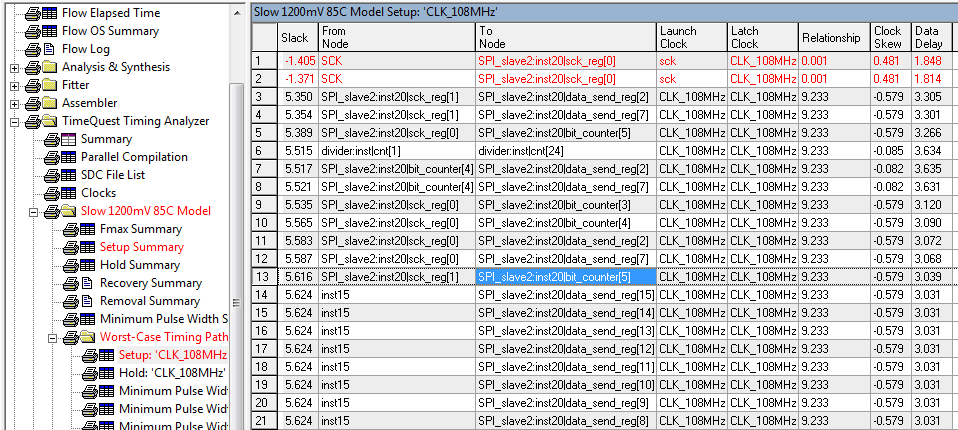

Прошу меня сильно не пинать, Verilog начал изучать совсем недавно. Модуль не хочет работать ни в симуляторе, ни в железе( Код программы, RTL и скрин симуляции прилагаются, могу скинуть исходный код. Проект собирается в Quartus II 9.1, ПЛИС cyclone III.

Код:

Код

module MEM_CONTROLLER

(

input clk, cs,

input [15:0] data_in,

output [15:0] data_out,

output reg [3:0] addr,

output wr

);

reg [15:0] data_out_reg;

reg [2:0] state;

reg b_write; //Если 1 - то записываем данные

reg wr_reg;

parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3, S4 = 4, S5 = 5, S6 = 6;

always @ (posedge clk)

begin

case (state)

//---------------------------

// Ждем спад 1 cs

//---------------------------

S0:

if (cs==0)

state <= S1;

else

state <= S0;

//---------------------------

// Фронт 1 cs, заносим адрес в регистр addr

// Если старший бит = 1 - то записываем данные в RAM,

// иначе - читаем

//---------------------------

S1:

if (cs)

begin

case (data_in[2:0])

3'b001 : addr <= 4'b0001;

3'b010 : addr <= 4'b0010;

3'b011 : addr <= 4'b0100;

3'b100 : addr <= 4'b1000;

default : addr <= 4'b0000;

endcase

b_write <= data_in[15]? 1'b1:1'b0;

state <= S2;

end

else

state <= S1;

//---------------------------

// Ждем спад 2 cs

//---------------------------

S2:

if (cs==0)

state <= S3;

else

state <= S2;

//---------------------------

// Ждем фронт 2 cs

//---------------------------

S3:

if (cs)

if (b_write)

begin

data_out_reg[15:0] <= data_in[15:0];

state <= S4;

end

else

state <= S0; //Читаем данные (выводим их на data_out)

else

state <= S3;

//---------------------------

// Ждем установки addr

// Устанавливаем wr = 1

//---------------------------

S4:

begin

wr_reg <= 1;

state <= S5;

end

//---------------------------

// Сбрасываем wr

//---------------------------

S5:

begin

wr_reg <= 0;

state <= S0;

end

//---------------------------

endcase

end

assign data_out[15:0] = data_out_reg[15:0];

assign wr = wr_reg;

endmodule

(

input clk, cs,

input [15:0] data_in,

output [15:0] data_out,

output reg [3:0] addr,

output wr

);

reg [15:0] data_out_reg;

reg [2:0] state;

reg b_write; //Если 1 - то записываем данные

reg wr_reg;

parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3, S4 = 4, S5 = 5, S6 = 6;

always @ (posedge clk)

begin

case (state)

//---------------------------

// Ждем спад 1 cs

//---------------------------

S0:

if (cs==0)

state <= S1;

else

state <= S0;

//---------------------------

// Фронт 1 cs, заносим адрес в регистр addr

// Если старший бит = 1 - то записываем данные в RAM,

// иначе - читаем

//---------------------------

S1:

if (cs)

begin

case (data_in[2:0])

3'b001 : addr <= 4'b0001;

3'b010 : addr <= 4'b0010;

3'b011 : addr <= 4'b0100;

3'b100 : addr <= 4'b1000;

default : addr <= 4'b0000;

endcase

b_write <= data_in[15]? 1'b1:1'b0;

state <= S2;

end

else

state <= S1;

//---------------------------

// Ждем спад 2 cs

//---------------------------

S2:

if (cs==0)

state <= S3;

else

state <= S2;

//---------------------------

// Ждем фронт 2 cs

//---------------------------

S3:

if (cs)

if (b_write)

begin

data_out_reg[15:0] <= data_in[15:0];

state <= S4;

end

else

state <= S0; //Читаем данные (выводим их на data_out)

else

state <= S3;

//---------------------------

// Ждем установки addr

// Устанавливаем wr = 1

//---------------------------

S4:

begin

wr_reg <= 1;

state <= S5;

end

//---------------------------

// Сбрасываем wr

//---------------------------

S5:

begin

wr_reg <= 0;

state <= S0;

end

//---------------------------

endcase

end

assign data_out[15:0] = data_out_reg[15:0];

assign wr = wr_reg;

endmodule

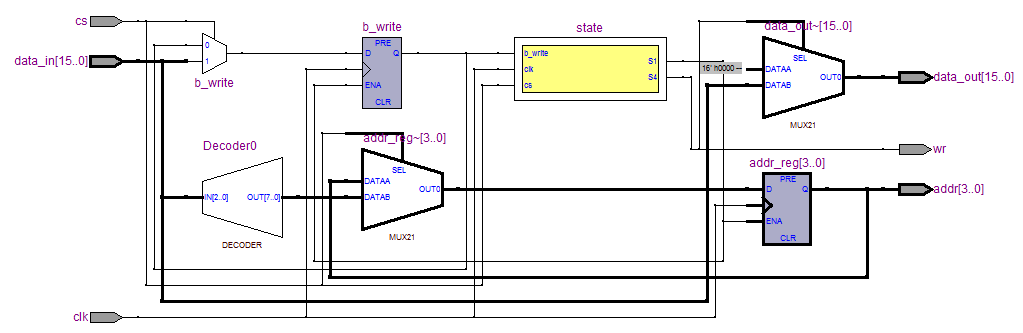

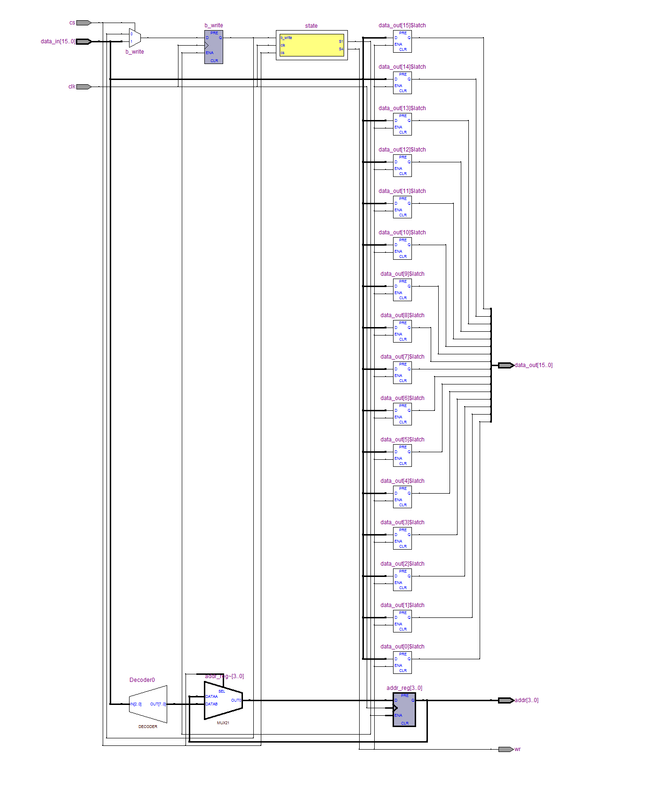

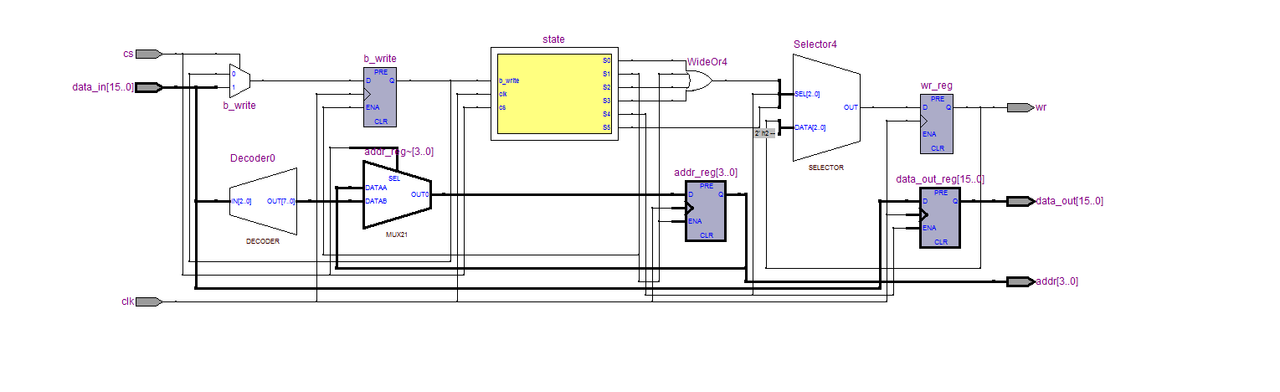

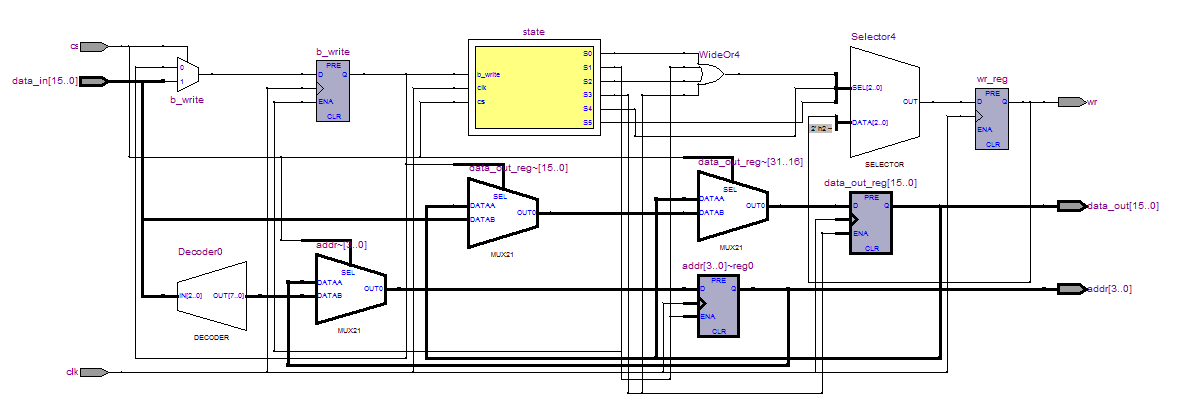

RTL:

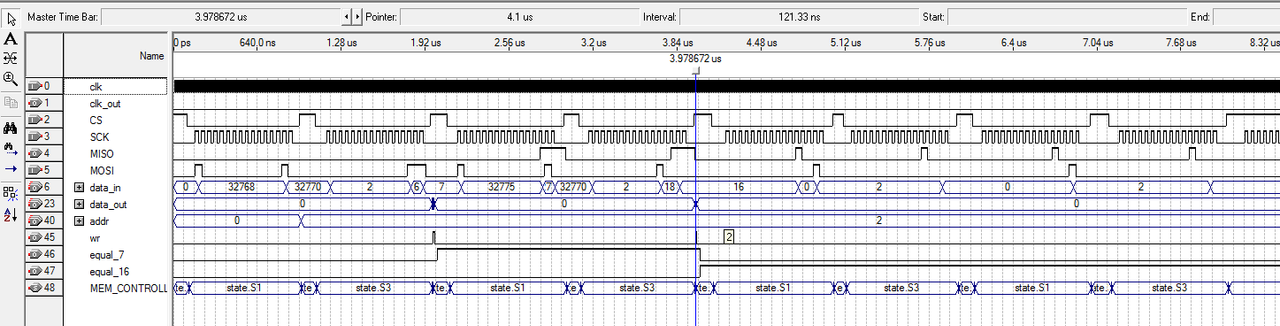

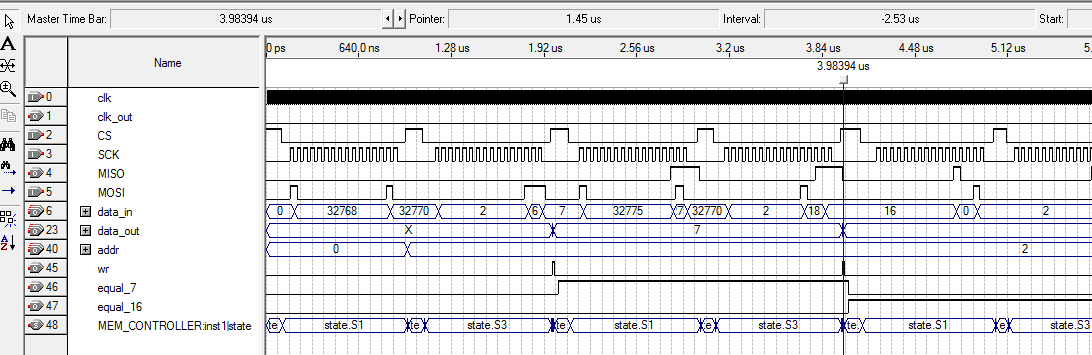

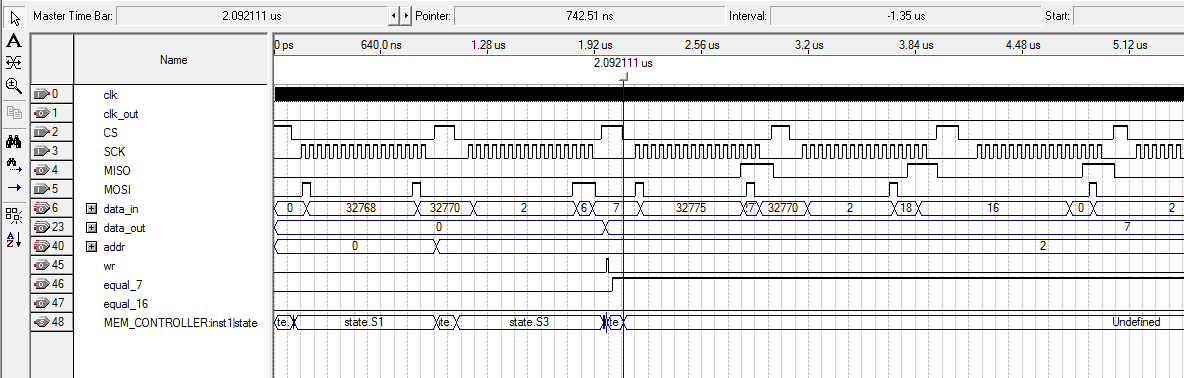

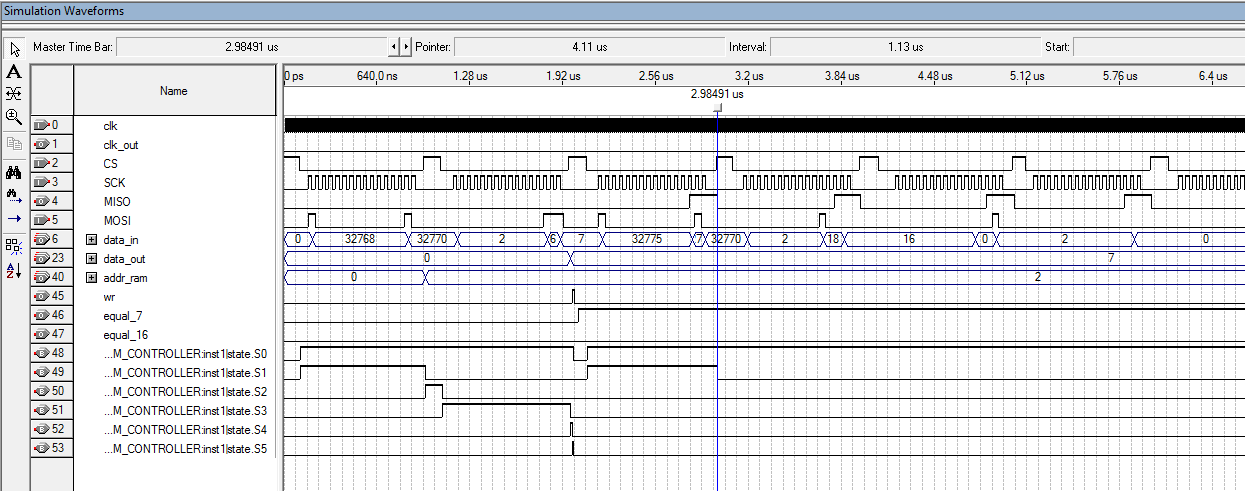

Waveform:

В симулиции по логике там где стоит маркер должен происходить переход в состояние S2, но ничего не происходит(