Изучаю TimeQuest, есть несколько вопросов.

Есть модуль:

Код

module adc

(

input clk,

input clk_32MHz,

input ena,

input [7:0]data,

output reg alarm

);

reg [1:0] state;

parameter s0=0, s1=1, s2=2, s3=3;

reg [7:0] data_ch1[2:0];

reg [1:0] clk_32MHz_reg;

initial

begin

state = 0;

data_ch1[0] = 8'd0;

data_ch1[1] = 8'd0;

data_ch1[2] = 8'd0;

clk_32MHz_reg = 2'b00;

alarm = 0;

end

wire clk_32MHz_risingEdge;

wire clk_32MHz_fallingEdge;

//---------------------------------

// Select front and fall moment

//---------------------------------

always @(posedge clk)

begin

clk_32MHz_reg <= {clk_32MHz_reg[0], clk_32MHz};

end

assign clk_32MHz_risingEdge = (clk_32MHz_reg == 2'b01);

assign clk_32MHz_fallingEdge = (clk_32MHz_reg == 2'b10);

//----------------------------------------

always @ (posedge clk)

begin

if (ena)

begin

case (state)

//============================

//Channel process

//============================

s0:

begin

state <= clk_32MHz_risingEdge? s1:s0;

end

//----------------------------

s1:

begin

if (clk_32MHz_fallingEdge)

begin

data_ch1[0] <= data;

state <= s2;

end

else

state <= s1;

end

//----------------------------

s2:

begin

if ((data_ch1[0] > data_ch1[1]) && (data_ch1[1] > data_ch1[2]))

alarm = 1;

else

alarm = 0;

state <= s3;

end

//----------------------------

s3:

begin

data_ch1[2] <= data_ch1[1];

data_ch1[1] <= data_ch1[0];

state <= s0;

end

//----------------------------

default:

begin

alarm <= 0;

state <= s0;

end

//----------------------------

endcase

end

else

begin

alarm <= 0;

state <= s0;

end

end

//----------------------------------------

endmodule

(

input clk,

input clk_32MHz,

input ena,

input [7:0]data,

output reg alarm

);

reg [1:0] state;

parameter s0=0, s1=1, s2=2, s3=3;

reg [7:0] data_ch1[2:0];

reg [1:0] clk_32MHz_reg;

initial

begin

state = 0;

data_ch1[0] = 8'd0;

data_ch1[1] = 8'd0;

data_ch1[2] = 8'd0;

clk_32MHz_reg = 2'b00;

alarm = 0;

end

wire clk_32MHz_risingEdge;

wire clk_32MHz_fallingEdge;

//---------------------------------

// Select front and fall moment

//---------------------------------

always @(posedge clk)

begin

clk_32MHz_reg <= {clk_32MHz_reg[0], clk_32MHz};

end

assign clk_32MHz_risingEdge = (clk_32MHz_reg == 2'b01);

assign clk_32MHz_fallingEdge = (clk_32MHz_reg == 2'b10);

//----------------------------------------

always @ (posedge clk)

begin

if (ena)

begin

case (state)

//============================

//Channel process

//============================

s0:

begin

state <= clk_32MHz_risingEdge? s1:s0;

end

//----------------------------

s1:

begin

if (clk_32MHz_fallingEdge)

begin

data_ch1[0] <= data;

state <= s2;

end

else

state <= s1;

end

//----------------------------

s2:

begin

if ((data_ch1[0] > data_ch1[1]) && (data_ch1[1] > data_ch1[2]))

alarm = 1;

else

alarm = 0;

state <= s3;

end

//----------------------------

s3:

begin

data_ch1[2] <= data_ch1[1];

data_ch1[1] <= data_ch1[0];

state <= s0;

end

//----------------------------

default:

begin

alarm <= 0;

state <= s0;

end

//----------------------------

endcase

end

else

begin

alarm <= 0;

state <= s0;

end

end

//----------------------------------------

endmodule

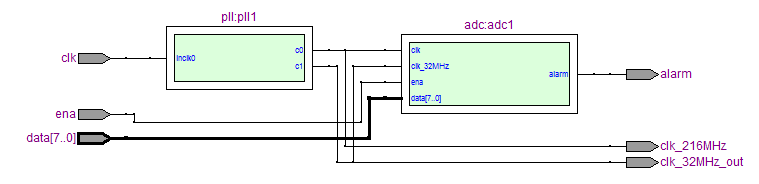

И есть pll с входной частотой 36МГц (clk) и двумя выходными частотами: 216 (с0) и 32МГц (с1). В общем виде это выглядит вот так:

В двух словах: сигнал с выхода c1 pll (32MГц) поступает на детектор фронта/спада сигнала модуля, тактовая частота которого 216Мгц.

Написал вот такой констрейн:

Код

derive_clock_uncertainty

create_clock -name clk -period 36.1MHz [get_ports {clk}]

create_generated_clock -name clk_216MHz -source [get_ports {clk}] -multiply_by 6 [get_nets {pll1|altpll_component|auto_generated|wire_pll1_clk[0]}]

create_generated_clock -name clk_32MHz -source [get_ports {clk}] -divide_by 17 -multiply_by 15 [get_nets {pll1|altpll_component|auto_generated|wire_pll1_clk[1]}]

create_clock -name clk -period 36.1MHz [get_ports {clk}]

create_generated_clock -name clk_216MHz -source [get_ports {clk}] -multiply_by 6 [get_nets {pll1|altpll_component|auto_generated|wire_pll1_clk[0]}]

create_generated_clock -name clk_32MHz -source [get_ports {clk}] -divide_by 17 -multiply_by 15 [get_nets {pll1|altpll_component|auto_generated|wire_pll1_clk[1]}]

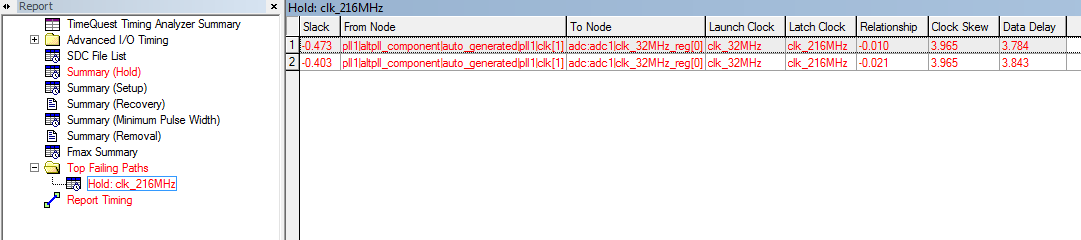

После компиляции TimeQuest выдает слаки:

Прошу знающих людей объяснить на что ругается TimeQuest.

Заранее спасибо!