Полная версия этой страницы: Help the noob with Verilog

Форум разработчиков электроники ELECTRONIX.ru > Программируемая логика ПЛИС (FPGA,CPLD, PLD) > Языки проектирования на ПЛИС (FPGA)

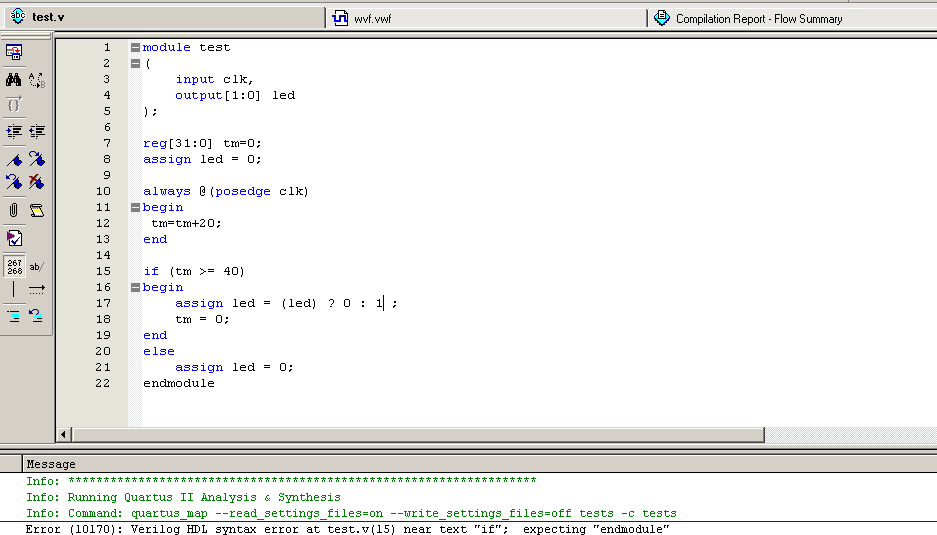

у вас комбинация if - else сама по себе болтается, её надо в always сунуть , а assign вытащить из неё.

з.ы.

правда что вы хотите от led-a я так и не понял.

з.ы.

правда что вы хотите от led-a я так и не понял.

у вас комбинация if - else сама по себе болтается, её надо в always сунуть , а assign вытащить из неё.

з.ы.

правда что вы хотите от led-a я так и не понял.

з.ы.

правда что вы хотите от led-a я так и не понял.

Каждые 40 нс меняется состояние led. То есть это имитация светодиода, который горит в течение 40 нс каждые 40 нс.

За совет - спасибо. Не знал, что нельзя вне блока always операторы совать

это имитация светодиода, который горит в течение 40 нс каждые 40 нс.

если лед будет гореть 40 нс, каждые 40 нс - то он будет гореть непрерывно.

Но я вас понял - вы на самом деле хотите чтобы у вас лед мигал со скважностью 2.

Код

reg led_reg=0;

always @(posedge clk)

if (tm!=40) tm<=tm+1;

else

begin

tm<=0;

led_reg<=~led_reg;

end

assign led = led_reg;

always @(posedge clk)

if (tm!=40) tm<=tm+1;

else

begin

tm<=0;

led_reg<=~led_reg;

end

assign led = led_reg;

Симулятора у меня под рукой нет - надеюсь не накосячил.

Само - собой , тактовая 1 ГГц.

Можно оффтоп?

Есть какие-нибудь наработки для визуализации всего этого дела? Виртуальная эмуляция платы например, которая будет мигать диодами и реагировать на клики мышью по кнопкам? Настоящую ПЛИС приобрести пока нет возможности.

В инете не нашел, но, быть может, плохо искал (ибо формулировка такого запроса - дело мутное).

А что, так можно было??

Есть какие-нибудь наработки для визуализации всего этого дела? Виртуальная эмуляция платы например, которая будет мигать диодами и реагировать на клики мышью по кнопкам? Настоящую ПЛИС приобрести пока нет возможности.

В инете не нашел, но, быть может, плохо искал (ибо формулировка такого запроса - дело мутное).

led_reg<=~led_reg;

А что, так можно было??

Никрасиво! :D

На самом деле, симулятор это очень даже няяя и кавайно.

HDL симулятор это основной инструмент разработки и отладки. Если noob решил учиться, то пусть учится сразу правильно. Некоторые малоопытные разработчики, немного пишущие на Verilog, как раз и задерживают свое развитие в данной области, потому что не желают научиться пользоваться симулятором. В итоге, когда нужно справить даже со средней сложности проектом, они оказываются беспомощными.

https://electronix.ru/forum/index.php?showtopic=147073

https://electronix.ru/forum/index.php?showtopic=147246

Приветствую!

Удачи! Rob.

Нет энтера после endmodule , он синим должен быть.

При чем тут энтер - if не может болтаться в теле модуля сам по себе - он должен быть либо в always либо в generate блоках.Код

module ...

generate

if (...) begin

assign var0 = ...

end

endgenerate

always_comb begin

if (..) begin

var1 = ...

end

end

always @(posedge clk) begin

if (..) begin

var2 <= ...

end

end

endmodule

generate

if (...) begin

assign var0 = ...

end

endgenerate

always_comb begin

if (..) begin

var1 = ...

end

end

always @(posedge clk) begin

if (..) begin

var2 <= ...

end

end

endmodule

Удачи! Rob.

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.