Полная версия этой страницы: FIFO на VHDL

Форум разработчиков электроники ELECTRONIX.ru > Программируемая логика ПЛИС (FPGA,CPLD, PLD) > Языки проектирования на ПЛИС (FPGA)

В Квартусе есть корка FIFO вполне такая ничего. Но там единица - байт. А как мне сделать FIFO пакетов по 13 байт?

Эээ.. Что вы имели ввиду под словом "единица"?

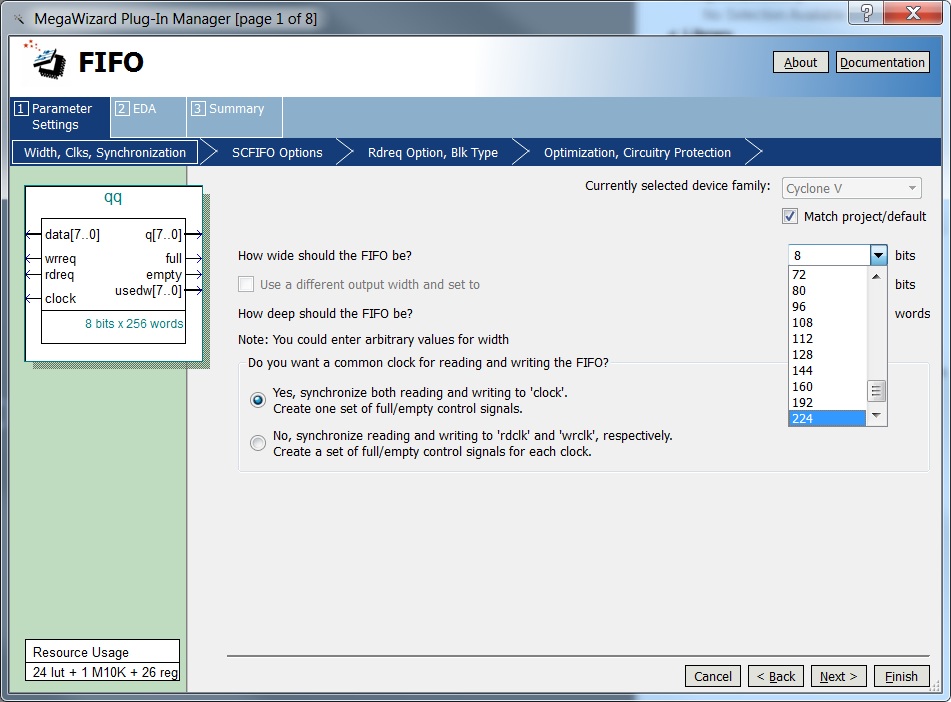

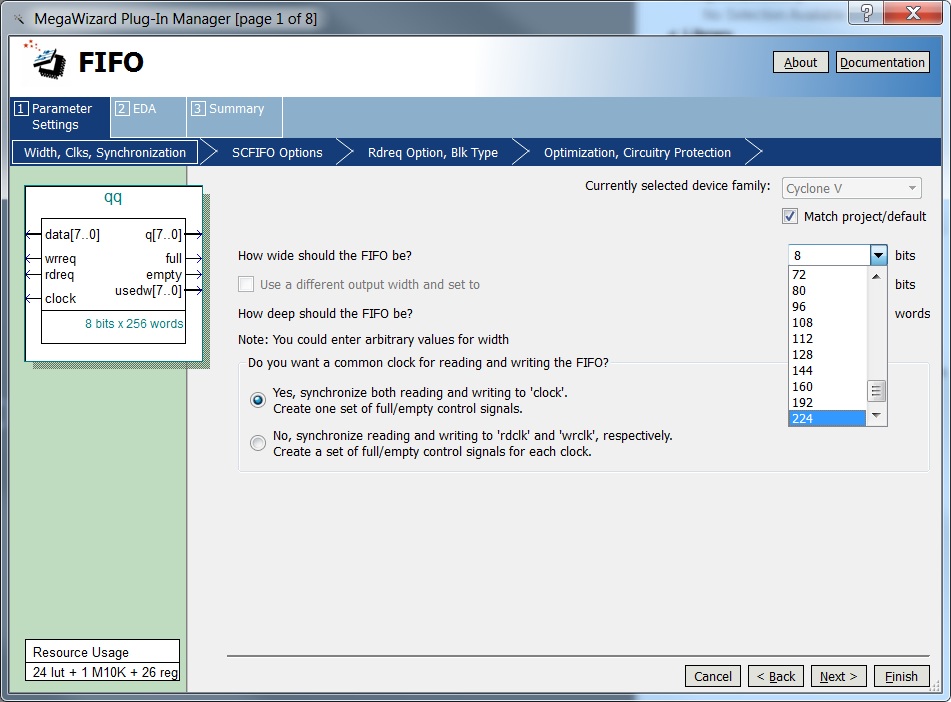

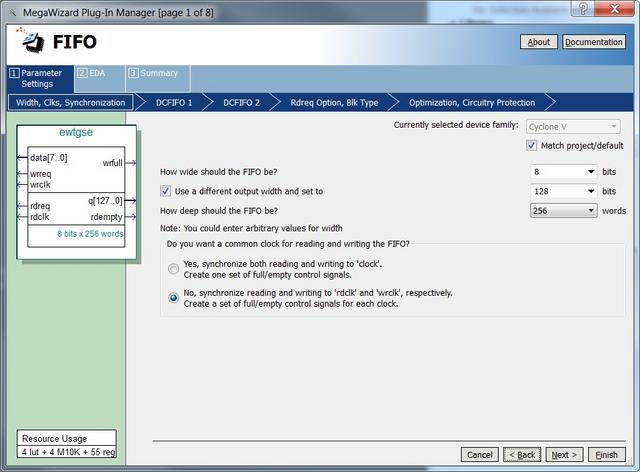

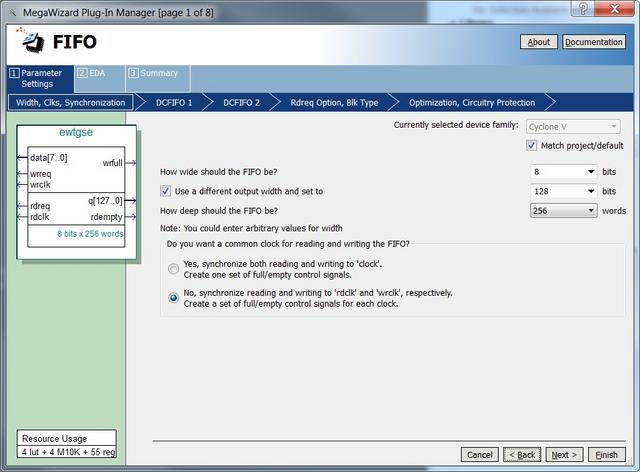

В версии 18:

Разрядность данных - от 1 до 256.

Глубина - от 4 и до конца памяти (ну или триггеров).

Вообще, не плохо бы знать про какой камень идёт речь.

В приаттаченой картинке скриншот.

Если имеется ввиду разрядность 13*8=104 бита, возьмите ближайшее значение - 108.

В версии 18:

Разрядность данных - от 1 до 256.

Глубина - от 4 и до конца памяти (ну или триггеров).

Вообще, не плохо бы знать про какой камень идёт речь.

В приаттаченой картинке скриншот.

Если имеется ввиду разрядность 13*8=104 бита, возьмите ближайшее значение - 108.

Эээ.. Что вы имели ввиду под словом "единица"?

В версии 18:

Разрядность данных - от 1 до 256.

Глубина - от 4 и до конца памяти (ну или триггеров).

Вообще, не плохо бы знать про какой камень идёт речь.

В приаттаченой картинке скриншот.

Если имеется ввиду разрядность 13*8=104 бита, возьмите ближайшее значение - 108.

В версии 18:

Разрядность данных - от 1 до 256.

Глубина - от 4 и до конца памяти (ну или триггеров).

Вообще, не плохо бы знать про какой камень идёт речь.

В приаттаченой картинке скриншот.

Если имеется ввиду разрядность 13*8=104 бита, возьмите ближайшее значение - 108.

это ФИФО байт. а мне нужно ФИФО объектов, скажем так. каждый объект 13 байт. объект вошел объект вышел.

ааа...понял. вы предлагаете сделать ширину шины в 13 байт. не знаю. мне это не очень нравиться.

Вместо того чтобы выбирать значения из списка можно это значение вписать руками. И будет Вам счастье

а как передать 13 байт на шину? они у меня в РАМ лежат.

Напишите свой контроллер поверх FIFO, который будет определять последовательное заполнение FIFO по 13 байт (пачкой) и выдавать их на выход непрерывной пачкой.

но данные надо ведь на шину загрузить. на вход. создал я data[0..103] но 13 байт лежат в РАМ. Как их загрузить из РАМ в data[0..103]?

В RAM эти 13 байт лежат один словом (word) шириной 104 бита или 13-тью байтными словами?

Если одним словом, то не вижу проблем паралельной выгрузки этой пачки на шину.

Если 13-тью словами, то нужен перевод из последовательного формата в параллельный (serdes).

Напишите свой контроллер поверх FIFO, который будет определять последовательное заполнение FIFO по 13 байт (пачкой) и выдавать их на выход непрерывной пачкой.

В RAM эти 13 байт лежат один словом (word) шириной 104 бита или 13-тью байтными словами?

Если одним словом, то не вижу проблем паралельной выгрузки этой пачки на шину.

Если 13-тью словами, то нужен перевод из последовательного формата в параллельный (serdes).

В RAM эти 13 байт лежат один словом (word) шириной 104 бита или 13-тью байтными словами?

Если одним словом, то не вижу проблем паралельной выгрузки этой пачки на шину.

Если 13-тью словами, то нужен перевод из последовательного формата в параллельный (serdes).

у меня РАМ 8х1024 - 1 килобайт. так как это сделать практически?

у меня РАМ 8х1024 - 1 килобайт. так как это сделать практически?

Выдайте из RAM 13 байт и запишите их в 13 байтных регистров, затем защелкните эти 13 регистров на шину шириной 104 бита с сигналом валидности.

Вообще, у производителя должны быть FIFO с настраиваемыми разными размерностями входных и выходных шин (вход - байтный, выход 13-ти байтный). По крайней мере, у Xilinx есть.

А как вам такое решение?

Я создал двухмерный массив

Я создал двухмерный массив

Код

type packet_t is array (12 downto 0) of std_logic_vector(7 downto 0);

type packet_fifo_t is array (31 downto 0) of packet_t;

signal tx_mailbox_fifo : packet_fifo_t;

shared variable g_fifo_head_idx : integer range 0 to 255 := 0;

shared variable g_fifo_tail_idx : integer range 0 to 255 := 0;

В одном процесе я загружаю байты в очередную ячейку из РАМtype packet_fifo_t is array (31 downto 0) of packet_t;

signal tx_mailbox_fifo : packet_fifo_t;

shared variable g_fifo_head_idx : integer range 0 to 255 := 0;

shared variable g_fifo_tail_idx : integer range 0 to 255 := 0;

Код

when ST_RAM_TO_TX_BUF_3 =>

if (idx2 < 13) then

tx_mailbox_fifo(g_fifo_head_idx)(idx2) <= slave_data_out2;

idx2 := idx2 + 1;

else

--get ready the next fifo slot

g_fifo_head_idx := g_fifo_head_idx + 1;

if (g_fifo_head_idx > 31) then

g_fifo_head_idx := 0;

end if;

RamState_b <= ST_RAMB_IDLE;

end if;

В другом слежу за индексомif (idx2 < 13) then

tx_mailbox_fifo(g_fifo_head_idx)(idx2) <= slave_data_out2;

idx2 := idx2 + 1;

else

--get ready the next fifo slot

g_fifo_head_idx := g_fifo_head_idx + 1;

if (g_fifo_head_idx > 31) then

g_fifo_head_idx := 0;

end if;

RamState_b <= ST_RAMB_IDLE;

end if;

Код

TX_MAILBOX_FIFO_MANAGER: process (REG_CLK)

begin

if (rising_edge(REG_CLK)) then

--send previous message - g_fifo_head_idx incremeted by 1 in other process

if (g_fifo_tail_idx < g_fifo_head_idx) then

tx_buf_ready <= '1';

end if;

if (update_tail_idx = '1') then

tx_buf_ready <= '0';

g_fifo_tail_idx := g_fifo_tail_idx + 1;

if (g_fifo_tail_idx > 31) then

g_fifo_tail_idx := 0;

end if;

end if;

end if;

end process TX_MAILBOX_FIFO_MANAGER;

И есть процесс посылкиbegin

if (rising_edge(REG_CLK)) then

--send previous message - g_fifo_head_idx incremeted by 1 in other process

if (g_fifo_tail_idx < g_fifo_head_idx) then

tx_buf_ready <= '1';

end if;

if (update_tail_idx = '1') then

tx_buf_ready <= '0';

g_fifo_tail_idx := g_fifo_tail_idx + 1;

if (g_fifo_tail_idx > 31) then

g_fifo_tail_idx := 0;

end if;

end if;

end if;

end process TX_MAILBOX_FIFO_MANAGER;

Код

when ST_TX_DATA => --send 13 byte of data

if (tx_byte_idx < 13) then

MSPI_WR_DATA <= X"00" & tx_mailbox_fifo(g_fifo_tail_idx)(tx_byte_idx);

MSPI_WR_START_TRIG <= '1'; --send a byte

tx_byte_idx := tx_byte_idx + 1;

NextState <= ST_TX_DATA;

McpState <= ST_WAIT_DONE;

else

MSPI_CS <= '1'; --chip select high

update_tail_idx <= '1';

NextState <= ST_MCP_IDLE;

McpState <= ST_REQ_TO_SEND0;

end if;

if (tx_byte_idx < 13) then

MSPI_WR_DATA <= X"00" & tx_mailbox_fifo(g_fifo_tail_idx)(tx_byte_idx);

MSPI_WR_START_TRIG <= '1'; --send a byte

tx_byte_idx := tx_byte_idx + 1;

NextState <= ST_TX_DATA;

McpState <= ST_WAIT_DONE;

else

MSPI_CS <= '1'; --chip select high

update_tail_idx <= '1';

NextState <= ST_MCP_IDLE;

McpState <= ST_REQ_TO_SEND0;

end if;

И всё таки, что вы хотите сделать?

Есть какая-то RAM.

Есть какое-то Fifo.

Зачем их нужно скрещивать?

Ну хорошо, почему нельзя сделать Ram с разной разрядностью входа и выхода?

Ну а сделать FIFO с разной разрядностью входа и выхода в чём проблема?

Есть какая-то RAM.

Есть какое-то Fifo.

Зачем их нужно скрещивать?

Ну хорошо, почему нельзя сделать Ram с разной разрядностью входа и выхода?

Ну а сделать FIFO с разной разрядностью входа и выхода в чём проблема?

я пришел к тому же выводу - ФИФО наше все. сериально загонять байты по 13 штук и считывать тоже по 13.

единственно я не понимаю - я должен стробировать сигнал wrreq? иначе как ФИФО знает что нужно принять следующий байт?

и то же самое при чтении - нужно стробировать rdreq?

я пришел к тому же выводу - ФИФО наше все. сериально загонять байты по 13 штук и считывать тоже по 13.

единственно я не понимаю - я должен стробировать сигнал wrreq? иначе как ФИФО знает что нужно принять следующий байт?

и то же самое при чтении - нужно стробировать rdreq?

единственно я не понимаю - я должен стробировать сигнал wrreq? иначе как ФИФО знает что нужно принять следующий байт?

и то же самое при чтении - нужно стробировать rdreq?

Рассматривайте сигнал wrreq - как сигнал валидности данных. Т.е подали на шину данные, и одновременно с ними выставили сигнал wrreq на 1 такт, чтобы данные записались в FIFO.

Вообще FIFO не знает ничего, кроме того, сколько в него записано слов, и пустой он или полный. Вы им сами управляете записью и чтением FIFO. Не совсем понимю, что Вы имеете ввиду когда говорите про стробирование wrreq и rdreq.

Рассматривайте сигнал wrreq - как сигнал валидности данных. Т.е подали на шину данные, и одновременно с ними выставили сигнал wrreq на 1 такт, чтобы данные записались в FIFO.

Вообще FIFO не знает ничего, кроме того, сколько в него записано слов, и пустой он или полный. Вы им сами управляете записью и чтением FIFO. Не совсем понимю, что Вы имеете ввиду когда говорите про стробирование wrreq и rdreq.

Вообще FIFO не знает ничего, кроме того, сколько в него записано слов, и пустой он или полный. Вы им сами управляете записью и чтением FIFO. Не совсем понимю, что Вы имеете ввиду когда говорите про стробирование wrreq и rdreq.

это я и имею в виду - выставить wrreq и потом опустить. и то же самое при чтении, я так понимаю перед каждым байтом выставить rdreq - он вытолкнет байт наружу и опустить rdreq.

это я и имею в виду - выставить wrreq и потом опустить. и то же самое при чтении, я так понимаю перед каждым байтом выставить rdreq - он вытолкнет байт наружу и опустить rdreq.

Извините меня но Вы вообще читали user guide на altera FIFO ?

Все ваши вопросы решаются за 10 минут путем запуска симуляции FIFO в modelsim.

Сигнал Wrreq удобно рассматривать как сигнал data_valid. Т.е какие данные сопровождает этот строб, такие данные и запишутся в память..

А вот сигнал rdreq чуть сложнее.

Сначала выставляете сигнал rd_req и только на следующем такте появляются данные.

НО !!!

Есть у этого FIFO есть очень интересный режим: show ahead mode.

Что за режим говорить не буду, ибо открывайте https://www.intel.com/content/dam/altera-ww.../ug/ug_fifo.pdf и курите мануал

Извините меня но Вы вообще читали user guide на altera FIFO ?

Все ваши вопросы решаются за 10 минут путем запуска симуляции FIFO в modelsim.

Сигнал Wrreq удобно рассматривать как сигнал data_valid. Т.е какие данные сопровождает этот строб, такие данные и запишутся в память..

А вот сигнал rdreq чуть сложнее.

Сначала выставляете сигнал rd_req и только на следующем такте появляются данные.

НО !!!

Есть у этого FIFO есть очень интересный режим: show ahead mode.

Что за режим говорить не буду, ибо открывайте https://www.intel.com/content/dam/altera-ww.../ug/ug_fifo.pdf и курите мануал

Все ваши вопросы решаются за 10 минут путем запуска симуляции FIFO в modelsim.

Сигнал Wrreq удобно рассматривать как сигнал data_valid. Т.е какие данные сопровождает этот строб, такие данные и запишутся в память..

А вот сигнал rdreq чуть сложнее.

Сначала выставляете сигнал rd_req и только на следующем такте появляются данные.

НО !!!

Есть у этого FIFO есть очень интересный режим: show ahead mode.

Что за режим говорить не буду, ибо открывайте https://www.intel.com/content/dam/altera-ww.../ug/ug_fifo.pdf и курите мануал

спасибо.

я посмотрел диаграмы записи и чтения. из них получается что разрешающие сигналы можно держать постоянно. но данные на каждом клоке нужно обновлять.

у меня тут вот какая дилема возникла. я получаю пакеты по 13 байт. а по какому условию мне считывать с ФИФО? не empty он уже на первом байте. а мне нужно посылать по 13 байт.

спасибо.

я посмотрел диаграмы записи и чтения. из них получается что разрешающие сигналы можно держать постоянно. но данные на каждом клоке нужно обновлять.

у меня тут вот какая дилема возникла. я получаю пакеты по 13 байт. а по какому условию мне считывать с ФИФО? не empty он уже на первом байте. а мне нужно посылать по 13 байт.

я посмотрел диаграмы записи и чтения. из них получается что разрешающие сигналы можно держать постоянно. но данные на каждом клоке нужно обновлять.

у меня тут вот какая дилема возникла. я получаю пакеты по 13 байт. а по какому условию мне считывать с ФИФО? не empty он уже на первом байте. а мне нужно посылать по 13 байт.

Сложно, практически невозможно ответить на вопрос, не зная всей задачи в целом !

Может вы хотите к соседу за солью сходить, который живет этажом выше. И вместо того, чтобы подняться на один этаж выше, строите катапульту, которая вас закинет в окно несчастному соседу

Приветствую!

Удачи! Rob.

...

у меня тут вот какая дилема возникла. я получаю пакеты по 13 байт. а по какому условию мне считывать с ФИФО? не empty он уже на первом байте. а мне нужно посылать по 13 байт.

Как по какому? - Вы же сами это условие задаете - как только в FIFO будет >= 13 байт можно запускать считывание пакета в 13 байт! Причем читать можно бурстом - одним куском. И всего то нужно FIFO с выходом счетчика доступных для чтения слов.у меня тут вот какая дилема возникла. я получаю пакеты по 13 байт. а по какому условию мне считывать с ФИФО? не empty он уже на первом байте. а мне нужно посылать по 13 байт.

Удачи! Rob.

сделал ФИФО

Пишу два пакета по 13 байт - debug_val1 = 26 - логично. а debug_val4 = 0 - ноль записанных слов? почему?

Код

component fifo IS port

(

clock : in std_logic;

data : in std_logic_vector (7 DOWNTO 0);

rdreq : in std_logic;

sclr : in std_logic;

wrreq : in std_logic;

almost_empty : out std_logic;

almost_full : out std_logic;

empty : out std_logic;

full : out std_logic;

q : out std_logic_vector (7 DOWNTO 0);

usedw : out std_logic_vector (8 DOWNTO 0)

);

end component;

U_FIFO : fifo

port map

(

clock => REG_CLK,

data => fifo_data_in,

rdreq => fifo_rdreq,

sclr => '0',

wrreq => fifo_wrreq,

almost_empty => fifo_almost_empty,

almost_full => fifo_almost_full,

empty => fifo_empty,

full => fifo_full,

q => fifo_data_out,

usedw => fifo_usedw

);

Пишу (

clock : in std_logic;

data : in std_logic_vector (7 DOWNTO 0);

rdreq : in std_logic;

sclr : in std_logic;

wrreq : in std_logic;

almost_empty : out std_logic;

almost_full : out std_logic;

empty : out std_logic;

full : out std_logic;

q : out std_logic_vector (7 DOWNTO 0);

usedw : out std_logic_vector (8 DOWNTO 0)

);

end component;

U_FIFO : fifo

port map

(

clock => REG_CLK,

data => fifo_data_in,

rdreq => fifo_rdreq,

sclr => '0',

wrreq => fifo_wrreq,

almost_empty => fifo_almost_empty,

almost_full => fifo_almost_full,

empty => fifo_empty,

full => fifo_full,

q => fifo_data_out,

usedw => fifo_usedw

);

Код

FIFO_INTERFACE : process (REG_CLK) variable fifo_idx : integer range 0 to 255 := 0;

begin

if (rising_edge(REG_CLK)) then

case FifoState is

when ST_FIFO_IDLE =>

fifo_idx := 0;

debug_val4 <= fifo_usedw(7 downto 0);

if (fifo_write = '1') then

if (fifo_almost_full = '0') then

FifoState <= ST_FIFO_WRITE;

end if;

end if;

when ST_FIFO_WRITE => --continious write to FIFO

if (cs2 = '0') then --chip select low

if (rx_rdy4 = '1') then --byte received

fifo_wrreq <= '1';

fifo_data_in <= sspi_data_in;

fifo_idx := fifo_idx + 1;

debug_val1 <= debug_val1 + '1';

end if;

if (fifo_idx > 13) then --overflow protection

fifo_idx := 0;

fifo_wrreq <= '0';

FifoState <= ST_FIFO_IDLE;

end if;

else

fifo_idx := 0;

fifo_wrreq <= '0';

FifoState <= ST_FIFO_IDLE;

end if;

end case;

end if;

end process FIFO_INTERFACE;

begin

if (rising_edge(REG_CLK)) then

case FifoState is

when ST_FIFO_IDLE =>

fifo_idx := 0;

debug_val4 <= fifo_usedw(7 downto 0);

if (fifo_write = '1') then

if (fifo_almost_full = '0') then

FifoState <= ST_FIFO_WRITE;

end if;

end if;

when ST_FIFO_WRITE => --continious write to FIFO

if (cs2 = '0') then --chip select low

if (rx_rdy4 = '1') then --byte received

fifo_wrreq <= '1';

fifo_data_in <= sspi_data_in;

fifo_idx := fifo_idx + 1;

debug_val1 <= debug_val1 + '1';

end if;

if (fifo_idx > 13) then --overflow protection

fifo_idx := 0;

fifo_wrreq <= '0';

FifoState <= ST_FIFO_IDLE;

end if;

else

fifo_idx := 0;

fifo_wrreq <= '0';

FifoState <= ST_FIFO_IDLE;

end if;

end case;

end if;

end process FIFO_INTERFACE;

Пишу два пакета по 13 байт - debug_val1 = 26 - логично. а debug_val4 = 0 - ноль записанных слов? почему?

Ничего не понял, что Вы хотите сделать !

кхм...даже стесняюсь спросить...а кто то вообще работал с ФИФО? может показать как писать в ФИФО?

кхм...даже стесняюсь спросить...а кто то вообще работал с ФИФО? может показать как писать в ФИФО?

Очень странные вопросы Вы задаете ! Что тут показывать то ? Читаете https://www.intel.com/content/dam/altera-ww.../ug/ug_fifo.pdf и вперед. Очень похоже на разговор слепого с глухим. Тема была создана 1 августа, сегодня уже 6. И судя по вопросам, Вы так и не удосужились прочитать user guide на FIFO, хотя это Вы должны были сделать в первую очередь. Тогда возникает вопрос ради чего вообще была создана тема ?

кхм...даже стесняюсь спросить...а кто то вообще работал с ФИФО? может показать как писать в ФИФО?

У меня выражение лица сейчас, как на аватарке Flip-fl0p.

FIFO один из самых распространенных функциональных узлов на ПЛИС.

https://drive.google.com/open?id=1wyWqPKKIC...VzMEuKcOAJDaHJ9

Пример записи в FIFO 7 байт пачкой и чтения из него побайтно. Можно делать и наоборот: записывать побайтно, а читать непрерывной пачкой. Можно вообще почти как угодно.

Потренируйтесь на простых блоках, посимулеруйте разные варианты записи и чтения FIFO и ясность появится.

Приветствую!

. Бывало что разрешение чтения неплотно прилегало и данные медленно считывались в процессе использования FIFO. Поэтому когда уровень опускался ниже порога Almost Full приходилось периодически приоткрывать запись и добавлять горячих данных в FIFO. В конце цикла сигнал разрешения чтения открывался полностью и данные бурстом считывались в pipe переработки данных.

. Бывало что разрешение чтения неплотно прилегало и данные медленно считывались в процессе использования FIFO. Поэтому когда уровень опускался ниже порога Almost Full приходилось периодически приоткрывать запись и добавлять горячих данных в FIFO. В конце цикла сигнал разрешения чтения открывался полностью и данные бурстом считывались в pipe переработки данных.

Удачи! Rob.

кхм...даже стесняюсь спросить...а кто то вообще работал с ФИФО? может показать как писать в ФИФО?

Раньше я каждый день пользовался FIFO вечерком - как приду с работы - окрываю сигнал записи и набираю горячие данные в FIFO до уровня Almost Full. Если не уследить и не запретить запись вовремя то можно и перелить выше Full уровня - и тогда беда - данные теряются (и могут утечь к соседу) Удачи! Rob.

Приветствую!

Раньше я каждый день пользовался FIFO вечерком - как приду с работы - окрываю сигнал записи и набираю горячие данные в FIFO до уровня Almost Full. Если не уследить и не запретить запись вовремя то можно и перелить выше Full уровня - и тогда беда - данные теряются (и могут утечь к соседу) . Бывало что разрешение чтения неплотно прилегало и данные медленно считывались в процессе использования FIFO. Поэтому когда уровень опускался ниже порога Almost Full приходилось периодически приоткрывать запись и добавлять горячих данных в FIFO. В конце цикла сигнал разрешения чтения открывался полностью и данные бурстом считывались в pipe переработки данных.

. Бывало что разрешение чтения неплотно прилегало и данные медленно считывались в процессе использования FIFO. Поэтому когда уровень опускался ниже порога Almost Full приходилось периодически приоткрывать запись и добавлять горячих данных в FIFO. В конце цикла сигнал разрешения чтения открывался полностью и данные бурстом считывались в pipe переработки данных.

Удачи! Rob.

Раньше я каждый день пользовался FIFO вечерком - как приду с работы - окрываю сигнал записи и набираю горячие данные в FIFO до уровня Almost Full. Если не уследить и не запретить запись вовремя то можно и перелить выше Full уровня - и тогда беда - данные теряются (и могут утечь к соседу)

Удачи! Rob.

Спасибо за хороший рассказ. Посмеялся от души

кхм...даже стесняюсь спросить...а кто то вообще работал с ФИФО? может показать как писать в ФИФО?

Стесняюсь спросить, а вы точно под свои аккаунтом зашли?

Для просмотра полной версии этой страницы, пожалуйста, пройдите по ссылке.