Имеем 2 независимых клока (скажем, 20 и 24 МГц), требуется сделать переключататель, который на выходе даёт 20,10,24,12 МГц (выбор - 2 асинхронными сигналами). Требуется, чтобы на выходе не появлялось импульсов короче, чем полупериод самого быстрого входного клока.

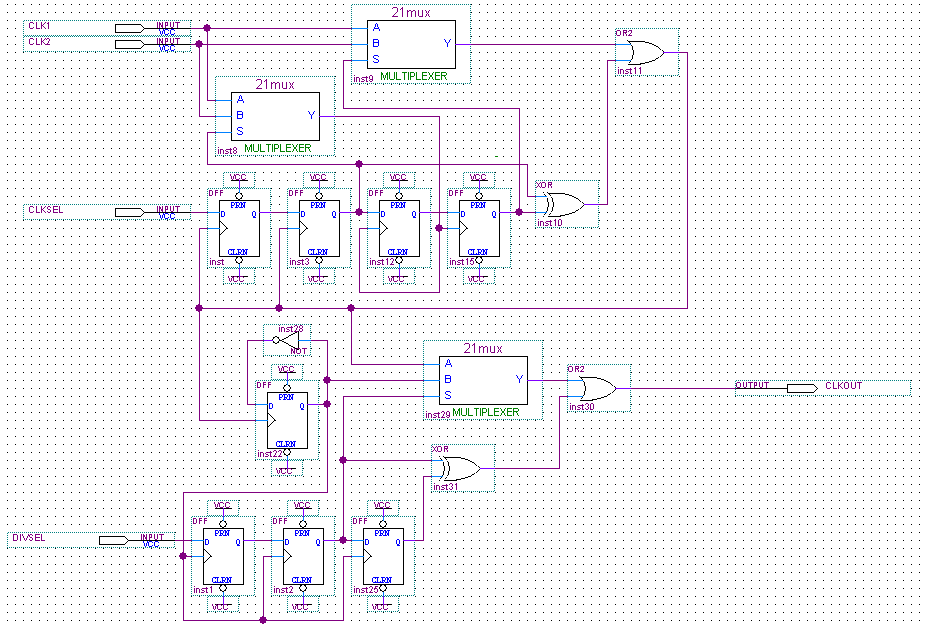

Родил вот такую схему (нарисовано в квартусе)

, насколько она корректна?

, насколько она корректна?PS: вполне понимаю, что схема асинхронная и на очень быстрых клоках всё равно возможны глюки. Но макс. частота такая, как указана выше, а моделирование вроде бы не выявляет глитчей (целевой чип - epm3032).