| |

|

|

Altera: manual routing Altera: manual routing, Как управлять размещением межсоединений? |

|

|

|

|

Dec 19 2011, 10:14 Dec 19 2011, 10:14

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 9-10-07

Пользователь №: 31 202

|

Добрый день, уважаемые ПЛИСоводы. Столкнулся со следующей проблемой: Fitter по-разному размещает межсоединения, хотя ячейки назначены одинаково. Разница в двух проектах лишь в том, что левом - больше логики (расширен проект), а в правом - у ячейки больше выходов (Fan-out)

РЈРСВВВВВеньшено Р В Р’В Р СћРІР‚ВВВВР С• 88%

1438 x 472 (51.65 килобайт)

|

Подскажите, пожалуйста, если кто-то встречался, как указать fitter'у использовать межсоединения для рядов, а не смежные? Мне требуется максимально выровнять задержку (как на правом рисунке). Возможно, есть другие способы? Использую EP1C3T100C6. PS. Прошу прощения - ошибся немного темой, нужно было в САПР...

Сообщение отредактировал Egor-ka - Dec 19 2011, 11:25

|

|

|

|

|

|

|

|

Dec 21 2011, 18:59 Dec 21 2011, 18:59

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 9-10-07

Пользователь №: 31 202

|

Форумчане дорогие, ну неужели никто даже прокомментировать и на пути решения направить не может?

|

|

|

|

|

|

|

|

Dec 22 2011, 04:50 Dec 22 2011, 04:50

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 9-10-07

Пользователь №: 31 202

|

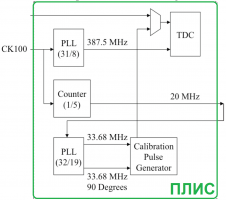

Во-первых, я как раз и хочу понять из каких соображений Quartus раскидывает межсоединения? Во-вторых, мне важно не минимальное время задержки между ячейками, а именно одинаковое. Я пытаюсь сделать задержку асинхронного сигнала с точностью меньше периода тактовой, для этого я использую чертыре фазы частоты для оцифровки асинхронного сигнала и их же - для формирования задержанного импульса. Quartus не позволяет размещать ячейки тактичуемые частотыми с разными фазами в одном LAB'е(те 0 и 180 можно в одном, а 90 и 270 - в другом)  FPGA_ADC_TDC.ppt

FPGA_ADC_TDC.ppt ( 1.73 мегабайт )

Кол-во скачиваний: 210Определяю фазу асинхронного сигнала, как описано в статье, но кроме определения времени прихода асинхронного сигнала, я пытаюсь аналогичным способом сформировать задерженный импульс. Для этого как раз очень важно равное время распространения. Просто в версии, где задержки равные, у меня все получилось. Чуть изменил проект и уже точность получилась меньше..

|

|

|

|

|

|

|

|

Dec 22 2011, 13:35 Dec 22 2011, 13:35

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 9-10-07

Пользователь №: 31 202

|

Возможно я ошибаюсь, но как понимаю, констрейны и timequest analysis предназначены в основном для синхронных проектов (в общем то как и ПЛИС в целом). Их основная задача проследить, чтобы сигнал данных соотвествовал определенному клоку во избежание неправильной передачи данных (между регистрами или даже смежными чипами). Поэтому, как мне кажется, с помощью этих инструментов невозможно так точно ( 10 пс) задать время распространения сигнала. В основном таймквест отслеживает, чтобы данные приходили раньше периода тактовой частоты, так что точность получается в пределах 1нс.

Из статей des00 вижу только вариант использования set max/min delay, но пока не понимаю как, ведь ячейки у меня зафиксированы, а если убрать фиксацию, то как написал выше, вряд ли получится такая же точность.

Меня больше интересует, почему в почти одинаковых проектах квартус располагает межсоединения по разному?

|

|

|

|

|

|

|

|

Dec 22 2011, 14:17 Dec 22 2011, 14:17

|

Профессионал

Группа: Свой

Сообщений: 1 088

Регистрация: 20-10-09

Из: Химки

Пользователь №: 53 082

|

Цитата(Egor-ka @ Dec 22 2011, 17:35)  Меня больше интересует, почему в почти одинаковых проектах квартус располагает межсоединения по разному? Вы задали ограничения на межсоединения - нет, поэтому квартусу все равно. Ключевое слово здесь "почти", каждый раз разводится по разному, даже если поменяли настройки, а у Вас там fan-out другой. Цитата Возможно я ошибаюсь, но как понимаю, констрейны и timequest analysis предназначены в основном для синхронных проектов (в общем то как и ПЛИС в целом). Их основная задача проследить, чтобы сигнал данных соотвествовал определенному клоку во избежание неправильной передачи данных (между регистрами или даже смежными чипами). Поэтому, как мне кажется, с помощью этих инструментов невозможно так точно ( 10 пс) задать время распространения сигнала. В основном таймквест отслеживает, чтобы данные приходили раньше периода тактовой частоты, так что точность получается в пределах 1нс. Как правило не достаточно задать ограничения на тактовые частоты, требуется задавать еще на входные данные относительно в том числе и относительно тактовой (в некоторых случаях квартус сам будет вставлять логические болки для "выравнивания"). Стабильную точность в 10пс Вы никак не получите, не поверю я в это. Честно говоря не осилил статью, а Ваше описание алгоритма мне лично не понятно. Цитата Я пытаюсь сделать задержку асинхронного сигнала с точностью меньше периода тактовой, для этого я использую чертыре фазы частоты для оцифровки асинхронного сигнала и их же - для формирования задержанного импульса. Поподробнее бы описали, что за сигнал, как соотносится с тактовой (которая кстати тоже извне синхронно поступает?), с какой точностью.

|

|

|

|

|

|

|

|

Dec 22 2011, 15:57 Dec 22 2011, 15:57

|

Знающий

Группа: Свой

Сообщений: 859

Регистрация: 7-04-05

Из: Санкт-Петербург

Пользователь №: 3 943

|

Посмотрите стр.9 - примерно то, что вам нужно.

Прикрепленные файлы

an356.pdf

an356.pdf ( 155.22 килобайт )

Кол-во скачиваний: 96

--------------------

"Человек - это существо, которое охотнее всего рассуждает о том, в чем меньше всего разбирается." (с) С.Лем

|

|

|

|

|

|

|

|

Dec 22 2011, 20:26 Dec 22 2011, 20:26

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 9-10-07

Пользователь №: 31 202

|

Gate, огромное спасибо - в самую точку. Просто и понятно.  Что какается Цитата(bogaev_roman @ Dec 22 2011, 18:17)  Вы задали ограничения на межсоединения - нет, поэтому квартусу все равно. Если вы не видели, то я как раз в своем первом сообщении и спрашивал как это сделать... Точность в 10 пс - относится к внутренним сигналам (то что показано на рисунке). Моя задача - задерживать внешний асинхронный импульс на Nое количество времени с максимальной точностью на ПЛИС. Исследую способы повышения точности. Пока добился джиттера выходного задержанного импульса, равного 80% периода внутернней тактовой частоты (от PLL). Если кто-то встреячался с такими заданиями, какой вообще точности следует ожидать? Кстати, кто-нибудь знает как создать генератор кореллированных импульсов, как на рисунке

РЈРСВВВВВеньшено Р В Р’В Р СћРІР‚ВВВВР С• 81%

906 x 803 (113.09 килобайт)

|

, но с помощью одного PLL?

|

|

|

|

|

|

|

|

Dec 23 2011, 13:17 Dec 23 2011, 13:17

|

Знающий

Группа: Свой

Сообщений: 859

Регистрация: 7-04-05

Из: Санкт-Петербург

Пользователь №: 3 943

|

2Egor-kaЕсли вы делаете TDC, посмотрите еще xilinx xapp224. Если вам не нужно иметь десяток каналов в одном устойстве, то рекомендую acam gpx: http://www.acam-usa.com/GPX.html

--------------------

"Человек - это существо, которое охотнее всего рассуждает о том, в чем меньше всего разбирается." (с) С.Лем

|

|

|

|

|

|

|

|

Dec 23 2011, 15:11 Dec 23 2011, 15:11

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 9-10-07

Пользователь №: 31 202

|

2Gate

Спасибо за документы, у меня как раз что-то похожее получается.

Я пытаюсь усовершенствовать управляемую линию задержки, для этого хочу использовать TDC.

Так как устройства такие уже произведены, работаю на имеющейся эл.базе. Поэтому пока GPX не рассматриваю.

По поводу разводки межсоединений:

нашел, где Quartus это прописывает - файл .rcf - routing constraint file - но пока не понял, можно ли как-то его в этих целях использовать?

К тому же, этот файл создается при использовании back-annotation, а как с этим работать тоже пока не понял.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|