| |

|

|

Свои процессоры Свои процессоры, Разработка своих процессоров со своей системой команд |

|

|

|

|

May 26 2014, 06:59 May 26 2014, 06:59

|

Лентяй

Группа: Свой

Сообщений: 2 203

Регистрация: 11-10-04

Из: Санкт-Петербург

Пользователь №: 843

|

Цитата(Serhiy_UA @ May 26 2014, 14:49)  Меня же пока интересует маленький процессор на 8 или 16 разрядов, с ограниченным набором команд, Насколько "маленький" должен быть процессор в ресурсах ПЛИС? Есть пара "почти доделанных" вариантов 8-разрядникров "для души" (порядка 200-400 LE в зависимости от степени махровости)  Цитата(Serhiy_UA @ May 26 2014, 14:49)  который загружался бы в ПЛИС типа Cyclone III, например, с EPCS16. И помимо процессора, чтобы можно было загружать программы к нему, а также другую аппаратную обвязку.

Для подобных загрузок надо знать, как вместе с процессором разместить в EPCS программу к нему, и как все это из EPCS выгрузить. Для NiosII это решается интегрированной средой и с применением jic-файла А зачем так сложно? Размещейте код в блоках встроенного ОЗУ ПЛИСа. Для отладки кода можно использовать In-system Memory Content Editor. А финальная версия кода будет содержаться в pof'е и грузиться во всторенное ОЗУ ПЛИС в процессе конфигурирования.

--------------------

Чтобы слова не расходились с делом, нужно молчать и ничего не делать...

|

|

|

|

|

|

|

|

May 26 2014, 10:01 May 26 2014, 10:01

|

Участник

Группа: Участник

Сообщений: 45

Регистрация: 22-12-10

Из: Россия, Ростовская обл.

Пользователь №: 61 800

|

Цитата(Serhiy_UA @ May 26 2014, 14:49)  Прочел ссылки, и на мой взгляд, Вы синтезируете аппаратный диспетчер для многозадачных процессов, с целью ускорения работы операционных систем. Но могу и ошибаться… Это должно получиться в результате, но пока ещё работа далека от завершения. В текущем состоянии устройство представляет из себя маленький и довольно простой 32-битный микропроцессор. Единственное, что может оттолкнуть от его использования - отсутствие прерываний. При желании прерывания можно реализовать сверху, обернув ядро, но в конечном устройстве прерывания будут замещены сообщениями, поэтому не вижу особого смысла разрабатывать то, от чего потом придётся откзаться. Цитата(Serhiy_UA @ May 26 2014, 14:49)  Меня же пока интересует маленький процессор на 8 или 16 разрядов, с ограниченным набором команд, который загружался бы в ПЛИС типа Cyclone III, например, с EPCS16. Посмотрите вот это (кликабельно):  Цитата(Serhiy_UA @ May 26 2014, 14:49)  И помимо процессора, чтобы можно было загружать программы к нему, а также другую аппаратную обвязку.

Для подобных загрузок надо знать, как вместе с процессором разместить в EPCS программу к нему, и как все это из EPCS выгрузить. Для NiosII это решается интегрированной средой и с применением jic-файла, но не понятны детали, как это все делать и увязать самому.

Конечно, NiosII удовлетворяет с лихвой, но есть задачи и для души... Задачи для души, по моему скромному мнению, это самый лучший стимул для разработки. Я использовал мегафункцию ROM для размещения интерактивного монитора и загрузчика по протоколу X-modem непосредственно в ПЛИС. В принципе, в микрокод можно поместить довольно сложные программы. Ой... Вы имеете в виду как загрузить из EPCS пользовательскую программу в процессор и что NiosII умеет это делать. Да, я тоже хотел бы это знать, как можно "программно" прочитать регион памяти из EPCS, в которой зашита прошивка устройства. Некоторая информация есть вот здесь .

Сообщение отредактировал alman - May 26 2014, 10:51

|

|

|

|

|

|

|

|

Jun 25 2014, 12:28 Jun 25 2014, 12:28

|

Местный

Группа: Участник

Сообщений: 368

Регистрация: 18-04-11

Из: Город-герой Москва

Пользователь №: 64 451

|

Здравствуйте, товарищи! Не совсем пишу туда куда надо, но не хочу создавать целую тему, во всяком случае пока что, так что выскажусь здесь. Не имю большого опыта в работе с софт процессорами, но весчь безусловна интересная и архиполезная! Вот и я гуляя по просторам тырнета в поисках халявный ядрышек набрёл на сайтик http://www.oreganosystems.at/?page_id=96 на коем валяется бесплатный проектик ядра 8051. Вообщем собрал я его и запустил, удачно поморгал сетодиодиками, но вот в итоге встал вопрос, что дальше то? У меня стоит задача общения с n-ым кол-вом устройств по уарт на скорости до 1Мб/с. Однако как я понял, по диодикам, ядро работает не так что б аж "В ЛЁТ"! На симулирование времени не было. Досканально разбирать код -  крыша съедит, нет ни времени ни желания. Правда прогнал его через TimeQuest, в коем я совсем и не спец (ограничения задал лишь на клоковую частоту) ну и на 25МГц полезли слаки (хотя в даташитах написано, что эту частоту выставлять и надо). В составе ядра имеется т.н. datamux, который и портил картину - весь проект тактируется по переднему фронту, а этот блок по заднему! В следствии точо, что как я понял из схемы он и не нужен вообщем (схема видимо сыровата и последний раз правилась аж 10 лет назад) то я его исключил. И вроде на 25МГц завелось. Но вот мож но ли ещё частоту задрать? Вообщем вопрос в следующем, кто нибудь вообще с этой штукой ковырялся и стоит ли вообще её ковырять? P.S. Цитата Конечно, NiosII удовлетворяет с лихвой, но есть задачи и для души... Сложно представить, во всяком случае если он эконом класса... т.е. БЕСплатный! АВРка и та могутнее в ряде случаев будит, хотя конечно если количество интерфейсов или счётчиков не нормировано... то да-с...

Сообщение отредактировал Грендайзер - Jun 25 2014, 12:38

|

|

|

|

|

|

|

|

Jun 25 2014, 12:34 Jun 25 2014, 12:34

|

Гуру

Группа: Модераторы

Сообщений: 4 011

Регистрация: 8-09-05

Из: спб

Пользователь №: 8 369

|

Цитата(Грендайзер @ Jun 25 2014, 16:28)  бесплатный проектик ядра 8051.

Вообщем вопрос в следующем, кто нибудь вообще с этой штукой ковырялся и стоит ли вообще её ковырять? На открытых проектах полно разных процессоров. Так зачем их искать по "помойкам", да еще тех, которые не поддерживаются... Чем не устраивают те, к которым есть компиляторы? Скажем Альтеровские? Или бесплатные Актеловские? А может вообще, N+1 автомат нужен и все дела?

--------------------

www.iosifk.narod.ru

|

|

|

|

|

|

|

|

Jun 25 2014, 12:56 Jun 25 2014, 12:56

|

Местный

Группа: Участник

Сообщений: 368

Регистрация: 18-04-11

Из: Город-герой Москва

Пользователь №: 64 451

|

Ну по поводу открытых проектов - как я понял эти занимаются все у кого душа к этому тяготеет, и прожжёный спец и начинающий любитель... так что как попадёшь, и в этом плане данное ядро ничем не отличается от открытых ресурсов. А вот дока на него очень качественная! Теперь, что значит Цитата не поддерживаются... и Цитата Чем не устраивают те, к которым есть компиляторы? Программку то я для него написал и скомпилил!!! Более того скоомпилил в последней (бесплатной версии) Keil, её я скачал с сайта совсем не давно. Да и ядро это тащем то популярное... относительно, даже в нынешнее время! Ниос же как я писал эконом класа меня не устроил (не успевает он достойно обрабатывать прерывания на той скорости что я указывал), а "экспропреировать" его не выходит. С актеловскими вообще не знаком и как вообще аолучится ли их в альтеру то засунуть?

|

|

|

|

|

|

|

|

Sep 1 2014, 14:16 Sep 1 2014, 14:16

|

Профессионал

Группа: Участник

Сообщений: 1 075

Регистрация: 30-09-05

Пользователь №: 9 118

|

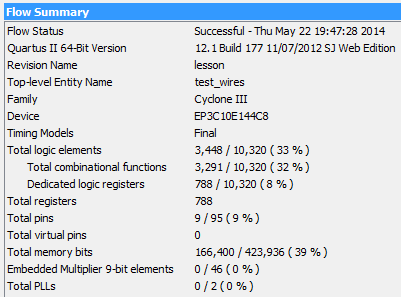

Для нового проекта перешел на Altera. Попробовал перенести давнишнее ядро, оптимизированное под Xilinx: http://electronix.ru/forum/index.php?showt...mp;#entry597323и сразу проблемы: 1) Квартус ни под каким соусом не хочет есть Верилоговское описание True Dual Port памяти с сигналом разрешения клока. Это действительно так, или плохо смотрел? 2) Квартус не хочет автоматом размещать в MLAB мелкие регистровые файлы с асинхронным чтением, без явного размещения атрибута (* ramstyle = "MLAB, no_rw_check" *) перед каждым объявлением мелкой памяти. Это действительно так, или плохо смотрел? Пока-что двухпортовую память выделил в отдельную мегафункцию, и вставил нужный атрибут перед объявлением регистрового файла (но это неудобно, тк Верилоговский код синтезируется автоматом из другого описания). Дизайн заработал, результат синтеза для 32-разрядного ядра(Фон-Неймановская архитектура с 1К РФ в памяти) + память(2К слов) + UART + кнопки + светодиоды: Код +------------------------------------------------------------------------------+

; Fitter Summary ;

+---------------------------------+--------------------------------------------+

...

; Family ; Cyclone V ;

; Device ; 5CGXFC5C6F27C7 ;

; Timing Models ; Final ;

; Logic utilization (in ALMs) ; 203 / 29,080 ( < 1 % ) ;

; Total registers ; 197 ;

; Total pins ; 26 / 364 ( 7 % ) ;

; Total virtual pins ; 0 ;

; Total block memory bits ; 73,728 / 4,567,040 ( 2 % ) ;

...

+---------------------------------+--------------------------------------------+ Как описать такую память на Верилоге, чтобы Квартус понял?

Эскизы прикрепленных изображений

|

|

|

|

|

|

|

|

Sep 2 2014, 09:02 Sep 2 2014, 09:02

|

Лентяй

Группа: Свой

Сообщений: 2 203

Регистрация: 11-10-04

Из: Санкт-Петербург

Пользователь №: 843

|

Цитата(Leka @ Sep 1 2014, 18:16)  1) Квартус ни под каким соусом не хочет есть Верилоговское описание True Dual Port памяти с сигналом разрешения клока. Это действительно так, или плохо смотрел?

...

Как описать такую память на Верилоге, чтобы Квартус понял? Не оно: Verilog HDL: True Dual-Port RAM with a Single Clock ? Ну и другие примеры там посмотреть можно...

--------------------

Чтобы слова не расходились с делом, нужно молчать и ничего не делать...

|

|

|

|

|

|

|

|

Sep 2 2014, 09:34 Sep 2 2014, 09:34

|

Гуру

Группа: Свой

Сообщений: 3 304

Регистрация: 13-02-07

Из: 55°55′5″ 37°52′16″

Пользователь №: 25 329

|

Цитата(Leka @ Sep 1 2014, 16:16)  1) Квартус ни под каким соусом не хочет есть Верилоговское описание True Dual Port памяти с сигналом разрешения клока. Это действительно так, или плохо смотрел? У меня вот такое нормально работает на альтере и хилых, не совсем разрешение клока конечно но может вам подойдёт: CODE

//////////////////////////////////////////////////////////////////////////////////

module sdpram #(parameter p_DW = 0, parameter p_AW = 0)

(

// SYS_CON

input i_clk,

// IN / port-a

input i_we_a,

input [p_AW-1:0] iv_addr_a,

input [p_DW-1:0] iv_data_a,

// OUT / port-b

input i_rd_b,

input [p_AW-1:0] iv_addr_b,

output reg [p_DW-1:0] ov_data_b

);

//////////////////////////////////////////////////////////////////////////////////

// ram-MEM

reg [p_DW-1:0] sv_mem [2**p_AW-1:0];

//////////////////////////////////////////////////////////////////////////////////

//

// Construct "Simple Dual Port RAM" logic

//

always @ (posedge i_clk)

begin : RAM_LOGIC

// IN / port-a

if (i_we_a)

sv_mem[iv_addr_a] <= iv_data_a;

// OUT / port-b

if (i_rd_b)

ov_data_b <= sv_mem[iv_addr_b];

end

//////////////////////////////////////////////////////////////////////////////////

endmodule

|

|

|

|

|

|

|

|

Sep 2 2014, 10:20 Sep 2 2014, 10:20

|

Знающий

Группа: Свой

Сообщений: 721

Регистрация: 23-10-08

Из: next to Odessa

Пользователь №: 41 112

|

Цитата(Leka @ Sep 1 2014, 21:57)  ...но есть другая принципиальная проблема, почему и перешел на Квартус... Уточните, в чем проблема и почему переход на Квартус ее решил... Сделал недавно небольшой софт RISC-процессор на 8 разрядов. Память команд и данных по 4К. Система команд - 25 инструкций, схожая на MCS51. Всего 20% времени ушло на verilog-синтез и 80% - на программирование на С++ транслятора с ассемблера в машинные коды.Память программ сначала была одно-, а потом двух-портовая, что в итоге позволило двухбайтные команды также выполнять за один такт. На Cyclone III скорость 100 MГц. Выгода этого дела - процессор можно постоянно улучшать как по системе команд и функционалу, так и по производительности. Если будет свободное время…

|

|

|

|

|

|

|

|

Sep 2 2014, 16:22 Sep 2 2014, 16:22

|

Профессионал

Группа: Участник

Сообщений: 1 075

Регистрация: 30-09-05

Пользователь №: 9 118

|

Такое описание синтезируется: Код //True Dual Port RAM

module mem(

output reg [10-1:0] qA, qB,

input [10-1:0] dA, dB,

input [10-1:0] aA, aB,

input weA, weB, reA, reB, clkA, clkB

);

//(* ramstyle = "M10K, no_rw_check" *)

reg [10-1:0] ram[2**10-1:0];

always@(posedge clkA)

if(weA)

ram[aA] = dA;

always@(posedge clkB)

if(weB)

ram[aB] = dB;

always@(posedge clkA)

//if(reA)

qA <= ram[aA];

always@(posedge clkB)

//if(reB)

qB <= ram[aB];

endmodule а с сигналами разрешения чтения не синтезируется. Придется костыль приделывать... Цитата(Serhiy_UA @ Sep 2 2014, 14:20)  Уточните, в чем проблема и почему переход на Квартус ее решил... Мои интересы сейчас - переход на более высокий уровень описания синхронных схем. И Quartus намного быстрее ISE синтезирует кошмар, сгенерированный моими прогами. По поводу простого ядра - могу выложить свое 5-летней давности (более поздние еще не реанимировал) с простым компилятором(без исходника), но код малочитаем: 1) некоторые блоки ручками соптимизированы, 2) весь код автоматически сгенерирован из другого описания, в котором все сигналы по-умолчанию 64-разрядные(и тп), 3) док нет, тк это просто один из экспериментов по поиску "оптимальной" архитектуры.

|

|

|

|

|

|

|

|

Sep 3 2014, 05:29 Sep 3 2014, 05:29

|

Знающий

Группа: Свой

Сообщений: 721

Регистрация: 23-10-08

Из: next to Odessa

Пользователь №: 41 112

|

Leka, если не трудно, то уточните. Цитата(Leka @ Sep 2 2014, 20:22)  Мои интересы сейчас - переход на более высокий уровень описания синхронных схем. Это по отношению к верилогу, или что-то другое? Цитата(Leka @ Sep 2 2014, 20:22)  По поводу простого ядра - могу выложить свое 5-летней давности ... Интересно было бы узнать его структурные данные. Цитата(Leka @ Sep 2 2014, 20:22)  весь код автоматически сгенерирован из другого описания... С одного HDL в другой? Цитата(Leka @ Sep 2 2014, 20:22)  ...это просто один из экспериментов по поиску "оптимальной" архитектуры. Какими будут критерии оптимальности? Меня еще интересует метод повышения быстродействия для стандартных инструкций для RISC-процессоров за счет конвейеризации. Где бы почитать об этом?

|

|

|

|

|

|

|

|

Sep 3 2014, 07:56 Sep 3 2014, 07:56

|

Профессионал

Группа: Участник

Сообщений: 1 075

Регистрация: 30-09-05

Пользователь №: 9 118

|

top.v - топ-модуль soc.v - ядро + uart + кнопки + светодиоды memA.v - RAM для CycloneV memX.v - RAM для Xilinx top.hex - код для загрузки ядра по uart (содержит служебную информацию) q.pas - тестовая программа (конструкции языка + N-ферзей) c.bat - запуск компилятора и симулятора compile.exe - компилятор (без каких-либо проверок синтаксиса и тп, winXP), создает top.hex core.exe - потактовый симулятор ядра (winXP), исполняет top.hex . sof.bat - вызывает jtag загрузчик и устанавливает параметры uart, надо поправить путь к top.sof и номер uart top.bat - компилирует программу и загружает код в ядро, надо поправить номер uart u.exe - выводит на экран поток из uart (u.c, winXP) Цитата(Serhiy_UA @ Sep 3 2014, 09:29)  Это по отношению к верилогу, или что-то другое? По отношению к верилогу. Цитата Какими будут критерии оптимальности?? Это целый опус писать надо, не сейчас.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|