| |

|

|

Ошибки работы Altium Designer 15 Ошибки работы Altium Designer 15, Только в версии 15 и выше! |

|

|

|

|

May 25 2016, 07:58 May 25 2016, 07:58

|

Местный

Группа: Свой

Сообщений: 301

Регистрация: 9-02-06

Пользователь №: 14 158

|

Цитата(Zlumd @ May 25 2016, 10:46)  Ну и вас также все via видны. И дорожки похоже что уже, чем самом деле. Вот уж... А так лучше? Сличайте :-)

Эскизы прикрепленных изображений

|

|

|

|

|

|

|

|

May 25 2016, 08:13 May 25 2016, 08:13

|

Местный

Группа: Свой

Сообщений: 327

Регистрация: 12-04-05

Из: Новосибирск

Пользователь №: 4 057

|

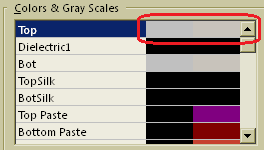

Цитата(Constantin @ May 25 2016, 13:58)  А так лучше? Сличайте :-) Я тоже сейчас выставил одинаковые цвета справа и слева. Но via все равно почему-то другого цвета. И размеры круглых и квадратных площадок разные, хотя на самом деле они одинаковые.

UPD. Добавил Multi-Layer.

Via стали серыми.

Но почему ? Какая здесь логика ? И почему все-таки толщина линий маленькая и круглые площадки меньше, чем надо ?

|

|

|

|

|

|

|

|

May 25 2016, 09:11 May 25 2016, 09:11

|

Местный

Группа: Свой

Сообщений: 405

Регистрация: 9-09-09

Из: Украина

Пользователь №: 52 262

|

Цитата(Владимир @ May 24 2016, 16:51)  Где надо --там и работают. Просто контроля нет применимости в правилах, где можно, где бессмысленно.

Хотя в последнем обновлении уже есть кнопочки Test Кнопочка это конечно хорошо. Но больше интересует вопрос КОГДА вернут или ВООБЬЩЕ вернут ли "полноценный" Query Builder как в 15 версии? Вопрос уже поднимался! Но...

--------------------

Om Shanti, Shanti, Shanti Om

|

|

|

|

|

|

|

|

May 25 2016, 09:20 May 25 2016, 09:20

|

Гуру

Группа: Модераторы

Сообщений: 11 653

Регистрация: 25-03-05

Из: Минск

Пользователь №: 3 671

|

Так он есть. Добраться к нему другой дорогой нужно В конце вsпадающего списка Cusom Query, а в последнем Query Builder. Река старым руслом не течет. Привыкайте Цитата(Uree @ May 25 2016, 12:13)  Медь-медь на слое - одно правило, медь-переходное - другое правило. Ну и зачем спрашивается? Все возможности дают. Есть в этом смысл, или нет - конечно вопрос.

|

|

|

|

|

|

|

|

May 25 2016, 18:27 May 25 2016, 18:27

|

Местный

Группа: Свой

Сообщений: 239

Регистрация: 5-02-06

Из: Подмосковье

Пользователь №: 14 012

|

Все ждал возможности опробовать в 16 версии учет длины дорожек внутри чипа. Разочарован.  Ожидал, что как и прежде Альтиум будет показывать в РСВ суммарную длину проводников цепи но теперь вместе с прибавкой от чипа. Показывает, но только для 2х выводной цепи. Если выводов в цепи более 2, то n/a, недоступно. Логику такого решения не понимаю. Зачем было городить огород?

--------------------

Автор благодарит алфавит за любезно предоставленные буквы.(С)

|

|

|

|

|

|

|

|

May 25 2016, 19:00 May 25 2016, 19:00

|

Гуру

Группа: Модераторы

Сообщений: 11 653

Регистрация: 25-03-05

Из: Минск

Пользователь №: 3 671

|

Цитата DDR3 адрес fly-by, подтяжка какая на цепи Извиняюсь тут точка- точка. От МС до первой IC памяти От МС до второй IC памяти Подтяжки должны быть исключены из учета длины. Или у вас собственные подходы? Цитата возможность использования другой микросхемы, у которой вместо гигабитной дифпары обычный сигнал Это как. При запайке другой микросхемы с другой задержкой у вас дорожки на PCB растянутся, чтобы подстроится под другую длину? Цитата Суммарную длину проводников Альтиум все равно сейчас показывает. Он это всегда показывал. И этого совершенно недостаточно было для DDR2, 3 и прочего.

|

|

|

|

|

|

|

|

May 25 2016, 19:28 May 25 2016, 19:28

|

Местный

Группа: Свой

Сообщений: 239

Регистрация: 5-02-06

Из: Подмосковье

Пользователь №: 14 012

|

Т.е. DDR через From-To? Тут я может не поспел за прогрессом, помню начинал, когда From-To еще не было, а DDR3 уже был.  Сейчас ими не пользуюсь. From-To учитывают чиповую добавку? Ну могу вспомнить, что в одном проекте гигабитная дифпара имела по 3 вывода в каждой цепи. Нормально, работает. Завтра на работе сделаю скриншот с 4 выводами. А вообще, это какая-то техническая сложность?

--------------------

Автор благодарит алфавит за любезно предоставленные буквы.(С)

|

|

|

|

|

|

|

|

May 25 2016, 19:38 May 25 2016, 19:38

|

Гуру

Группа: Модераторы

Сообщений: 11 653

Регистрация: 25-03-05

Из: Минск

Пользователь №: 3 671

|

Цитата(_Sergey_ @ May 25 2016, 22:28)  Т.е. DDR через From-To?

А вообще, это какая-то техническая сложность? Можно, но геморой еще тот. Поэтому и ввели этот механизм. Цитата From-To учитывают чиповую добавку? Нет Цитата Ну могу вспомнить, что в одном проекте гигабитная дифпара имела по 3 вывода в каждой цепи. Нормально, работает.

Завтра на работе сделаю скриншот с 4 выводами. Неважно сколько точек подключения. Важна задержка от источника к потребителю. Поэтому 2 точки Цитата а DDR3 уже был Я еще с DDR3 не работал, а были проекты где нужно было учитывать с более жесткими требованиями, чем в DDR Excell все считал. Скрипты писали люди. Теперь одним геморроем стало меньше. За эту фичу спасибо. ЕЕ давно не хватало. Цитата скриншот с 4 выводами Зачем эти скриншоты. Давайте ссылки на стандарты или рекомендации производителей, где они требую учитывать задержки микросхем от более 2 источников для учета задержек в топологии

|

|

|

|

|

|

|

|

May 26 2016, 03:37 May 26 2016, 03:37

|

Местный

Группа: Свой

Сообщений: 327

Регистрация: 12-04-05

Из: Новосибирск

Пользователь №: 4 057

|

Жму Cancel, а AD продолжает, как будто я OK нажал. Хочу обновить все футпринты. Выбираю PCB->Tools->Update From PCB Libraries->Update All Footprints(Create ECO)->Execute Changes

И тут я передумал и жму Cancel. А AD все равно обновляет все футпринты.

|

|

|

|

|

|

|

|

2 чел. читают эту тему (гостей: 2, скрытых пользователей: 0)

Пользователей: 0

|

|

|