| |

|

|

Прошу дать оценку 8 layer StackUp-у Прошу дать оценку 8 layer StackUp-у, Zynq, DDR3 |

|

|

|

|

Aug 12 2016, 13:33 Aug 12 2016, 13:33

|

Частый гость

Группа: Свой

Сообщений: 105

Регистрация: 10-03-08

Из: Helsinki

Пользователь №: 35 763

|

Цитата(Uree @ Aug 12 2016, 19:20)  Так а что с корпусом? Ах да, пропустил. FBG484. Цитата ЗЫ Так параметры меди мощно разные на картинках от Полара и Сатурна - раз, и Сатурн не учитывает маску - два.

В общем порядок величины Сатурн конечно показывает, но верить могу только Полару. Да нет же - одинаковы. Base copper weight в сатурне 0.053мм, T1 в поляре - 0.053. Или я не прав? Ну да ладно, раз поляру больше веры - я последую вашему примеру. Цитата картинка ни о чем.

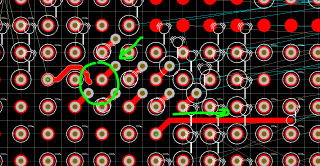

На верхнем слое выводятся сигналы с краю от минросхемы, а не от центра. А для вас не очевидно, что если тянуть от центра, то будет то же самое? Ну может так понятней будет (см. аттач). Если и сейчас скажите, что выйгрыша нет, то я решу, что вы издеваетесь. upd. а, я понял о чем вы. Ну, а теперь есть возможность тянуть и от центра, так что - выйгрыш есть. Ладно, закроем уже вопрос via-in-pad, поскольку вроде бы разобрались: стоимость возрастает относителньо не значительно, проблем с монтажом BGA в виде утекания припоя нет, места чуть больше.

Сообщение отредактировал UnDerKetzer - Aug 12 2016, 13:41

Эскизы прикрепленных изображений

РЈРСВеньшено Р В РўвЂР  С• 82%

965 x 498 (78.84 килобайт)

|

|

|

|

|

|

|

|

|

Aug 12 2016, 13:44 Aug 12 2016, 13:44

|

Гуру

Группа: Модераторы

Сообщений: 11 653

Регистрация: 25-03-05

Из: Минск

Пользователь №: 3 671

|

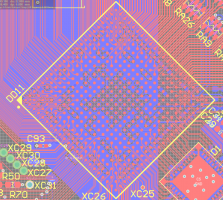

Считайте, что издеваюсь. Дайте картинку, как выводите НАРУЖУ, а не ВНУТРИ. Внутри обычно питания и масса неиспользуемых выводов. Сигнальные там на внутренних слоях вытягиваются. На внутренних без разницы, так как количество отверстий от этого не меняется Вот, все вытянуто на верхнем слое

Эскизы прикрепленных изображений

РЈРСВеньшено Р В РўвЂР  С• 84%

1067 x 960 (190.51 килобайт)

|

|

|

|

|

|

|

|

|

Aug 12 2016, 13:48 Aug 12 2016, 13:48

|

Знающий

Группа: Свой

Сообщений: 771

Регистрация: 24-04-08

Из: Зеленоград

Пользователь №: 37 056

|

Цитата(UnDerKetzer @ Aug 12 2016, 16:16)  Дорожка 0.2 (контроль импеданса), виасы 0.2/0.4, провести трассу DQ3 под BGA на топе невозможно (цифра 1), а в случае использования via-in-pad линию DQ2 - возможно. Может я чего-то не понимаю, конечно, но выглядит как шило на мыло. Так бы в ТОР вышли первые два ряда, а следующие через dog bone и далее во внутренних. А тут наоборот - первые во внутренних, задние в TOP. Суммарно по слоям одно и то же. PROFIT в том, чтобы вытащить дальний ряд именно в TOP? Цитата(Uree @ Aug 12 2016, 16:44)  Ваш случай делается в 8-ми слоях и без ВИП: +1 Переходные в падах и микровиа для этой задачи стоит использовать только в случае, если хочется опыта набраться за счёт работодателя.

|

|

|

|

|

|

|

|

Aug 12 2016, 14:07 Aug 12 2016, 14:07

|

Частый гость

Группа: Свой

Сообщений: 105

Регистрация: 10-03-08

Из: Helsinki

Пользователь №: 35 763

|

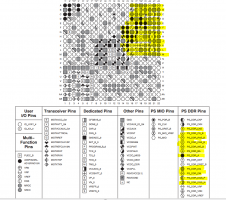

Цитата(Владимир @ Aug 12 2016, 19:44)  Считайте, что издеваюсь.

Дайте картинку, как выводите НАРУЖУ, а не ВНУТРИ.

Внутри обычно питания и масса неиспользуемых выводов. Сигнальные там на внутренних слоях вытягиваются. Вот именно, что обычно. Вот распиновка, взгляните на пин-аут ДДР контроллера - все собрано в кучу и занимает весь правый верхний квадрант чипа. Оттуда выводить хочется не только по двум внутренним сигнальным слоям, но и по внешним. А чтобы вытянуть по внешним, нужен контроль импеданса 40Ом, а с препрегом в 0.1мм это ширина трассы 0.27мм! Её не вытянуть и с via-in-pad, не говоря о dog-bone. И как решать эту коллизию с импедансом я вообще не представляю... С одной стороны - тоньше препрег нельзя, с другой - линии по TOP и BOT не тянутся, поскольку толстенные. Цитата На внутренних без разницы, так как количество отверстий от этого не меняется Абсолютно справедливо. Цитата Вот, все вытянуто на верхнем слое А ширина трассы какая? Видимо, 0.1, коль скоро между падами по две линии аж протянуто. И каков импеданс у линии? 70Ом? Uree, Владимир, Corvus, господа, да я уверен, что все разводится в 8 слоях. Мне лишь непонятно - как именно. Ведь если 4 плейна, то остается 4 слоя. Внешние не подходят, поскольку оттуда не вытянуть такую толстую трассу, остается 2 внутренних слоя для всех линий (dq, dqs, addr, clock, ctrl).

Сообщение отредактировал UnDerKetzer - Aug 12 2016, 14:07

Эскизы прикрепленных изображений

РЈРСВеньшено Р В РўвЂР  С• 84%

1058 x 937 (273.24 килобайт)

|

|

|

|

|

|

|

|

|

Aug 12 2016, 14:11 Aug 12 2016, 14:11

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Материал FR-4 даже от разных производителей имеет практически одинаковую сетку толщин диэлектрика, фольги и препрегов. Т.е., конечно, у разных производителей есть свои особенные продукты - у кого-то дополнительно есть очень тонкие ядра, но основная сетка толщин (0.1, 0.15, 0.2, 0.25, 0.3, 0.51, 0.71 и т.д.) а также меди (0.018, 0.035, 0.070, 0.105) - есть всегда. Толщина- конечно, и плетение тоже. А вот Dk, Df, CTE и еще кое чего до кучи- совсем нет. Не поверите, даже пара из этого списка влияет на дизайн похлеще чем толщина. Цитата Уже сказано - неверный это подход. Нужно стараться делать максимально унифицированно, чтобы любой приличный завод мог изготовить плату. А то наладите производство, а цеха сгорят, или закроется фирма, и что - финита ля, поскольку никто больше не может изготовить по вашим требованиям? Неверный подход предлагаете именно вы- он противоречит здравому смыслу: любой стек всегда нужно уточнять у конкретного производства. Всегда  А вы чушь несете какую-то. Цитата Опять 25. Да, именно это я и хочу сказать.

Специально для вас - смотрите аттач.

Дорожка 0.2 (контроль импеданса), виасы 0.2/0.4, провести трассу DQ3 под BGA на топе невозможно (цифра 1), а в случае использования via-in-pad линию DQ2 - возможно. Я в принципе понимаю вашу идею на этом скриншоте, однако поддерживаю комментарии Uree, Владимир-а и Corvus отписавшихся на эту тему. Ну и по правде говоря сильно попахивает сферическим дизайном в вакууме. Ну и длина догбона тоже отдельная тема для разговора. Цитата Есть в ваших словах истина, но 10 слоев для разводки DDR3 - жирновато... Как-то же упихивают в 4 слоя с контролем импеданса?!.. Да можно и 2 при желании и соответствующем дизайне(ключевой момент)- и также будут соблюдены все констрейны. В вашем случае все зависит от того что за компоненты вокруг и как они упакованы- но в целом 8 слоев это нормальный старт. Но не потолок. Цитата Вот именно, что обычно. Вот распиновка, взгляните на пин-аут ДДР контроллера - все собрано в кучу и занимает весь правый верхний квадрант чипа. Оттуда выводить хочется не только по двум внутренним сигнальным слоям, но и по внешним. А зачем? С учетом частот на которых гоняется ваша память, используйте neck-и, как сказал Uree если не можете нормально вывести. Но все равно мне кажется что с расчетами у вас что-то не так. Ну выведете вы один проводник из центра при VIP- ну и что? Там до кучи еще добра которое надо выводить, целиком эту проблемы вы не решите этой технологией. Тут либо пересматривать нормы, либо расстановку компонентов.

|

|

|

|

|

|

|

|

Aug 12 2016, 14:27 Aug 12 2016, 14:27

|

Гуру

Группа: Модераторы

Сообщений: 11 653

Регистрация: 25-03-05

Из: Минск

Пользователь №: 3 671

|

Цитата(UnDerKetzer @ Aug 12 2016, 17:07)  А ширина трассы какая? Видимо, 0.1, коль скоро между падами по две линии аж протянуто. да Цитата И каков импеданс у линии? 70Ом? Там нет DDR Только дифпары Но не в этом дело. просто как пример вывода на внешнем слое

|

|

|

|

|

|

|

|

Aug 12 2016, 14:27 Aug 12 2016, 14:27

|

Частый гость

Группа: Свой

Сообщений: 105

Регистрация: 10-03-08

Из: Helsinki

Пользователь №: 35 763

|

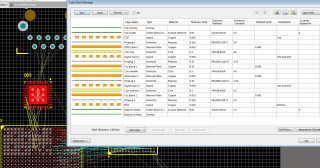

Цитата(EvilWrecker @ Aug 12 2016, 20:11)  Толщина- конечно, и плетение тоже. А вот Dk, Df, CTE и еще кое чего до кучи- совсем нет. Не поверите, даже пара из этого списка влияет на дизайн похлеще чем толщина. Отчасти согласен. И кстати вы правы - не поверю. Проверил: разброс 25% толщины дает импеданс 39.7-53.7, т.е. дельта 14 Ом. Разброс 25% Dk дает импеданс 43.3-52.5, т.е. дельта 9.2 Ом. Но влияние серьезное, это факт. Цитата Неверный подход предлагаете именно вы- он противоречит здравому смыслу: любой стек всегда нужно уточнять у конкретного производства. Всегда  А вы чушь несете какую-то. Опять же, согласен от части. Но ведь верно также и то, что 100% закладываться на исключительно одного производителя - тоже не вполне разумно. Цитата Я в принципе понимаю вашу идею на этом скриншоте, однако поддерживаю комментарии Uree, Владимир-а и Corvus отписавшихся на эту тему. Ну и по правде говоря сильно попахивает сферическим дизайном в вакууме. Вы правы. Ладно, если вы не против, закрываем вопрос с via-in-pad, и возвращаемся к стек-апу. Я его пересмотрел и согласовал с Резонитом. По-прежнему получаю для трассы 40 Ом на внешнем слое ширину проводника 0.28 - как обойти проблему? Цитата Да можно и 2 при желании и соответствующем дизайне(ключевой момент)- и также будут соблюдены все констрейны. В вашем случае все зависит от того что за компоненты вокруг и как они упакованы- но в целом 8 слоев это нормальный старт. Но не потолок.

А зачем? С учетом частот на которых гоняется ваша память, используйте neck-и, как сказал Uree если не можете нормально вывести. Но все равно мне кажется что с расчетами у вас что-то не так. Спасибо. Видимо, буду использовать neck-и, хотя и ОЧЕНЬ не хочется: дело в том, что в литературе я не встречал описания влияния neck-ов на сигнал, выраженного в цифрах, и для меня neck - неоднородность с неясными характеристиками. Да, я интуитивно отдаю себе отчет в том, что три-четыре neck-а влиять критично не должны, но... По поводу расчетов: ну не знаю... Проверял несколько раз. Взгляните, если не трудно, может что-то увидите (аттач). Владимир, если бы речь шла об 0.1/0.1, проблемы бы вовсе не было - это трассируется легко. Меня тревожит именно случай с ddr3, где есть требования к импедансу, а импеданс достижим лишь толстенными трассами, поскольку лимит по толщине препрега я уже выработал. Господа, прошу взглянуть на стек-ап: были внесены правки на основании дискуссии, а также он был предварительно согласован с технологом. Стало ли лучше?

Сообщение отредактировал UnDerKetzer - Aug 12 2016, 14:34

Эскизы прикрепленных изображений

РЈРСВеньшено Р В РўвЂР  С• 89%

1467 x 768 (102.45 килобайт)

|

РЈРСВеньшено Р В РўвЂР  С• 84%

1040 x 707 (61.81 килобайт)

|

|

|

|

|

|

|

|

|

Aug 12 2016, 14:37 Aug 12 2016, 14:37

|

ядовитый комментатор

Группа: Свой

Сообщений: 2 765

Регистрация: 25-06-11

Пользователь №: 65 887

|

Цитата Отчасти согласен. И кстати вы правы - не поверю.

Проверил: разброс 25% толщины дает импеданс 39.7-53.7, т.е. дельта 14 Ом.

Разброс 25% Dk дает импеданс 43.3-52.5, т.е. дельта 9.2 Ом.

Но влияние серьезное, это факт. Оно и понято- при ваших цифрах разбег сопоставим или больше технологического разброса по контролю целевого импеданса. В лотерею играете то есть  Цитата Опять же, согласен от части. Но ведь верно также и то, что 100% закладываться на исключительно одного производителя - тоже не вполне разумно. А это вообще говоря неизбежно в определенном смысле- единственное что хорошо в вашем случае, так это факт того что требуемые цифры в вашей плате можно набрать довольно большой комбинацией материалов. Цитата Спасибо. Видимо, буду использовать neck-и, хотя и ОЧЕНЬ не хочется: дело в том, что в литературе я не встречал описания влияния neck-ов на сигнал, выраженного в цифрах, и для меня neck - неоднородность с неясными характеристиками. Да, я интуитивно отдаю себе отчет в том, что три-четыре neck-а влиять критично не должны, но... А вы их длинными не делайте(только в области фанаутов у бга) и сами трассы держите короче. Для ваших скоростей это ничто. Вот если бы был Zynq Ultrascale(MPSOC+) c DDR4, то другое дело совсем. А какие цифры Резонит дает для 50 Ом?

|

|

|

|

|

|

|

|

Aug 12 2016, 15:34 Aug 12 2016, 15:34

|

Частый гость

Группа: Свой

Сообщений: 105

Регистрация: 10-03-08

Из: Helsinki

Пользователь №: 35 763

|

Цитата(ClayMan @ Aug 12 2016, 21:16)  На картинке стэка тощина фольги VCC слоя 0.35 - думаю стоит поправить)

Ну и на картинке расчета импеданса подтрав аж 130 мкм, если не ошибаюсь - как-то уж очень круто) Ой, точно, ноль забыл. Подтрав сделал 50%, пожалуй, можно и поменьше. Впрочем, мало влияет на импеданс. Спасибо!

|

|

|

|

|

|

|

|

Aug 12 2016, 18:40 Aug 12 2016, 18:40

|

Гуру

Группа: Модераторы

Сообщений: 11 653

Регистрация: 25-03-05

Из: Минск

Пользователь №: 3 671

|

Что вы маетесь. Закажите расчет на заводе. многие делают это бесплатно для потенциальных заказчиков. Например тут для технологии только со сквозными отверстиями, а тут напишите, что вам надо и вам рассчитают, для применяемых у них материалов. Но лучше сразу на тот завод, с которым вы работаете. Там учтут и с учетом прессования и прочих технологических уловок для выдержки нужного волнового сопротивления.

|

|

|

|

|

|

|

|

Aug 15 2016, 13:41 Aug 15 2016, 13:41

|

Частый гость

Группа: Свой

Сообщений: 105

Регистрация: 10-03-08

Из: Helsinki

Пользователь №: 35 763

|

to EvilWreckerЦитата А вы их длинными не делайте(только в области фанаутов у бга) и сами трассы держите короче. Для ваших скоростей это ничто. Вот если бы был Zynq Ultrascale(MPSOC+) c DDR4, то другое дело совсем. Посмотрим, быть может, проще пойти на компромисс с волновым: задаться 45-ю омами и тянуть без неков вовсе. Кстати, коль скоро вы упомянули: как же тогда решается трассировка Ultrascale с DDR4 в таком случае? Тупо количеством слоев? Цитата(Владимир @ Aug 13 2016, 01:40)  Что вы маетесь. Закажите расчет на заводе. многие делают это бесплатно для потенциальных заказчиков. Например тут для технологии только со сквозными отверстиями, а тут напишите, что вам надо и вам рассчитают, для применяемых у них материалов. Но лучше сразу на тот завод, с которым вы работаете. Там учтут и с учетом прессования и прочих технологических уловок для выдержки нужного волнового сопротивления. Да, вероятно, вы правы, этот путь оптимален. Спасибо. И спасибо всем ответившим, искренне признателен за критику, советы и наставления. Владимир, вопрос к вам как к модератору: можно ли будет в этой же теме попросить покритиковать саму трассировку, или же лучше следует создать новый топик?

Сообщение отредактировал UnDerKetzer - Aug 15 2016, 13:44

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|