Всем добрый день! Имеем Cyclone V (обычный, без SOC) + Quartus 14.0 + QuestaSim.

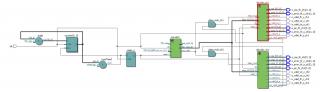

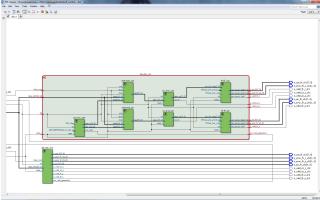

Собрал проект цифрового понижающего преобразователя (digital down converter) из альтеровских IP ядер (NCO, умножитель, FIR фильтр) и с opencores (CIC фильтр). Система двухканальная. В самом начале идет логика автоматического сброса (далее сброс будет приходить с процессора)

РЈРСВВВеньшено Р В Р’В Р СћРІР‚ВВР С• 89%

1550 x 445 (117.42 килобайт)

|

Отдельно DDC, собранный из IP ядер.

РЈРСВВВеньшено Р В Р’В Р СћРІР‚ВВР С• 90%

1680 x 1050 (277.81 килобайт)

|

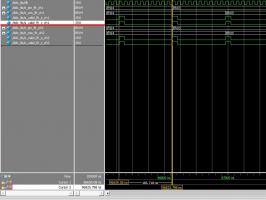

Данные с ПЛИС по последовательному порту идут в DSP. Под выходные данные с ПЛИС идет строб, который я вывожу на контрольные точки.

РЈРСВВВеньшено Р В Р’В Р СћРІР‚ВВР С• 81%

900 x 676 (114.35 килобайт)

|

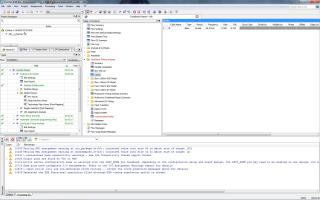

В SDC файл прописываю свой клок, равный 60 МГц.

РЈРСВВВеньшено Р В Р’В Р СћРІР‚ВВР С• 90%

1680 x 1050 (390.09 килобайт)

|

В Warning присутствуют следующие предупреждения:

1)Unconstrained output ports

РЈРСВВВеньшено Р В Р’В Р СћРІР‚ВВР С• 78%

760 x 625 (102.75 килобайт)

|

2)4 сигнала строба:

Missing drive strength and slew rate

РЈРСВВВеньшено Р В Р’В Р СћРІР‚ВВР С• 78%

789 x 699 (104.59 килобайт)

|

Все остальные выходные информационные сигналы я вывожу на виртуальные пины, чтобы не мешались. В будущем они пойдут в DSP.

При загрузке в ПЛИС стробы не идут - на контрольных точках висит высокий уровень.

Буду признателен, если подскажете, как избавиться от варнингов.