| |

|

|

Графический TFT LCD с параллельной шиной и 18-битным цветом. Помогите запустить Графический TFT LCD с параллельной шиной и 18-битным цветом. Помогите запустить, Есть три модели от Sharp, Nec и U.R.S. у всех разные тайминги. |

|

|

|

|

Mar 14 2008, 18:38 Mar 14 2008, 18:38

|

Профессионал

Группа: Свой

Сообщений: 1 817

Регистрация: 14-02-07

Из: наших, которые работают за бугром

Пользователь №: 25 368

|

Народ подскажите пожалуйста, кто сталкивался с реализацией интерфейса от процессора к таким LCD. То есть есть видеобуффер с 18-битным цветом. И я делаю на FPGA реализацию низкоуровнего интерфейса, который бы с определнным Фреймрейтом(60FPS) запихивал его в LCD. Прикол в том, что есть два последних дисплея из вышеупомянутого списка и спецификация от Шарпа на такой же дисплей.

Все дисплеи имеют абсолютно одинаковую распиновку, разрешение 320х240, по 6 бит на цвет и одинаковые и как я понял стандартные сигналы VSYNC, HSYNC, DATA_ENABLE, CLK, R/L, U/D.

С двумя последними вроде все понятно - они определяют направление развертки и по идее просто цепляются к соответсвующим напряжениям питания.

Но со всеми остальными полная фигня.

Во первых я так и не понял - в двух моделях описано два возможных режима работы FIXED и DE. Второй вроде как упрощенный - только DE, но почему-то в одном дисплее используется сигнал VSYNC, а в другом просто DE должен быть длинней и это вроде как начало кадра.

Во вторых у всех FIXED Mode вроде как одинаковый, но у каждого свои тайминги для VSYNC и HSYNC и свои количества холостых линий и пикселей - у одного 50 линий после VSYNC, у другого 37, у трeтьего 74, то есть при всей своей одинаковости - заменить один дисплей на другой без изменения программы нельзя - картинка просто будет сдвинута. Также в этом режиме одному нужен DE, другой только без DE работает а в третьем можно и так и так - DE определяет начало рабочих данных.

Ну и что вообще меня убило, что у них разная полярность сигнала DE и что самое прикольное фазировка CLK! У одного синхрoнизация по спаду у другого по фронту!

В общем я офигел, причем все пишут что базируются на одной спецификации от Sharpa.

В итоге 2 дня мудохаюсь, на одном дисплее всякие полоски мигают. Другой просто черный.

Помогите разобраться плиз - все таки надо этот FIXED режим реализовывать или как то еще их можно запустить?

|

|

|

|

|

|

|

|

Mar 16 2008, 03:59 Mar 16 2008, 03:59

|

Частый гость

Группа: Свой

Сообщений: 142

Регистрация: 18-02-08

Из: Челябинск

Пользователь №: 35 141

|

Цитата(syoma @ Mar 14 2008, 23:38)  Во первых я так и не понял - в двух моделях описано два возможных режима работы FIXED и DE. Второй вроде как упрощенный - только DE, но почему-то в одном дисплее используется сигнал VSYNC, а в другом просто DE должен быть длинней и это вроде как начало кадра. Все сигналы действительно стандартные, активный уровень сигнала DataEnable всегда соответствует активной части строк в активной части кадра, это инверсия сигнала BLANK - гашения информации. Частенько в документации на панели встечается примечание, что если DE имеет постоянный (высокий или низкий) уровень, дисплей будет черным, с некоторым мерцанием. Стандартно, импульсы строчной и кадровой синхронизации должны находится внутри интервалов гашения, не суть важно где именно, какое-то изображение, пусть со сдвигом, Вы все равно должны получить.

|

|

|

|

|

|

|

|

Mar 16 2008, 06:44 Mar 16 2008, 06:44

|

Местный

Группа: Свой

Сообщений: 210

Регистрация: 15-01-08

Из: Новосибирск

Пользователь №: 34 105

|

Цитата(syoma @ Mar 15 2008, 00:38)  на одном дисплее всякие полоски мигают. Другой просто черный. Тот у которого хоть что-то есть на экране - перспективен для дальнейшей отладки. Скорее всего там надо упорядочить частоты. А лучше, если бы Вы написали какой конкретно дисплей мучаете, схему и алгоритм (прогу).

--------------------

Я здесь и сейчас...

|

|

|

|

|

|

|

|

Mar 16 2008, 12:15 Mar 16 2008, 12:15

|

Профессионал

Группа: Свой

Сообщений: 1 817

Регистрация: 14-02-07

Из: наших, которые работают за бугром

Пользователь №: 25 368

|

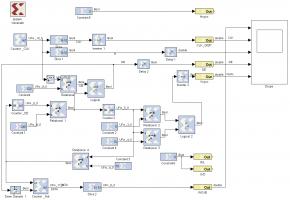

Тот, что черный - NEC3224BC35-22. 5.5" QVGA дисплей. Как раз мне он кажется более многообещающим с точки зрения отладки, так как он работал на демонстрационной плате. Второй - я считаю noname, так как фирма непонятная - U.R.T и даташит непонятный. К сожалению посмотреть осциллограмы рабочей платы я не могу, так как демо-прогу просто стерли и теперь не знают где искать. Но насколько я понял моя ошибка в том, что я понадеялся на режим DE, а его не надо испльзовать, а нужны все сигналы и горизонтальной и вертикальной синхронизации. Если так, то моя прога в System Generatore однозначно неправильная. Просто могу описать как она работает, если получится. За оптимизацию прошу не пинать

Р В Р’ВВВВВВВВзображенРСвЂВВВВВВВР В Р’Вµ СѓРСВВВВВВВВеньшено

(38.21 килобайт)

|

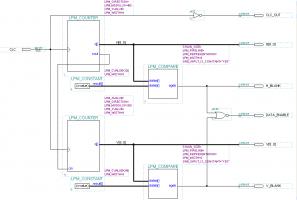

Счетчик Counter_CLK считает с частотой 12Мгц до 800, т.к самый младший бит счетчика используется как клок CLK, то получается, что CLK имеет частоту 6Мгц и счетчик как раз отсчитывает 400 клоков, что составляет длину одной линии (320+холостые клоки).

Р В Р’ВВВВВВВВзображенРСвЂВВВВВВВР В Р’Вµ СѓРСВВВВВВВВеньшено

(19.72 килобайт)

|

Дальше стоит компаратор, который выдает 1 если значение счетчика менее 320. Это генерация сигнала DE. Логика И после этого служит для блокирования сигнала DE, во время импульса вертикальной синхронизации и чтобы количество DE импульсов соответствовало 240. Для єтого стоит счетчик Counter_DE, который считает с частотой 1/(CLK*400), т.е. с частотой вертикальной развертки. Если значение счетчика менее 240 строк, сигнал DE генерируется, иначе запускается Counter2, который считает с такой же частотой как и предыдущий счетчик(нахрена тогда этот счетчик нужен? Вопрос самому себе).

Р В Р’ВВВВВВВВзображенРСвЂВВВВВВВР В Р’Вµ СѓРСВВВВВВВВеньшено

(34.77 килобайт)

|

Выход этого счетчика с помощью компараторов генерирует сигнал VSYNC, который начинается за 5 строк после окончания генерации DE, длится 5 строк, и еще 5 строк ничего не происходит. Затем он сбрасывает счетчик строк. Т.о. длительность вертикальной развертки составляет 240+5+5+5=255строк. Счетчик Counter_Adr, используется как счетчик адреса в видеобуфере, и инкрементируется с частотой клока. Он инкрементируется, только если DE активный, то есть, когда выводятся правильные данные. Дальше должен быть сам буффер, но я просто подал выход счетчика на выход данных. Т.о я ожидал увидеть стабильные цветные полосы, или что-то похожее на это. Всякие Delays служат для синхронизации клока, данных и DE по фронтам. Инвертированный сигнал - Vsync - это уже следствие экспериментов.

Р В Р’ВВВВВВВВзображенРСвЂВВВВВВВР В Р’Вµ СѓРСВВВВВВВВеньшено

(39.15 килобайт)

|

Я так понял, что проблема в Vsync - то что его просто нема. Еще вопрос. Осцик показывает фронты по 30-40 нс - это очень плохо? Просто линии связи сейчас порядка 50см. Дисплей с такой длинной проводов будет работать?

|

|

|

|

|

|

|

|

Mar 16 2008, 17:51 Mar 16 2008, 17:51

|

Частый гость

Группа: Свой

Сообщений: 142

Регистрация: 18-02-08

Из: Челябинск

Пользователь №: 35 141

|

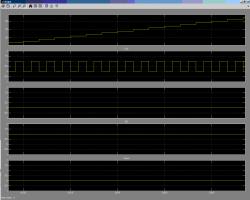

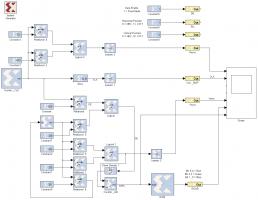

Я с Xilinx’ом не работал, приведу очень простой пример дизайна для Altera. Девятиразрядный счетчик по модулю 400 формирует строчный интервал ( 320 тактов активной части строки + 80 тактов гасящий интервал). Строчный гасящий импульс формируется компаратором по условию H[8..0] больше или равно 320. Совершенно аналогично формируется кадровый интервал. Сигнал DATA_ENABLE формируется элементом ИЛИ-НЕ из строчного и кадрового гасящих импульсов ( выведены на внешние контакты для наглядности). В качестве сигнала CLC для LCD панели используется прямой или инвертированый системный CLC ( учитываем, что смена адреса H[8..0], V[8..0] происходит синхронно по фронту CLC). Если панели действительно нужны сигналы HS и VS, каждый из них можно сформировать одинаковой схемой из двух компараторов, сравнивающих значение счетчика с константами начального и конечного положения импульса, и RS-триггера, включаемого первым компаратором и выключаемого вторым. Замечу, что в общем случае, адрес для экранной памяти формируется отдельным счетчиком, счет которого приостанавливается на время гасящих интервалов, что позволяет использовать ровно столько памяти, сколько занимает активная часть изображения. В данном случае, это было бы актуально для изображения 320 х 200 = 64000 ( 64К памяти) против 512 х 256 ( 128К ), а для 320 х 240 = 76800 все равно придется использовать память длиной 128К, так что можно формировать адрес прямо из H[8..0], V[7..0].

Эскизы прикрепленных изображений

Р В Р’ВВВВВВВВзображенРСвЂВВВВВВВР В Р’Вµ СѓРСВВВВВВВВеньшено

(15.33 килобайт)

|

|

|

|

|

|

|

|

|

Mar 16 2008, 21:48 Mar 16 2008, 21:48

|

Частый гость

Группа: Свой

Сообщений: 142

Регистрация: 18-02-08

Из: Челябинск

Пользователь №: 35 141

|

Цитата(syoma @ Mar 16 2008, 23:09)  Спасибо. Но эта схема с работающего дизайна или просто пример?

Действительно можно обойтись без H_SYNC и V_SYNC?

Я у себя заметил еще, что H_SYNC всегда имел низкий уровень, что похоже наверняка свело с ума контроллер LCD.

А по памяти - у меня будет использоваться Xilinxовская встроенная BRAM. а цветов будет всего 64, и тут получится ровно 76800*6 бит. Именно столько синтезатор и возъмет. Да, это рабочая схема для Toshiba LTM210 (640х480), только значения подставлены другие, под Ваш пример. Там входов HS и VS нет вообще, а обойдется ли без них Ваша панель...

|

|

|

|

|

|

|

|

Mar 17 2008, 18:41 Mar 17 2008, 18:41

|

Частый гость

Группа: Свой

Сообщений: 142

Регистрация: 18-02-08

Из: Челябинск

Пользователь №: 35 141

|

Цитата(syoma @ Mar 17 2008, 14:26)  То есть я так понял, что вы работаете в DE режиме. К сожалению, у меня из 4-х документаций этот режим описан только в 2-х и то - в одной панели нужен VSYNC, а в другой - нет - как у вас.

Поэтому я на него рассчитывать не могу, а буду делать обычный FIXED режим. Я работаю в разных режимах, в частности, проекционные матрицы требуют формирования существенно более сложного набора сигналов, но тем не менее, все решаемо. А насчет HS и VS, как я уже говорил, требуется очень простое дополнение к приведенной схеме: Цитата Если панели действительно нужны сигналы HS и VS, каждый из них можно сформировать одинаковой схемой из двух компараторов, сравнивающих значение счетчика с константами начального и конечного положения импульса, и RS-триггера, включаемого первым компаратором и выключаемого вторым. Или требуется это нарисовать?

|

|

|

|

|

|

|

|

Mar 17 2008, 19:13 Mar 17 2008, 19:13

|

Профессионал

Группа: Свой

Сообщений: 1 817

Регистрация: 14-02-07

Из: наших, которые работают за бугром

Пользователь №: 25 368

|

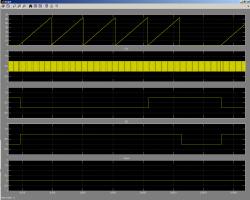

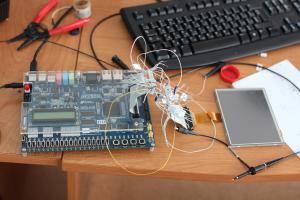

Не надо, заработало. Но почему-то на моих длинных проводах один дисплей показывает картинку с конкретными искажениями - то есть наложения текста или копии текста в разных цветах, все конкретно сдвинуто и т.д. А второй показывает нормально. И есть у меня демонстрационная плата, куда можно дисплей прямо втыкнуть коротким шлейфом - там оба дисплея показывают нормально. Похоже проблема с длиной проводов была. Осцик показывает конкретно заваленые фронты, но я знаю что он брешет, потому что щуп только до 10Мгц и то же самое показывал, когда дисплеи напрямую к плате присоединялись. Схема получилась обычная - с двумя счетчиками и компараторами на H_SYNC, V_SYNC и внутренний DE. Внешний, как оказалось никому не нужен. Только при этом пришлось точно подогнать длину строки 404 клока и длину фрейма - 262 строки. Это почему-то точно задано. Нафига тогда H_SYNC?. Ну и естественно сдвиг картинки подогнать.

Р В Р’ВВВВВВВВзображенРСвЂВВВВВВВР В Р’Вµ СѓРСВВВВВВВВеньшено

(46.82 килобайт)

|

Теперь дело за Линухом и Microwindows. Интересно, хватит ли производительности Microblaze на 50МГц это все отрисовывать? Может что хорошее посоветуете для GUI?

|

|

|

|

|

|

|

|

Apr 13 2018, 13:23 Apr 13 2018, 13:23

|

Частый гость

Группа: Участник

Сообщений: 191

Регистрация: 18-09-12

Из: Орёл

Пользователь №: 73 591

|

РЈРСВВВВВВВВеньшено Р В Р’В Р СћРІР‚ВВВВВВВР С• 94%

2592 x 1728 (1.2 мегабайт)

|

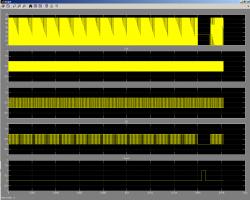

Позвольте продолжить тему. Сейчас только начинаю осваивать и верилог и подключение таких дисплеев.  OSD057VA01CT_V0.4__With_Touch_.pdf

OSD057VA01CT_V0.4__With_Touch_.pdf ( 390.22 килобайт )

Кол-во скачиваний: 28Имею плату DE2-115 от альтеры (точнее терасик). Пишу на верилоге. Имею дисплей OSD057VA (даташит во вложении) Подскажите, сигналы vsync и hsync когда в 1, а когда в 0 ? И то же самое про сигнал DE. Как я понял, лучше перевести дисплей в режим sync ( не de-оnly). Правильно? Код модуля на верилоге: Код module osdDisplaySimple (input clkPin, input adjVal, output reg pixPin, output reg HYNC_PIN, output reg VSYNC_PIN, output reg dePin, output reg ledAdjPin, output refOutPin);

integer pixCnt;

integer lineCnt;

integer frameCnt;

integer ledAdjCnt;

integer deLogic;

assign refOutPin = clkPin;

initial

begin

ledAdjCnt = 0;

pixCnt = 0;

lineCnt = 0;

frameCnt = 0;

HYNC_PIN = 0;

VSYNC_PIN = 0;

dePin = 0;

ledAdjPin = 0;

end

always @(posedge clkPin)

begin

ledAdjCnt = ledAdjCnt + 1;

if(ledAdjCnt > 1250)

begin

ledAdjCnt = 0;

ledAdjPin = ~ledAdjPin;

end

pixPin = ~pixPin;

// Pixels block

pixCnt = pixCnt + 1;

if(pixCnt < 640*2)

HYNC_PIN = 1;

else if(pixCnt < 800*2)

HYNC_PIN = 0;

else

begin

HYNC_PIN = 0;

pixCnt = 0;

lineCnt = lineCnt + 1;

if (lineCnt < 480)

VSYNC_PIN = 1;

else if(lineCnt < 525)

VSYNC_PIN = 0;

else

begin

VSYNC_PIN = 0;

lineCnt = 0;

end

end

dePin = HYNC_PIN & VSYNC_PIN;

end

endmodule топ-модуль: Код module top(

input wire [17:0] SW,

input wire [3:0] KEY,

input wire OSC_50,

output wire [7:0] LED_GREEN,

output wire [6:0] HEX0,

output wire [6:0] HEX1,

output wire [6:0] HEX2,

output wire [6:0] HEX3,

output wire [35:0] GPIO,

output wire UART_TXD,

output wire [17:0] LED_RED

);

integer samples[1024];

integer sampCnt1;

integer sampCnt2;

integer cnt;

integer cntClk;

integer trig;

integer unitCnt;

//module osdDisplaySimple (clkPin, adjVal, pixPin, HYNC_PIN, VSYNC_PIN, dePin, ledAdjPin, refOutPin);

osdDisplaySimple Simple (OSC_50, SW[3], GPIO[33], GPIO[1],GPIO[2], GPIO[3], GPIO[4], GPIO[11]);

// RED color

assign GPIO[32] = SW[0];

// GREEN color

assign GPIO[6] = SW[1];

// BLUE color

assign GPIO[5] = SW[2];

// DMS

assign GPIO[0] = SW[4];

endmodule всё равно не работает.... В какой полярности д.б. сигналы, подскажите пожалуйста.

|

|

|

|

|

|

|

|

Apr 22 2018, 21:39 Apr 22 2018, 21:39

|

В поисках себя...

Группа: Свой

Сообщений: 729

Регистрация: 11-06-13

Из: Санкт-Петербург

Пользователь №: 77 140

|

Цитата Подскажите, сигналы vsync и hsync когда в 1, а когда в 0 ?

И то же самое про сигнал DE. Смотрите внимательно описание на дисплей. Если верить ему - активный уровень сигналов H_sync и V_sync - лог. 0. DE - активный уровень - лог.1 Цитата Как я понял, лучше перевести дисплей в режим sync ( не de-оnly). Правильно? Как Вам удобнее так и работайте. Цитата Код модуля на верилоге: Ужас  Цитата всё равно не работает.... И не должно... Ибо код с ошибками.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|