| |

|

|

Проблема с ПСС в синтезаторе сантиметрового диапазона Проблема с ПСС в синтезаторе сантиметрового диапазона, Проблема со spur в синтезаторе сантиметрового диапазона |

|

|

|

|

Oct 5 2011, 07:44 Oct 5 2011, 07:44

|

Узкополосный широкополосник

Группа: Свой

Сообщений: 2 316

Регистрация: 13-12-04

Из: Moscow

Пользователь №: 1 462

|

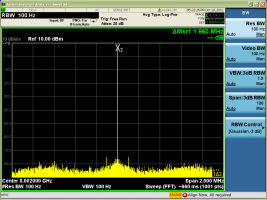

Цитата(Master_MW @ Oct 4 2011, 22:51)  Измерил кусок смеситель - ППФ - делитель и вот что получилось.

...

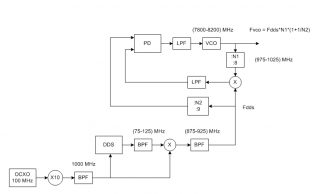

Изменить частоту на доли килогерца - начинаются проблемы. Может с похожими узлами кто-нибудь имел схожие проблемы, при подавлении спуров DDS, например ? Как Вы сами видите, это не спуры, в последней схеме DDS нет. Но задачка не такая простая, как может показаться на первый взгляд. Рассмотрим случай с частотой DDS (E8257) = 100.1 МГц. Комбинационные составляющие на выходе смесителя будут иметь следующий вид: Fmix(n,m) = n*F1 +- m*F2 где n,m = 0,1,2 ... F1 = 1000 MГц F2 = 100.1 МГц 1000 - 100.1 = 899.9 МГц - центральная частота перед делителем Fmix(0,+1) = 100.1 МГц 899.9/9 +- 100.1 = 99.99 + 0.11 МГц Fmix(1,+1) = 1000 + 100.1 = 1100.1 МГц 1100.1 - 899.9 = 200.2 МГц 899.9/9 +- 200.2 = 99.99 + 0.22 МГц Fmix(1,-3) = 1000 - 3*100.1 = 699.7 МГц 899.9 - 699.7 = 200.2 МГц 899.9/9 +- 200.2 = 99.99 + 0.22 МГц Fmix(2,-9) = 2*1000 - 9*100.1 = 1099.1 МГц 1099.1 - 899.9 = 199.2 МГц 899.9/9 +- 199.2 = 99.99 - 0.77 МГц Fmix(0,+7) = 7* 100.1 = 700.7 МГц 899.9 - 700.7 = 199.2 МГц 899.9/9 +- 199.2 = 99.99 - 0.77 МГц Fmix(0,+9) = 9*100.1 = 900.9 МГц 900.9 - 899.9 = 1 МГц 899.9/9 +- 1 = 99.99 +- 1 МГц За счет ограничения амплитуды и дополнительных комбинаций побочные составляющие станут симметричны относительно частоты 99.99 МГц и примут следующий вид: +-0.11, +-0.22, +-0.33 ... +-k*0.11 МГц. Или в общем виде Fspur = +- k*|Fdds - (Fvco-Fdds)/Ndiv| Но возникает вопрос: почему частоты +-0.44 и +-0.55 МГц значительно больше остальных? Единственный вариант, который мне приходит в голову - внутри микросхемы HMC394 деление разбито на два /(2*N) (в данном случае /(2*4.5) ) или используется предделитель 2/3. Хорошо бы посмотреть анализатором частоту (1000 - 100.1)/2 = 449.95 МГц. Классический вариант проблемы "разных опор". Пути решения в самом простом случае - замена смесителя на умножитель (например ADL5391) или квадратурный балансный модулятор + ППФ с хорошим внеполосным подавлением (SAW, BAW, CR), в лучшем случае - принципиально другое построение, например

Уменьшено до 79%

812 x 491 (22.02 килобайт)

|

|

|

|

|

|

|

|

|

Oct 5 2011, 10:11 Oct 5 2011, 10:11

|

.

Группа: Участник

Сообщений: 2 424

Регистрация: 25-12-08

Пользователь №: 42 757

|

Цитата(rloc @ Oct 5 2011, 12:25)  Прошу прощения, взял 100.1 МГц, вместо 100.0001 МГц, но по сути ничего не меняется. по сути - на больших расстройках , на порядок шырше полосы PLL , спуров нет. Смеситель ? - нет , не он , имхо. Master_MW , по Вашей структурной схеме непонятно какие уровни на смесителе, точнее написано минус 15 dbm и 0 dbm , а что куда подается и с какими уровнями на самом деле ?

Сообщение отредактировал тау - Oct 5 2011, 10:53

|

|

|

|

|

|

|

|

Oct 7 2011, 12:06 Oct 7 2011, 12:06

|

Местный

Группа: Свой

Сообщений: 202

Регистрация: 18-12-08

Из: Беларусь, Минск

Пользователь №: 42 590

|

Уважаемые коллеги, я прошу прощения за долгое отсутствие ..... Проверил изложенные здесь соображения по поводу выходу из ситуации. Выход нашелся, благодаря rloc, которому за это я бы хотел сказать отдельное БОЛЬШОЕ СПАСИБО  Цитата Master_MW , по Вашей структурной схеме непонятно какие уровни на смесителе, точнее написано минус 15 dbm и 0 dbm , а что куда подается и с какими уровнями на самом деле ? Сигнал Fvco/8 подается на вход RF смесителя, на вход IF смесителя подается сигнал от DDS. мощности, непосредственно подаваемые на смеситель, равны 0 dBm и -15 dBm по сигналу Fvco/8 и DDS. Цитата Имело бы смысл от этого уйти. Например тупо сделать частоту ФД и опорные частоты 50 Мгц. Ну или разогнать ДДС до диапазона 125-150 мгц и поделить после смесителя не на 9, а на 7 например. Не помогло ....изменил частоту DDS на величину 200 МГц, делитель соответственно на 8, полосовой фильтр переделал на 800 МГц.... пусть и на других частотах , но спуры остались... К месту оказалась архитектура, предложенная rloc, что и сняло проблему .... К месту пришлись старые поделки и макетки с предыдущих проектов, что позволило "на коленке" проверить предложенную архитектуру  И притом ФШ оказался в полосе основной фАПЧ порядка 4-6 дБ лучше

--------------------

Отсуствие единых стандартов всегда будет мучать человечество.

|

|

|

|

|

|

|

|

Oct 7 2011, 13:35 Oct 7 2011, 13:35

|

Гуру

Группа: Свой

Сообщений: 3 439

Регистрация: 29-12-04

Пользователь №: 1 741

|

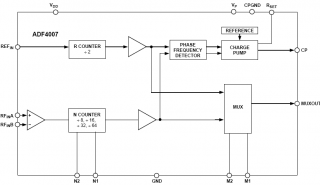

Цитата(Master_MW @ Oct 7 2011, 14:06)  К месту оказалась архитектура, предложенная rloc, что и сняло проблему Тогда вопрос к rloc теоретического плана. А а какой литературе такая архитектура ( с переменной частотой ФД) описана? И в чем ее "изюминка"? Почему именно это решение помогло избавится от спуров? Т.е нижняя часть с переносом ДДС на разностную частоту с опорой вопросов не вызыват. А вот формула Fvco=Fdds*N1(1+1/N2), а вернее ее член 1+1/N2 очень интересны.А то вот смотрю я на блок-схему ADF4007 и думаю, можно ли ее по подобной блок-схеме синтезатора применить? Вот только у нее коэффициент деления по опоре жестко задан. Надеюсь, 'Master_MW' простит мне сей вопрос в его теме?

Эскизы прикрепленных изображений

Уменьшено до 80%

837 x 482 (11.46 килобайт)

|

|

|

|

|

|

|

|

|

Oct 7 2011, 14:53 Oct 7 2011, 14:53

|

Узкополосный широкополосник

Группа: Свой

Сообщений: 2 316

Регистрация: 13-12-04

Из: Moscow

Пользователь №: 1 462

|

Архитектура подробно расписана в патенте у Александра, а также в его книге: "Frequency synthesizers: concept to product", Alexander Chenakin, Artech House, Dec 2010 (1+1/N2) - получается, если поставить равенство между двумя частотами, приходящими на фазовый детектор: Fvco/N1 - Fdds = Fdds/N2 Прелесть схемы легко понять, если подробно на листочке расписать все преобразования на смесителе n*f1+-m*f2 и многократные отражения спур от 0 и удвоенной частоты делителя. Последнее для меня было менее всего теоретически понятно, продолжаю поиски соответствующей литературы. Единственное, что удалось отыскать - парочка очень полезных статей Fred Walls: Effect of Aliasing on Spurs and PM Noise in Frequency Dividers  1380.pdf

1380.pdf ( 368.43 килобайт )

Кол-во скачиваний: 389Correlation Between Upper And Lower Noise Sidebands  1249.pdf

1249.pdf ( 242.69 килобайт )

Кол-во скачиваний: 488В итоге получается, что спуры от близко стоящих комбинаций частот (как на картинках с частотами 100.0001 и 1000 МГц или 100.0005 и 1000 МГц) просто сливаются с основной. Цитата(khach @ Oct 7 2011, 17:35)  А то вот смотрю я на блок-схему ADF4007 и думаю, можно ли ее по подобной блок-схеме синтезатора применить? Вот только у нее коэффициент деления по опоре жестко задан. Можно конечно, если мне не изменяет память, Александр в одной из статей упоминал ADF4002 для этих целей. Цитата(Master_MW @ Oct 7 2011, 16:06)  К месту оказалась архитектура, предложенная rloc, что и сняло проблему .... К месту пришлись старые поделки и макетки с предыдущих проектов, что позволило "на коленке" проверить предложенную архитектуру  И притом ФШ оказался в полосе основной фАПЧ порядка 4-6 дБ лучше  Поздравляю, очень быстро справились. Ждем результатов измерений.

|

|

|

|

|

|

|

|

Oct 7 2011, 16:47 Oct 7 2011, 16:47

|

Местный

Группа: Свой

Сообщений: 202

Регистрация: 18-12-08

Из: Беларусь, Минск

Пользователь №: 42 590

|

Цитата Тогда вопрос к rloc теоретического плана. А а какой литературе такая архитектура ( с переменной частотой ФД) описана? И в чем ее "изюминка"? Почему именно это решение помогло избавится от спуров? Т.е нижняя часть с переносом ДДС на разностную частоту с опорой вопросов не вызыват. А вот формула Fvco=Fdds*N1(1+1/N2), а вернее ее член 1+1/N2 очень интересны.А то вот смотрю я на блок-схему ADF4007 и думаю, можно ли ее по подобной блок-схеме синтезатора применить? Вот только у нее коэффициент деления по опоре жестко задан.

Надеюсь, 'Master_MW' простит мне сей вопрос в его теме? Естественно он Вам это простит.... Пусть другие молодые специалисты посмотрят на мои предыдущие результаты и и не допускают подобных ошибок. А по поводу ЧФД - это действительно хороший вопрос.. У меня пока стоит недешевый HMC439QS16G, есть желание заменить его на ADF4108 (остались с прежних проектов), с минимальным контроллером (на складе фирмы со старых времен около полусотни Attiny 2313), с SPI. 2 килобайт флеша контроллера должно хватить, чтобы забросить в микросхему начальную конфигурацию. Цена 439-го - около 25 долларов на сайте производителя. ADF-ка с контроллером получиться раза в 4 дешевле. Плюс сразу готовая диагностика наличия захвата по фазе, не надо городить АД по выходам 439-го. По предварительным прикидкам, ФШ ADF4108 в полосе ФАПЧ для обсуждаемой схемы составит -223+10*log(10^8)+20*log(8)=-124 дБ/Гц. Идею ставить в такую схему ADF4007 не поддерживаю по причине наличия там жесткого делителя на два по входу Ref in. Ну зачем искусственно занижать максимально возможную частоту работы ЧФД? Цитата Поздравляю, очень быстро справились. Ждем результатов измерений. В обязательном порядке. Мне просто повезло - практически все было на макетках, кроме ФНЧ по выходу смесителя.Лишь небольшое уточнение - частоту опоры 1 ГГЦ взял с генератора E8257D, но вряд ли это принципиально. Не думаю, что частота 1 ГГц с умноженного на ДНЗ на 10 ГК87-ТС окажется хуже по ФШ, нежели сигнал с генератора. Пока в цифрах - на частоте 8002 МГц получено на расстройке 1 кГц от несущей -111 дБ/Гц, на расстройке 10 кГц от несущей -113 дБ/Гц, 100 кГц от несущей -117 дБ/Гц. Графики выложу в понедельник - вторник .

Сообщение отредактировал Master_MW - Oct 7 2011, 17:15

--------------------

Отсуствие единых стандартов всегда будет мучать человечество.

|

|

|

|

|

|

|

|

Oct 7 2011, 17:02 Oct 7 2011, 17:02

|

Узкополосный широкополосник

Группа: Свой

Сообщений: 2 316

Регистрация: 13-12-04

Из: Moscow

Пользователь №: 1 462

|

Цитата(Master_MW @ Oct 7 2011, 20:47)  -223+20*log(10^8)+20*log(8)=-124 дБ/Гц. Вы хотели сказать 10*log(10^8) ? Вижу, что опечатка, иначе не получилось -124 дБн/Гц. Цитата(Master_MW @ Oct 7 2011, 20:47)  Идею ставить в такую схему ADF4007 не поддерживаю по причине наличия там жесткого делителя на два по входу Ref in. Ну зачем искусственно занижать максимально возможную частоту работы ЧФД? Частота ФД от этого меньше не становится, даже наоборот больше - 120 МГц. Делитель как раз делает чистый меандр, что может и повышает частоту.

|

|

|

|

|

|

|

|

Oct 7 2011, 17:16 Oct 7 2011, 17:16

|

Местный

Группа: Свой

Сообщений: 202

Регистрация: 18-12-08

Из: Беларусь, Минск

Пользователь №: 42 590

|

Цитата(rloc @ Oct 7 2011, 20:02)  Вы хотели сказать 10*log(10^8) ? Вижу, что опечатка, иначе не получилось -124 дБн/Гц. Исправил  Цитата(rloc @ Oct 7 2011, 20:02)  Частота ФД от этого меньше не становится, даже наоборот больше - 120 МГц. Делитель как раз делает чистый меандр, что может и повышает частоту. Я просто имел в виду, что при одной и той же частоте на выходе ФНЧ при использовании ADF4007 и 4108 частота будет в два раза меньше  (В диапазоне до 104 МГц, разумеется).

Сообщение отредактировал Master_MW - Oct 7 2011, 17:22

--------------------

Отсуствие единых стандартов всегда будет мучать человечество.

|

|

|

|

|

|

|

|

Oct 10 2011, 17:17 Oct 10 2011, 17:17

|

Местный

Группа: Свой

Сообщений: 202

Регистрация: 18-12-08

Из: Беларусь, Минск

Пользователь №: 42 590

|

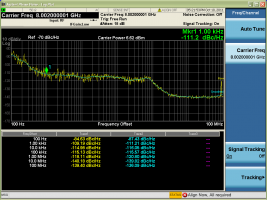

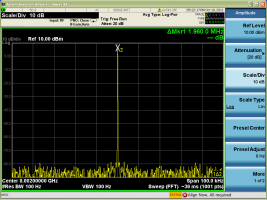

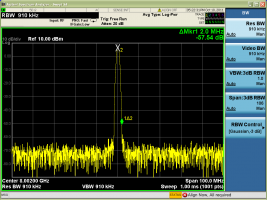

Цитата(rloc @ Oct 10 2011, 11:28)  ....Но опять же остается умножение на 8 в петле, это надо отдельно думать. Простейшее, что напрашивается - следящий фильтр на ФАПЧ по выходу DDS. Можно использовать и более изощренные методы, с уже упоминавшимся делением, например.... Посмотрел на спектр DDS - ближайшие спуры отстоят на величину около 350 - 400 кГц и ниже несущей на 85-90 дБ дБ... Думаю, при таком расположении нетрудно подавить их при помощи ФАПЧ с ФНЧ второго порядка ещё на 20 дБ, не особо ухудшив ФШ DDS. Этого должно быть более чем достаточно. Привожу обещанные результаты измерений, частота все та же - 8002 МГц.

Эскизы прикрепленных изображений

Уменьшено до 84%

1024 x 768 (44.24 килобайт)

|

Уменьшено до 84%

1024 x 768 (43.48 килобайт)

|

Уменьшено до 84%

1024 x 768 (42.99 килобайт)

|

Уменьшено до 84%

1024 x 768 (46.86 килобайт)

|

--------------------

Отсуствие единых стандартов всегда будет мучать человечество.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|