| |

проблемы с синхронизацией при помощи AD9524 проблемы с синхронизацией при помощи AD9524 |

|

|

|

|

Mar 15 2013, 04:32 Mar 15 2013, 04:32

|

Участник

Группа: Участник

Сообщений: 27

Регистрация: 20-05-10

Из: Новосибирск

Пользователь №: 57 383

|

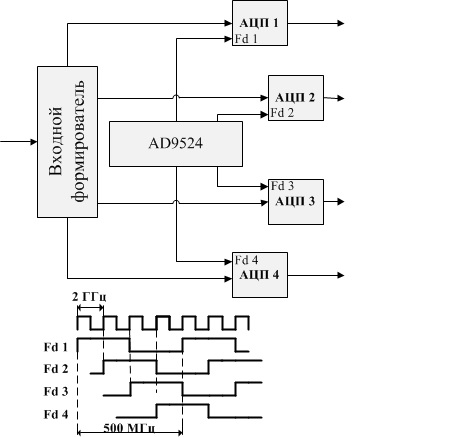

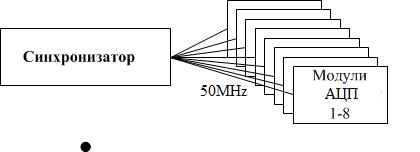

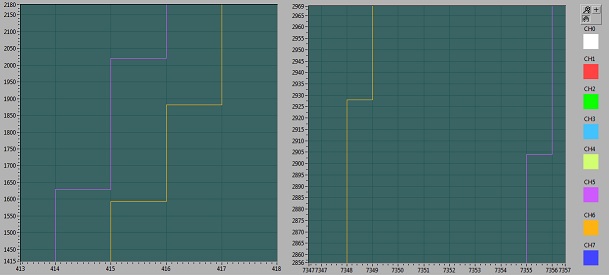

Добрый день! Проблема у меня следующая. Существует система из восьми 2ГГц модулей АЦП, которые должны работать в режиме жесткой синхронности. Каждый модуль АЦП построен на базе 4х кристаллов ADS5463 с частотой дискретизации 500МГц, включенных в параллель. Частота дискретизации каждого следующего АЦП сдвинута относительно предыдущего на 90 градусов. Для формирования частоты дискретизации и ее сдвигов используется кристалл AD9524. На рисунке дано пояснение:  Итак, при запуске одного модуля проблем не возникает, частоты формируются, фазовый сдвиг выполняется корректно. Проблемы начинаются при запуске системы из 8 модулей. Существует так называемая плата синхронизации, с выходов которой на каждый модуль АЦП приходит единая опорная частота (50МГц). Эта частота подается на входы REF кристалла AD9524. (рис)  В качестве внешнего VXCO в каждом модуле АЦП стоит 80МГц CVPD-920. По идее, при организации такой системы все модули между собой должны работать синхронно. Но они так не работают!!! Каждый живет свей жизнью. Ко всему прочему складывается впечатление, что у каждого кристалла AD9524 формируется своя частота дискретизации, типа у одного 500МГц, у другого 500 с небольшим. Потому что при подаче на входы 8 модулей одного и тот же сигнала, видно, что сдвиг между ними не постоянный, а увеличивающийся со временем. не знаю, понятно удалось изложить суть проблемы или нет, но попробую приложить еще пару иллюстраций:  На первом показан начальный сдвиг фаз между двумя модулями, на втором - сдвиг фаз спустя 16 периодов 240нс сигнала.  На последнем видна асинхронность регистрации одного и того же входного сигнала при едином внешнем запуске. P.S. При более детальном изучении выяснилось, что состояние обоих PLL у AD9524 находится в UNLOCK моде. Но как с этим бороться и почему он не входит в LOCK я не могу понять  Надеюсь на помощь более опытных и грамотных специалистов!

Сообщение отредактировал AiS - Mar 15 2013, 04:34

|

|

|

|

|

|

2 страниц  1 2 >

1 2 >

|

|

Ответов

(1 - 20)

|

|

Mar 15 2013, 13:50 Mar 15 2013, 13:50

|

Местный

Группа: Участник

Сообщений: 242

Регистрация: 10-06-08

Из: Хочу в пампасы...

Пользователь №: 38 192

|

Цитата(AiS @ Mar 15 2013, 08:32)  Проблема у меня следующая. P.S. При более детальном изучении выяснилось, что состояние обоих PLL у AD9524 находится в UNLOCK моде. Но как с этим бороться и почему он не входит в LOCK я не могу понять  Надеюсь на помощь более опытных и грамотных специалистов! Внимательно посмотрите осциллографом форму синхронизирующих сигналов непосредственно на входе ведомых модулей. Очень может быть из-за переотражений форма сильно искажена вот ПЛЛ и не синхронизируется. Было такое у меня, один тактовый сигнал на две ФПГА расходился. Из-за неудачного выбора места расхождения на концах "вилки" были жуткие искажения формы клока. Ну и ПЛЛ не синхронизировался. Такое можно довольно быстро в HyperLynx промоделировать.

Сообщение отредактировал Kompot - Mar 15 2013, 13:51

|

|

|

|

|

|

|

|

Mar 17 2013, 03:51 Mar 17 2013, 03:51

|

Voltage Control Output

Группа: Свой

Сообщений: 4 598

Регистрация: 21-07-09

Из: Kursk

Пользователь №: 51 436

|

Цитата(AiS @ Mar 15 2013, 07:32)  Итак, при запуске одного модуля проблем не возникает, частоты формируются, фазовый сдвиг выполняется корректно. Проблемы начинаются при запуске системы из 8 модулей. В вашем случае трудно разобраться, не зная конструктивно-схемотехнических подробностей реализации всей системы. Рискну предположить, что здесь не учтены фазовые задержки и/или нарушено согласование модулей по тактовой частоте и/или по сигналу REF. Обычно такие сложные системы синхронизируются по оптоволоконным линиям связи, которые решают обе проблемы одним махом. Также стоит обратить внимание на ЭМС по перекрёстным электромагнитному наводкам, которые могут возникнуть между 8 модулями. Ну и в конце концов перечисленные Вами частоты наводят на мысль о том, что между тактовыми и синхронизирующими сигналами могут возникнуть достаточно мощные биения, которые сбивают синхронизацию АЦП. В этом случае надо снять спектр REF непосредственно на входе АЦП и оценить уровень ПСС при различным Spanах, начиная с единиц кГц. На более опытного и грамотного специалиста заведомо не претендую, так как подобные системы не проектировал никогда...

--------------------

Слово - не воробей, вылетит - не пощадит

|

|

|

|

|

|

|

|

Mar 18 2013, 04:10 Mar 18 2013, 04:10

|

Участник

Группа: Участник

Сообщений: 27

Регистрация: 20-05-10

Из: Новосибирск

Пользователь №: 57 383

|

Kompot да в том-то и оно, что я не могу сказать, чтоб REF был искажен. VCOвсе модули располагаются в крейте ratiopacPRO-air 24572-031 фирмы Schroff. Синхроимпульсы до каждого модуля передаются по оптоволокну. polyakovavЦитата В этом синтезаторе столько регистров управления, что за программистом проверять и проверять....;-) есть такое. я даже не спорю, что могу что-то задавать не так или не корректно. на всякий случай прикрепляю док с моими регистрами, вдруг кто чего увидит.  Ahdl1.pdf

Ahdl1.pdf ( 114.14 килобайт )

Кол-во скачиваний: 230

|

|

|

|

|

|

|

|

Mar 18 2013, 04:53 Mar 18 2013, 04:53

|

Местный

Группа: Свой

Сообщений: 413

Регистрация: 1-10-08

Из: Екатеринбург

Пользователь №: 40 610

|

Цитата(VCO @ Mar 18 2013, 03:54)  Как это ни парадоксально, но я сместил бы акцент с 2 ГГц на 50 МГц! задам вопросы, т.к. с синтезаторами только разбираюсь Почему Вы так считаете? ФАПЧ1 синтезатора должна почистить джиттер опоры может быть так чтО в "Zero delay operation" синтезаторы синхронизируются с опорой 50МГц, но каждый со своим "нулем" ? посмотреть на разбег фаз на более длительном интервале времени, будут видны биения - нестабильность, разность фаз будет постоянно расти / резко меняться - нет захвата, т.е. что-то с настроиками.

Сообщение отредактировал _Vova - Mar 18 2013, 04:54

|

|

|

|

|

|

|

|

Mar 18 2013, 06:46 Mar 18 2013, 06:46

|

Частый гость

Группа: Свой

Сообщений: 197

Регистрация: 26-05-06

Из: Воронеж

Пользователь №: 17 486

|

Цитата(AiS @ Mar 18 2013, 07:10)  есть такое. я даже не спорю, что могу что-то задавать не так или не корректно. на всякий случай прикрепляю док с моими регистрами, вдруг кто чего увидит. Чтобы увидеть что-нибудь, нужно иметь схему всего Вашего устройства, знать как проводится инициализация, каким образом обеспечивается одновременный старт всех плат и т.д. и т.п. Недавно запускали похожую систему на AD9548, правда частоты пониже и каналов поменьше. Провозились больше двух месяцев, пока все заставили стартовать одновременно и синхронно по фазам. Так что Вам предстоит нелегкая работа.

|

|

|

|

|

|

|

|

Mar 18 2013, 08:29 Mar 18 2013, 08:29

|

Voltage Control Output

Группа: Свой

Сообщений: 4 598

Регистрация: 21-07-09

Из: Kursk

Пользователь №: 51 436

|

Цитата(_Vova @ Mar 18 2013, 07:53)  Почему Вы так считаете? Я железнячник по образованию и привык все возможные проблемы решать аппаратным способом. Программные изыски и так никуда не денутся, а в рамках данной темы они нам вовсе недоступны. Да и скорее всего не будут программисты копаться в чужих кодах и искать чужие ошибки, имхо... ЗЫ: Блин, P.S. в стартовом посте прошёл мимо моего взора. Конечно же я неправ, разумеется 2 ГГц!

--------------------

Слово - не воробей, вылетит - не пощадит

|

|

|

|

|

|

|

|

Mar 18 2013, 09:02 Mar 18 2013, 09:02

|

Местный

Группа: Свой

Сообщений: 413

Регистрация: 1-10-08

Из: Екатеринбург

Пользователь №: 40 610

|

Цитата(AiS @ Mar 15 2013, 07:32)  Итак, при запуске одного модуля проблем не возникает

P.S. При более детальном изучении выяснилось, что состояние обоих PLL у AD9524 находится в UNLOCK моде. захвата нет при включении нескольких модулей или его и в одном модуле нет?

|

|

|

|

|

|

|

|

Mar 18 2013, 10:15 Mar 18 2013, 10:15

|

Местный

Группа: Свой

Сообщений: 413

Регистрация: 1-10-08

Из: Екатеринбург

Пользователь №: 40 610

|

Цитата ...на всякий случай прикрепляю док с моими регистрами попробуйте в ADIsimCLK промоделировать схему с номиналами использованными Вами на сайте АД есть софт к EVAL board в нем наверняка можно посмотреть какими должны быть значения регистров

|

|

|

|

|

|

|

|

Mar 18 2013, 10:55 Mar 18 2013, 10:55

|

Участник

Группа: Участник

Сообщений: 27

Регистрация: 20-05-10

Из: Новосибирск

Пользователь №: 57 383

|

ViKo, в регистрах, помимо делителей и фильтров, рассчитываемых с помощью ADIsimCLK, так же задается еще ряд параметров. так что возможно там что-то выполняется не корректно. например калибровка VCO, либо же какие-то еще управляющие регистры. собственно у меня расчет был на то, что вдруг кто уже работал с данным кристаллом и сталкивался с подобным.

на счет опоры - смущает только то, что точно такие же модули синхронизации используются в аналогичной системе, правда в той системе вместо AD9524 использовался AD9518. И с ним все работает. В том числе и то, что оба ПЛЛ входят в LOCK

так что я, честно сказать, в некотором ступоре. есть подозрение, что во всем виноват кристалл VCXO (во всяком случае в AD9518 он внутренней, может потому и проблем не было...)

VCO, Да постскриптум был оставлен через пару минут, пока в ветке ни одного ответа даже не было.

Проект завтра выложу. просто руки не дошли уже сегодня

Сообщение отредактировал AiS - Mar 18 2013, 11:07

|

|

|

|

|

|

|

|

Mar 18 2013, 11:43 Mar 18 2013, 11:43

|

Частый гость

Группа: Свой

Сообщений: 197

Регистрация: 26-05-06

Из: Воронеж

Пользователь №: 17 486

|

Цитата(ViKo @ Mar 18 2013, 14:31)  ... следовательно, виновата опорная частота? Или железо не соответствует симулятору. В первую очередь нужно проверить, не выходит ли начальная отстройка за полосу захвата петли ФАПЧ. Полосу, вроде, можно посмотреть в ADIsimCLK (давно не пользовался). 50 МГц приходит снаружи, можно просто померить частотомером. Для 80 МГц получается возможная отстройка 1.6 кГц. Мерить лучше после буфера, потому что вход частотомера заметно влияет на генератор. Управляющим напряжением нужно двигать генератор 80 МГц как можно ближе к номиналу (с учетом измеренной отстройки 50 МГц) и следить за сигналом LOCK в синтезаторе. Случается, что при выбранных параметрах петли ФАПЧ полоса захвата получается всего с десяток Гц.

|

|

|

|

|

|

|

|

Mar 18 2013, 18:55 Mar 18 2013, 18:55

|

Частый гость

Группа: Свой

Сообщений: 197

Регистрация: 26-05-06

Из: Воронеж

Пользователь №: 17 486

|

Цитата(VCO @ Mar 18 2013, 19:37)  Агащаз, такую полосу по классической схеме Вы никогда не сможете реализовать (да оно здесь и не надо!).

Минимум, что получилось - около 100 Герц. Если покажете на конкретном VCO полосу 10 Гц, буду благодарень! Каюсь, приукрасил. У нас тоже было около 100, но получилось это случайно из-за ошибки в настройках (нужно было больше килогерца). На всякий случай предположил, что бывает еще хуже. Кстати, в AD9548 предусмотрено сужение полосы до долей герца для слежения за PPS от GPS-приемника. Надеюсь в скором времени попробовать живьем.

|

|

|

|

|

|

|

|

Apr 11 2013, 08:45 Apr 11 2013, 08:45

|

Участник

Группа: Участник

Сообщений: 27

Регистрация: 20-05-10

Из: Новосибирск

Пользователь №: 57 383

|

Доброго всем времени. прошу прощение за молчание. проблема вроде бы разрешилась. ну или хотя бы частично. проблем было две - с VCXO и с кодом. Проблема VCXO в том, что он имеет слишком маленький диапазон перестройки. Пытаясь синхронизоваться с 50МГцовой опорой, напряжение на подстраиваемой ножке VCXO просто уходило в зашкал. итог - PLL1 не в LOCk моде. При подаче в качестве опоры сигнала в 80МГц, сгенерированного аналогичным VCXO, PLL1 сразу входит в LOCK. (разумеется, при перерасчете соответсвующих делителей) Второй вариант решения мог быть при подключении вместо VCXO опорного сигнала в 50МГц. Но это фактически просто работа без PLL1 PLL2 не входил в LOCK по следующим причинам: 1. в даташит есть пункт MAXIMUM PFD FREQUENCY Antibacklash Pulse Width Minimum and Low 250 MHz Maximum and High 125 MHz у меня в регистре, где задается Antibacklash Pulse Width был указан максимум плюс был включен удвоитель частоты VCXO то есть на PFD приходила частота 160МГц, что противоречит указанным нормам. Тут просто надо было выключить удвоитель и пересчитать соответсвующий делитель (N2 на схеме) 2. Есть регистр "PLL2 charge pump control", если его не описывать, то ток устанавливается минимальный. ставлю его хотя бы в середину шкалы и вуаля - PLL2 входит в LOCK Наверное, для тех, кто с кристаллом не работал, вообще ничего не понятно отсюда. Для улучшения понимания приведу картинку с ADIsimCLK, хотя не уверена, что сильно поможет. Но из нее хотя бы наглядно видно, что есть удвоитель и PFD. В любом случае, вдруг кто будет мучиться с тем же? что и я, и тогда может кому-то это все пригодится.

Сообщение отредактировал AiS - Apr 11 2013, 08:46

Эскизы прикрепленных изображений

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|