Проблема у меня следующая.

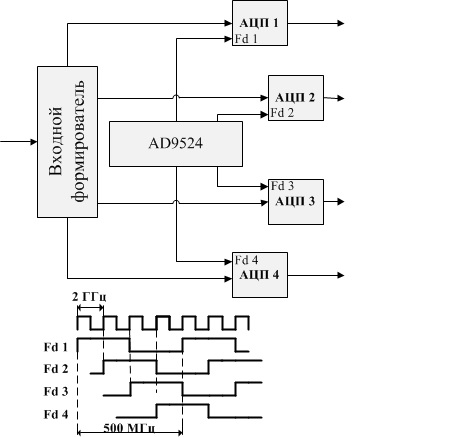

Существует система из восьми 2ГГц модулей АЦП, которые должны работать в режиме жесткой синхронности. Каждый модуль АЦП построен на базе 4х кристаллов ADS5463 с частотой дискретизации 500МГц, включенных в параллель. Частота дискретизации каждого следующего АЦП сдвинута относительно предыдущего на 90 градусов. Для формирования частоты дискретизации и ее сдвигов используется кристалл AD9524. На рисунке дано пояснение:

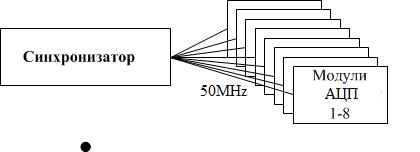

Итак, при запуске одного модуля проблем не возникает, частоты формируются, фазовый сдвиг выполняется корректно. Проблемы начинаются при запуске системы из 8 модулей. Существует так называемая плата синхронизации, с выходов которой на каждый модуль АЦП приходит единая опорная частота (50МГц). Эта частота подается на входы REF кристалла AD9524. (рис)

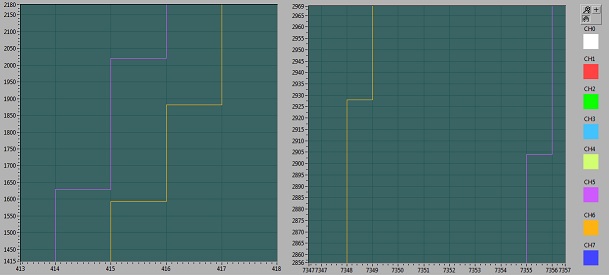

В качестве внешнего VXCO в каждом модуле АЦП стоит 80МГц CVPD-920. По идее, при организации такой системы все модули между собой должны работать синхронно. Но они так не работают!!! Каждый живет свей жизнью. Ко всему прочему складывается впечатление, что у каждого кристалла AD9524 формируется своя частота дискретизации, типа у одного 500МГц, у другого 500 с небольшим. Потому что при подаче на входы 8 модулей одного и тот же сигнала, видно, что сдвиг между ними не постоянный, а увеличивающийся со временем. не знаю, понятно удалось изложить суть проблемы или нет, но попробую приложить еще пару иллюстраций:

На первом показан начальный сдвиг фаз между двумя модулями, на втором - сдвиг фаз спустя 16 периодов 240нс сигнала.

На последнем видна асинхронность регистрации одного и того же входного сигнала при едином внешнем запуске.

P.S. При более детальном изучении выяснилось, что состояние обоих PLL у AD9524 находится в UNLOCK моде. Но как с этим бороться и почему он не входит в LOCK я не могу понять

Надеюсь на помощь более опытных и грамотных специалистов!