| |

Прошивка ПЛИС Cyclone IV с микроконтроллера Прошивка ПЛИС Cyclone IV с микроконтроллера |

|

|

2 страниц  1 2 >

1 2 >

|

|

Ответов

(1 - 29)

|

|

Apr 12 2018, 13:14 Apr 12 2018, 13:14

|

Участник

Группа: Участник

Сообщений: 54

Регистрация: 25-12-15

Из: Пенза

Пользователь №: 89 844

|

Цитата(Sprite @ Apr 12 2018, 14:55)  Добрый день!

Есть МК stm32f4VET6 с готовым бутлоадером. Требуется организовать загрузку прошивки в ПЛИС Cyclone IV. Немного не понятно, где есть прошивка ПЛИС (в памяти МК, требуется "заливать" с ПК через МК, на внешнем носителе и т.п.). Я бы начал с возможных вариантов загрузки ПЛИС (должно быть описано в datashet на микросхему), сообразно прочитанному смотрел бы что именно "потянет" МК. Уточнить бы схему эксперимента...

|

|

|

|

|

|

|

|

Apr 12 2018, 13:19 Apr 12 2018, 13:19

|

Местный

Группа: Свой

Сообщений: 498

Регистрация: 4-10-04

Из: Нижний Новгород

Пользователь №: 771

|

Цитата(Sprite @ Apr 12 2018, 14:55)  Добрый день!

Есть МК stm32f4VET6 с готовым бутлоадером. Требуется организовать загрузку прошивки в ПЛИС Cyclone IV. Пару лет назад я поднимал подобную тему, но речь шла о CPLD MAXII и один добрый человек (bugdesigner) посоветовал мне использовать FPGA и производить загрузку программы через passive serial. Подскажите, где можно посмотреть более подробную инфу по данному вопросу? В идеале хотелось бы передавать данные с МК по какому-нибудь стандартному интерфейсу (например SPI), пусть даже используя внешнюю микросхему памяти. Как лучше организовать?

Заранее спасибо. https://www.altera.com/content/dam/altera-w.../cyiv-51008.pdfPS Configuration Using an External Host p. 32

--------------------

Человек - это существо, которое охотнее всего рассуждает о том, в чем меньше всего разбирается.

|

|

|

|

|

|

|

|

Apr 12 2018, 13:27 Apr 12 2018, 13:27

|

Частый гость

Группа: Участник

Сообщений: 173

Регистрация: 11-05-08

Пользователь №: 37 414

|

Цитата(serj1979 @ Apr 12 2018, 20:14)  Немного не понятно, где есть прошивка ПЛИС (в памяти МК, требуется "заливать" с ПК через МК, на внешнем носителе и т.п.). Можно считать что она в памяти МК. Цитата(Realking @ Apr 12 2018, 20:19)  Спасибо, ознакомлюсь с документом!

|

|

|

|

|

|

|

|

Apr 13 2018, 08:11 Apr 13 2018, 08:11

|

Частый гость

Группа: Участник

Сообщений: 173

Регистрация: 11-05-08

Пользователь №: 37 414

|

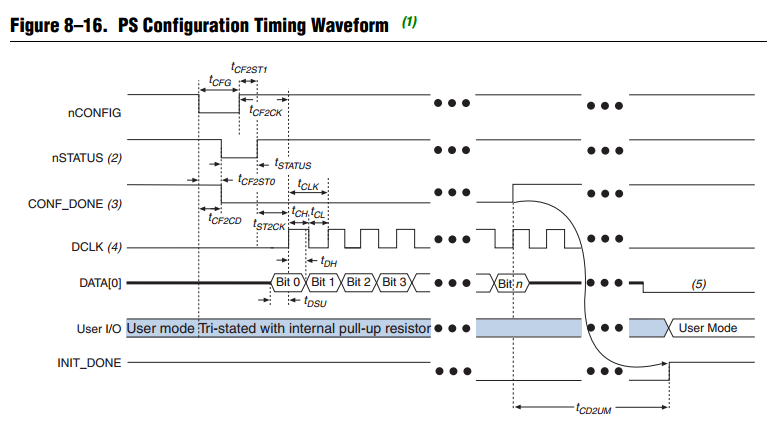

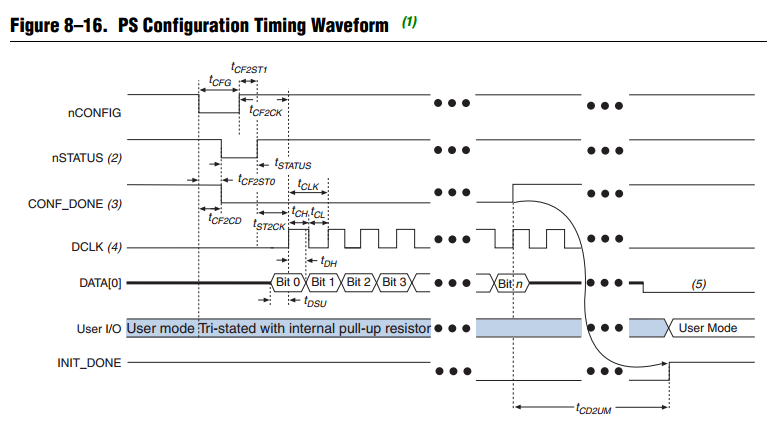

Цитата(Genadi Zawidowski @ Apr 13 2018, 03:34)  Вот вам пример дизайна, где грузится циклон четвертый из процессора. Программа интересует? Дам ссылку. В аттачменте - преобразователь из .RBF в сишный текст. Для скорости гружу 16-битными словами. Старшим битом вперед. Если я Вас правильно понял - в приложении программа подготовки rbf-файла для заливки в ПЛИС с поменяными местами байтами и младшим битом вперед? Буду очень признателен если скинете кусок кода программы МК!   Согласно представленной диаграмме сигналы nConfig, DATA[0] (SPI_MOSI), DCLK (SPI_SCK) конфигурируются в МК как выходы, остальные сигналы (nSTATUS, CONF_DONE, INIT_DONE) как входы, верно? И еще вопрос: как происходит (и происходит ли вообще) верификация прошивки в ПЛИС? Под рукой только Cyclone III, доки почитал - вроде бы механизм загрузки тот же самый, хочу потренироваться на нем.

|

|

|

|

|

|

|

|

Apr 13 2018, 08:53 Apr 13 2018, 08:53

|

Местный

Группа: Свой

Сообщений: 498

Регистрация: 4-10-04

Из: Нижний Новгород

Пользователь №: 771

|

Цитата(Sprite @ Apr 13 2018, 11:11)  Если я Вас правильно понял - в приложении программа подготовки rbf-файла для заливки в ПЛИС с поменяными местами байтами и младшим битом вперед? Буду очень признателен если скинете кусок кода программы МК!   Согласно представленной диаграмме сигналы nConfig, DATA[0] (SPI_MOSI), DCLK (SPI_SCK) конфигурируются в МК как выходы, остальные сигналы (nSTATUS, CONF_DONE, INIT_DONE) как входы, верно? И еще вопрос: как происходит (и происходит ли вообще) верификация прошивки в ПЛИС? Под рукой только Cyclone III, доки почитал - вроде бы механизм загрузки тот же самый, хочу потренироваться на нем. верно INIT_DONE можно не юзать в МК верификация по nSTATUS и CONF_DONE

--------------------

Человек - это существо, которое охотнее всего рассуждает о том, в чем меньше всего разбирается.

|

|

|

|

|

|

|

|

Apr 13 2018, 08:55 Apr 13 2018, 08:55

|

Профессионал

Группа: Участник

Сообщений: 1 620

Регистрация: 22-06-07

Из: Санкт-Петербург, Россия

Пользователь №: 28 634

|

CODE /* FPGA загружается процессором с помощью SPI */

static void board_fpga_loader_PS(void)

{

#if (WITHSPIHW && WITHSPI16BIT) // for skip in test configurations

#if (CTLSTYLE_RAVENDSP_V3 && ! WITHUSEDUALWATCH) && (DDS1_CLK_MUL == 10)

#include "rbf/rbfimage_v3_pll.h"

#elif (CTLSTYLE_RAVENDSP_V3 && ! WITHUSEDUALWATCH) && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v3.h"

#elif (CTLSTYLE_RAVENDSP_V4 && ! WITHUSEDUALWATCH) && (DDS1_CLK_MUL == 10)

#include "rbf/rbfimage_v4_pll.h"

#elif (CTLSTYLE_RAVENDSP_V4 && ! WITHUSEDUALWATCH) && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v4.h"

#elif CTLSTYLE_RAVENDSP_V5 && (DDS1_CLK_MUL == 10)

#include "rbf/rbfimage_v5_2ch_pll.h" // CTLSTYLE_RAVENDSP_V5 with 12.288 osc

#elif CTLSTYLE_RAVENDSP_V5 && (DDS1_CLK_MUL == 1) && WITHOPERA4BEACON

#include "rbf/rbfimage_v5_2ch_opera4.h" // CTLSTYLE_RAVENDSP_V5

#elif CTLSTYLE_RAVENDSP_V5 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v5_2ch.h" // CTLSTYLE_RAVENDSP_V5

#elif CTLSTYLE_RAVENDSP_V6 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v6_2ch.h" // CTLSTYLE_RAVENDSP_V6

#elif CTLSTYLE_RAVENDSP_V7 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7_2ch.h" // CTLSTYLE_RAVENDSP_V7

#elif CTLSTYLE_RAVENDSP_V8 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v8.h"

#elif CTLSTYLE_RAVENDSP_V9 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7renesas_2ch.h"

#elif CTLSTYLE_RAVENDSP_V2 && (DDS1_CLK_MUL == 1) && WITHRTS192

#include "rbf/rbfimage_v8renesas_2ch.h"

#elif CTLSTYLE_RAVENDSP_V2 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v8renesas96k_2ch.h"

#elif CTLSTYLE_STORCH_V1 && ! WITHUSEDUALWATCH && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7_1ch.h" //

#elif CTLSTYLE_STORCH_V1 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7_2ch.h" // same as CTLSTYLE_RAVENDSP_V7

#elif CTLSTYLE_STORCH_V2 && ! WITHUSEDUALWATCH && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7_1ch.h" //

#elif CTLSTYLE_STORCH_V2 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7_2ch.h" // same as CTLSTYLE_RAVENDSP_V7

#elif CTLSTYLE_STORCH_V3 && ! WITHUSEDUALWATCH && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7_1ch.h" //

#elif CTLSTYLE_STORCH_V3 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_v7_2ch.h" // same as CTLSTYLE_RAVENDSP_V7

#elif CTLSTYLE_STORCH_V4 && ! WITHUSEDUALWATCH && (DDS1_CLK_MUL == 1) // modem v2

#include "rbf/rbfimage_v7_1ch.h" //

//#elif CTLSTYLE_STORCH_V4 && (DDS1_CLK_MUL == 1) // modem v2

// #include "rbf/rbfimage_v7_2ch.h" // same as CTLSTYLE_RAVENDSP_V7

#elif CTLSTYLE_STORCH_V5 && ! WITHUSEDUALWATCH && (DDS1_CLK_MUL == 1) // mini

#include "rbf/rbfimage_v7_1ch.h" //

#elif CTLSTYLE_STORCH_V5 && (DDS1_CLK_MUL == 1) // mini

#include "rbf/rbfimage_v7a_2ch.h" // same as CTLSTYLE_RAVENDSP_V7

#elif CTLSTYLE_STORCH_V6 && ! WITHUSEDUALWATCH && (DDS1_CLK_MUL == 1) // mini

#include "rbf/rbfimage_v7_1ch.h" //

#elif CTLSTYLE_STORCH_V6 && (DDS1_CLK_MUL == 1) // mini

#include "rbf/rbfimage_v7a_2ch.h" // same as CTLSTYLE_STORCH_V6

#elif CTLSTYLE_OLEG4Z_V1 && (DDS1_CLK_MUL == 1)

#include "rbf/rbfimage_oleg4z.h" // same as CTLSTYLE_RAVENDSP_V7, 1 RX & WFM

#else

#error Missing FPGA image file

#endif

restart:

;

unsigned long w = 1000;

do {

debug_printf_P(PSTR("fpga: board_fpga_loader_PS start\n"));

const size_t rbflength = sizeof rbfimage / sizeof rbfimage [0];

/* After power up, the Cyclone IV device holds nSTATUS low during POR delay. */

FPGA_NCONFIG_PORT_S(FPGA_NCONFIG_BIT);

local_delay_ms(1);

/* 1) Выставить "1" на nCONFIG */

//debug_printf_P(PSTR("fpga: FPGA_NCONFIG_BIT=1\n"));

FPGA_NCONFIG_PORT_C(FPGA_NCONFIG_BIT);

/* x) Дождаться "0" на nSTATUS */

//debug_printf_P(PSTR("fpga: waiting for FPGA_NSTATUS_BIT==0\n"));

while (board_fpga_get_NSTATUS() != 0)

{

local_delay_ms(1);

if (-- w == 0)

goto restart;

}

FPGA_NCONFIG_PORT_S(FPGA_NCONFIG_BIT);

/* 2) Дождаться "1" на nSTATUS */

//debug_printf_P(PSTR("fpga: waiting for FPGA_NSTATUS_BIT==1\n"));

while (board_fpga_get_NSTATUS() == 0)

{

local_delay_ms(1);

if (-- w == 0)

goto restart;

}

/* 3) Выдать байты (бладший бит .rbf файла первым) */

//debug_printf_P(PSTR("fpga: start sending RBF image (%lu of 16-bit words)\n"), rbflength);

if (rbflength != 0)

{

unsigned wcd = 0;

size_t n = rbflength - 1;

const uint16_t * p = rbfimage;

//

hardware_spi_connect_b16(SPIC_SPEEDUFAST, SPIC_MODE3);

hardware_spi_b16_p1(* p ++);

while (n --)

{

if (board_fpga_get_CONF_DONE() != 0)

{

//debug_printf_P(PSTR("fpga: Unexpected state of CONF_DONE==1\n"));

break;

}

hardware_spi_b16_p2(* p ++);

}

//debug_printf_P(PSTR("fpga: done sending RBF image, waiting for CONF_DONE==1\n"));

/* 4) Дождаться "1" на CONF_DONE */

while (board_fpga_get_CONF_DONE() == 0)

{

++ wcd;

hardware_spi_b16_p2(0xffff);

}

hardware_spi_complete_b16();

hardware_spi_disconnect();

//debug_printf_P(PSTR("fpga: CONF_DONE asserted, wcd=%u\n"), wcd);

/*

After the configuration data is accepted and CONF_DONE goes

high, Cyclone IV devices require 3,192 clock cycles to initialize properly and enter

user mode.

*/

}

} while (board_fpga_get_NSTATUS() == 0); // если ошибка - повторяем

//debug_printf_P(PSTR("fpga: board_fpga_loader_PS done\n"));

/* проверяем, проинициализировалась ли FPGA (вошла в user mode). */

while (HARDWARE_FPGA_IS_USER_MODE() == 0)

{

local_delay_ms(1);

if (-- w == 0)

goto restart;

}

debug_printf_P(PSTR("fpga: board_fpga_loader_PS: usermode okay\n"));

#endif /* (WITHSPIHW && WITHSPI16BIT) */ // for skip in test configurations

}

Проект целиком тут https://188.134.5.254/browser/trunk - данная функция в файле board.c

|

|

|

|

|

|

|

|

Apr 13 2018, 15:46 Apr 13 2018, 15:46

|

Частый гость

Группа: Участник

Сообщений: 173

Регистрация: 11-05-08

Пользователь №: 37 414

|

Цитата(Genadi Zawidowski @ Apr 13 2018, 15:55)  Проект целиком тут https://188.134.5.254/browser/trunk - данная функция в файле board.c Большущщее Вам спасибо! (название проекта красивое  ) Теперь ясно в каком направлении двигаться!

|

|

|

|

|

|

|

|

Apr 14 2018, 11:05 Apr 14 2018, 11:05

|

Частый гость

Группа: Участник

Сообщений: 173

Регистрация: 11-05-08

Пользователь №: 37 414

|

Еще один маленький вопрос касательно получения rbf-файла. Скомпилил простейший проект с одним счетчиком. Не зная как из sof сделать rbf в просторах интернета нашел такие строчки: Код quartus_cpf -c test1.sof test1.rbf Получил rbf -файл размером 368 011 байт!!! Потом поискал в настройках Device and Pin options -> Programming files и выставил галочку "rbf-файл". Получил при этом файл 105 КБ, стало немного поспокойнее) В связи с этим вопрос: каков максимально возможный размер rbf-файла для Cyclone III (EP3C5E144C8N) и Cyclone IV (EP4CE6E22C8)? Прошивку для ПЛИС планировал сохранять в ROM МК, а ROM не резиновый)

|

|

|

|

|

|

|

|

Apr 15 2018, 12:13 Apr 15 2018, 12:13

|

Частый гость

Группа: Участник

Сообщений: 173

Регистрация: 11-05-08

Пользователь №: 37 414

|

Цитата(ViKo @ Apr 14 2018, 19:37)  Там где-то установка "compressed" задается. А размер можно найти в неких доках, конкретно не помню. Спасибо большое, разобрался! На вкладке " Configuration" раздела " Devise and Pin options" находится чекбокс " Generate compressed bitstreams" определяющий сжатие rbf-файла. Сам rbf-файл выбирается на вкладке " Programming Files", может кому пригодится  В документе " Device Handbook" циклона все подробно расписано (раздел " Configuration Data Decompression"), там же можно найти информацию о максимальном размере rbf-файла.

Сообщение отредактировал Sprite - Apr 15 2018, 12:13

|

|

|

|

|

|

|

|

Apr 21 2018, 10:00 Apr 21 2018, 10:00

|

Частый гость

Группа: Свой

Сообщений: 163

Регистрация: 25-09-09

Из: Nizhny Novgorod, Russia

Пользователь №: 52 588

|

Цитата(Sprite @ Apr 20 2018, 15:33)  Единственное наблюдение по верификации данных: она, как мне показалось, какая-то не полная: пробовал менять в прошивке байт где-то в начале файла - прошивка не загрузилась (судя по выводу CONF_DONE), но если поменять байт ближе к середине - то все грузится успешно. Так что остается надеяться на то, как карты лягут). Чтобы однозначно удостовериться в правильной загрузке ПЛИСа обычно в самой прошивке ПЛИС предусматривают отправку сообщения с ПЛИС в микроконтроллер в любом виде по любому выводу. Если после загрузки ПЛИСа микроконтроллер получает это сообщение, значит загрузка ПЛИСа прошла успешно. Я бы отправлял эти сообщения время от времени во время работы устройства, чтобы удостовериться, что прошивка не сбилась в ходе работы и отрабатывает верно. В противном случае просто перезагружаем ПЛИС прошивкой заново. Всяко надёжнее будет, чем просто грузить ПЛИС с ПЗУшки.

|

|

|

|

|

|

|

|

Apr 23 2018, 04:21 Apr 23 2018, 04:21

|

Частый гость

Группа: Участник

Сообщений: 173

Регистрация: 11-05-08

Пользователь №: 37 414

|

Цитата(Enthusiast @ Apr 21 2018, 17:00)  Чтобы однозначно удостовериться в правильной загрузке ПЛИСа обычно в самой прошивке ПЛИС предусматривают отправку сообщения с ПЛИС в микроконтроллер в любом виде по любому выводу. Если после загрузки ПЛИСа микроконтроллер получает это сообщение, значит загрузка ПЛИСа прошла успешно.

Я бы отправлял эти сообщения время от времени во время работы устройства, чтобы удостовериться, что прошивка не сбилась в ходе работы и отрабатывает верно. В противном случае просто перезагружаем ПЛИС прошивкой заново. Всяко надёжнее будет, чем просто грузить ПЛИС с ПЗУшки. Спасибо, учту! Связь МК с ПЛИС планирую осуществлять по SPI.

|

|

|

|

|

|

|

|

Apr 25 2018, 03:01 Apr 25 2018, 03:01

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 31-01-09

Пользователь №: 44 224

|

Всем привет.

Занимаюсь вот чем-то подобным. Пишу бутлоадер для устройства.

Программа на компьютере открывает rbf файл и шлет его кусками по 256 байт на устройство, плисина заливает эти куски постранично во флешку EPCS64.

Перед записью производится стирание нужного участка флехи посекторно, участок заведомо больше rbf файла.

После записи каждой страницы производится чтение ее из флехии и сравнение с буфером, ошибок нет, пишется правильно.

Пишу по нулевому адресу.

Проблема в том, что после перезагрузки плисина не грузится. Уже не знаю что делать, ошибок не вижу. Байты перед записью во флеху переворачиваю задом-наперед.

Подскажите что-нибудь.

|

|

|

|

|

|

|

|

Apr 25 2018, 16:41 Apr 25 2018, 16:41

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 31-01-09

Пользователь №: 44 224

|

Цитата(ViKo @ Apr 25 2018, 07:45)  И, повторю для невнимательных, я ничего не переворачиваю задом наперед. Просто посылаю байты с нужного конца. И чем это отличается одно от другого ? Если я работаю с массивом 256*8 бит, то проще отобразить биты данных еще на моменте формирования буфера, чем потом сушить мозг над адрессацией.

|

|

|

|

|

|

|

|

Apr 25 2018, 18:04 Apr 25 2018, 18:04

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 31-01-09

Пользователь №: 44 224

|

Цитата(ViKo @ Apr 25 2018, 21:22)  Тем, что процессор выполняет меньше команд. У нас немного разные сиcтемы. У меня нет процессора и все делает плисина. В Верилоге обратить байт этo просто byte <= byte[0+:7] Rbf ,шьется во штатную флеш из которой она же потом грузится в режиме AS.

Сообщение отредактировал rolin - Apr 25 2018, 18:04

|

|

|

|

|

|

|

|

Apr 28 2018, 20:12 Apr 28 2018, 20:12

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 31-01-09

Пользователь №: 44 224

|

Разобрался, все работает.

Оказалось, что в Верилоге byte <= byte[0+:7] не реверсирует биты, несмотря на кажущуюся логичность записи.

А вообще - берем rbf файл, пишем его по нужному адресу во флешку не забыв реверсировать биты в каждом байте и вперед, все работает.

|

|

|

|

|

|

|

|

May 2 2018, 05:27 May 2 2018, 05:27

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 31-01-09

Пользователь №: 44 224

|

Исходники проекта бутлоадера https://github.com/Dfinitski/Odyssey-2_2017...ssey_BL_2.0.zipИ программа на Питоне для ПК для работы с ним https://github.com/Dfinitski/Odyssey-2_2017...tLoader_2.0.pywБутлоадер реализует 4 слота для хранения прошивок, один из них используется для загрузки самого бутлоадера ( по нулевому адресу). Написано для специфичного девайса, коряво, но работает. Модуль Remote не обновлять, его предупреждение игнорировать, иначе не будет работать, не знаю почему. Также может представлять интерес Gigabit Ethernet trough RGMII стек с ARP, ICMP, UDP уровнями.

|

|

|

|

|

|

|

|

May 2 2018, 12:03 May 2 2018, 12:03

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 31-01-09

Пользователь №: 44 224

|

Цитата(ViKo @ May 2 2018, 10:07)  А просто выбрать биты Y = X[0:7]? Ну так это то же самое. Будет выбран указанный диапазон линий, старший к старшему, младший к младшему, без реверса. Видимо сама структура Плис не позволяет так вольно обходиться с адрессацией.

|

|

|

|

|

|

|

|

May 2 2018, 12:33 May 2 2018, 12:33

|

Универсальный солдатик

Группа: Модераторы

Сообщений: 8 634

Регистрация: 1-11-05

Из: Минск

Пользователь №: 10 362

|

Цитата(rolin @ May 2 2018, 15:03)  Ну так это то же самое. Будет выбран указанный диапазон линий, старший к старшему, младший к младшему, без реверса.

Видимо сама структура Плис не позволяет так вольно обходиться с адрессацией. Обычно биты нумеруются так [MSB:LSB]. И, если заметили, я присвоил игреку икс. Т.е., напишите так, конкретно, и биты прицепятся, как нужно. Y[7:0] = X[0:7]. Это же просто "провода".

|

|

|

|

|

|

|

|

May 2 2018, 15:12 May 2 2018, 15:12

|

Участник

Группа: Участник

Сообщений: 36

Регистрация: 31-01-09

Пользователь №: 44 224

|

Цитата(ViKo @ May 2 2018, 16:33)  Обычно биты нумеруются так [MSB:LSB]. И, если заметили, я присвоил игреку икс. Т.е., напишите так, конкретно, и биты прицепятся, как нужно.

Y[7:0] = X[0:7].

Это же просто "провода". Увы, нет. В Верилоге идентично, что 7:0 что 0:7. Вы просто указываете необходимый диапазон адресов в удобной для вас форме, но реверса не будет. Эта оказия часто обсуждается, можете по стековерфлоу пройтись. Говорят, что в SystemVerilog есть спецкоманда компилятора для реверса адрессации, но я не особо специалист в этих вещах, просто хобби.

|

|

|

|

|

|

|

|

May 3 2018, 04:49 May 3 2018, 04:49

|

Местный

Группа: Свой

Сообщений: 498

Регистрация: 4-10-04

Из: Нижний Новгород

Пользователь №: 771

|

Цитата(rolin @ May 2 2018, 18:12)  В Верилоге идентично, что 7:0 что 0:7. а можно об этом поподробнее, где это написано???? я просто хочу сказать, что это не идентично в 1ом случае старший бит имеет индекс 7, во 2ом - 0

--------------------

Человек - это существо, которое охотнее всего рассуждает о том, в чем меньше всего разбирается.

|

|

|

|

|

|

|

|

May 3 2018, 16:51 May 3 2018, 16:51

|

Знающий

Группа: Свой

Сообщений: 654

Регистрация: 24-01-07

Из: Воронеж

Пользователь №: 24 737

|

Цитата(rolin @ May 2 2018, 18:12)  Увы, нет. В Верилоге идентично, что 7:0 что 0:7. Бред сивой кобылы. Ну не нравится, напишите так: Y[7:0] = {X[0], X[1], X[2], X[3], X[4], X[5], X[6], X[7]}. Провода, они и есть провода.

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|