| |

PISO VHDL PISO VHDL, PISO VHDL |

|

|

|

|

Apr 12 2018, 12:16 Apr 12 2018, 12:16

|

Группа: Участник

Сообщений: 8

Регистрация: 10-01-18

Пользователь №: 100 998

|

Всем день добрый. Необходима некоторая помощь с регистром, т.к. я уже не могу найти где моя ошибка. CODE library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity shift is

Port ( clk : in STD_LOGIC;

reset: in STD_LOGIC;

load : in STD_LOGIC;

shift: in STD_LOGIC;

D : in STD_LOGIC_VECTOR (7 downto 0);

Q : out STD_LOGIC);

end shift;

architecture Behavioral of shift is

signal sr: std_logic_vector(7 downto 0) := (others=>'0');

begin

process (clk,load,D,)

begin

if (load = '1') then

sr <= D;

elsif (clk'event and clk = '1') then

if (shift = '1') then

sr <= sr(0) & sr(7 downto 1);

end if;

end if;

end process;

Q <= sr(0);

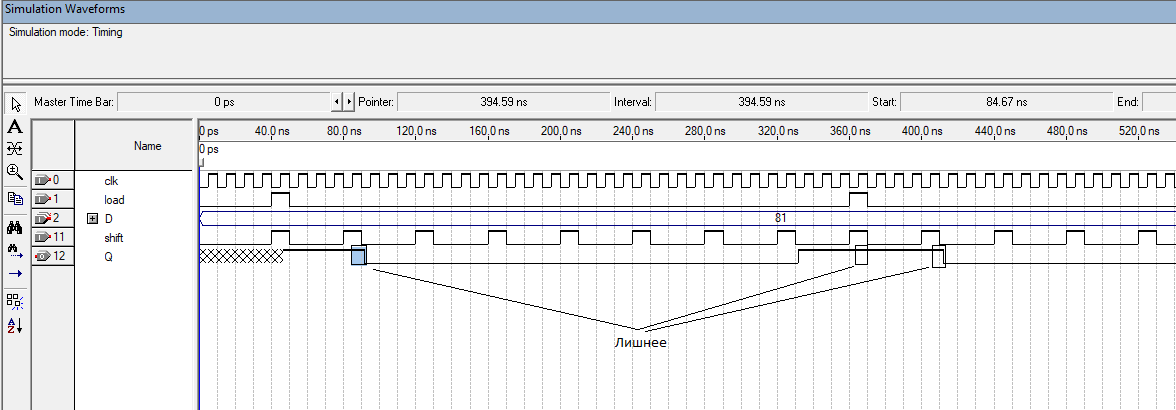

end Behavioral; В общем проблема состоит в том, что на выходе выводит неверный сигнал. На скрине я выделил лишнее, т.е. он заканчивает этот сигнал по спаду, хотя должен по фронту по сути идти  Да и второй сигнал тоже смещен на 1 такт по clk

|

|

|

|

|

|

|

|

Ответов

|

|

Apr 12 2018, 12:59 Apr 12 2018, 12:59

|

Группа: Участник

Сообщений: 8

Регистрация: 10-01-18

Пользователь №: 100 998

|

Цитата(iosifk @ Apr 12 2018, 15:48)  У Вас на картинке load и shift присутствуют одновременно. Так должно быть? И что при этом происходит? Кто имеет более высокий приоритет? Shift - это тот же enable, просто разрешающий сигнал Load - использую как сигнал загрузки Цитата(Burenkov Sergey @ Apr 12 2018, 15:47)  У вас timing simulation, сделайте behavioral

С кодом все ок, должно работать В квартусовском симуляторе могу выбрать только timing и functional

|

|

|

|

|

|

|

|

Apr 12 2018, 13:03 Apr 12 2018, 13:03

|

Частый гость

Группа: Участник

Сообщений: 86

Регистрация: 10-01-13

Пользователь №: 75 145

|

Цитата(MAXHAX @ Apr 12 2018, 15:59)  В квартусовском симуляторе могу выбрать только timing и functional functional значит выбирайте

|

|

|

|

|

|

|

|

Apr 12 2018, 13:20 Apr 12 2018, 13:20

|

Группа: Участник

Сообщений: 8

Регистрация: 10-01-18

Пользователь №: 100 998

|

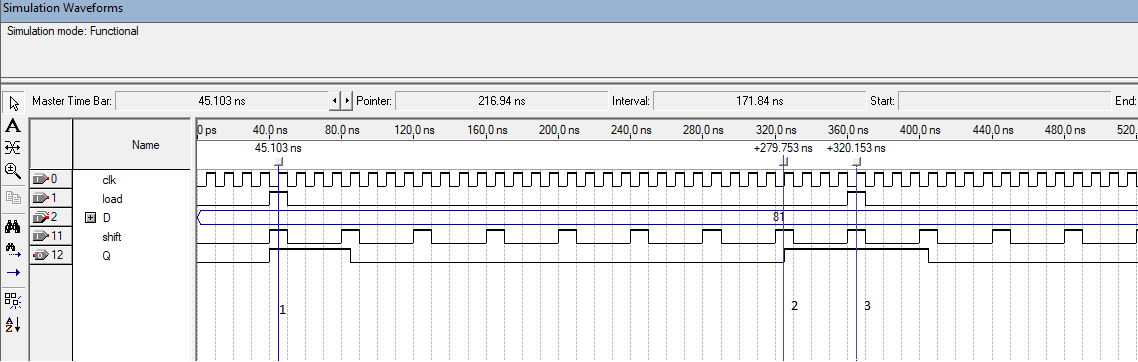

Цитата(Burenkov Sergey @ Apr 12 2018, 16:03)  functional значит выбирайте теперь здесь идет не по clk, а по load идет, на скрине видно что по первому и 3-ему time bar они идут неверно  Цитата(iosifk @ Apr 12 2018, 16:11)  Ответ не принимается!

Так все таки, когда два эти сигнала действуют одновременно, что происходит? Сдвиг или загрузка? Насколько я понимаю, чтобы ачать разрешать сдвигать, сперва должна произойти загрузка, значит load в большем приоритете?

|

|

|

|

|

|

|

|

Apr 12 2018, 13:24 Apr 12 2018, 13:24

|

Частый гость

Группа: Участник

Сообщений: 135

Регистрация: 19-10-13

Пользователь №: 78 795

|

Цитата(MAXHAX @ Apr 12 2018, 16:20)  теперь здесь идет не по clk, а по load идет, на скрине видно что по первому и 3-ему time bar они идут неверно Почему неверно? Сейчас все четко.

|

|

|

|

|

|

|

|

Apr 12 2018, 13:31 Apr 12 2018, 13:31

|

Группа: Участник

Сообщений: 8

Регистрация: 10-01-18

Пользователь №: 100 998

|

Цитата(Tausinov @ Apr 12 2018, 16:24)  Почему неверно? Сейчас все четко. мне надо, чтобы перед 3-им time bar было пол такта в нуле Цитата(Burenkov Sergey @ Apr 12 2018, 16:24)  load у вас асинхронный, так и будет. Хотите чтоб он был синхронный, перенесите его внутрь if (clk'event and clk = '1') что-то я вообще не могу придумать как это сделать, вообще под конец дня голова не варит

|

|

|

|

|

|

|

|

Apr 12 2018, 13:33 Apr 12 2018, 13:33

|

Частый гость

Группа: Участник

Сообщений: 86

Регистрация: 10-01-13

Пользователь №: 75 145

|

Цитата(MAXHAX @ Apr 12 2018, 16:31)  мне надо, чтобы перед 3-им time bar было пол такта в нуле

что-то я вообще не могу придумать как это сделать, вообще под конец дня голова не варит У вас данные при загрузке 0x81, младший бит в 1. Сделайте его в 0 и тогда будет пол такта в 0

|

|

|

|

|

|

Сообщений в этой теме

MAXHAX PISO VHDL Apr 12 2018, 12:16 MAXHAX PISO VHDL Apr 12 2018, 12:16  Burenkov Sergey У вас timing simulation, сделайте behavioral

С код... Apr 12 2018, 12:47 Burenkov Sergey У вас timing simulation, сделайте behavioral

С код... Apr 12 2018, 12:47         MAXHAX Цитата(Burenkov Sergey @ Apr 12 2018, 16... Apr 12 2018, 13:58 MAXHAX Цитата(Burenkov Sergey @ Apr 12 2018, 16... Apr 12 2018, 13:58          iosifk Цитата(MAXHAX @ Apr 12 2018, 16:58) ок, а... Apr 12 2018, 14:01 iosifk Цитата(MAXHAX @ Apr 12 2018, 16:58) ок, а... Apr 12 2018, 14:01           MAXHAX Цитата(iosifk @ Apr 12 2018, 17:01) А что... Apr 12 2018, 14:07 MAXHAX Цитата(iosifk @ Apr 12 2018, 17:01) А что... Apr 12 2018, 14:07            iosifk Цитата(MAXHAX @ Apr 12 2018, 17:07) от вс... Apr 12 2018, 14:12 iosifk Цитата(MAXHAX @ Apr 12 2018, 17:07) от вс... Apr 12 2018, 14:12      Burenkov Sergey Цитата(MAXHAX @ Apr 12 2018, 16:20) тепер... Apr 12 2018, 13:24 Burenkov Sergey Цитата(MAXHAX @ Apr 12 2018, 16:20) тепер... Apr 12 2018, 13:24    iosifk Цитата(MAXHAX @ Apr 12 2018, 15:59) Shift... Apr 12 2018, 13:11 iosifk Цитата(MAXHAX @ Apr 12 2018, 15:59) Shift... Apr 12 2018, 13:11  Tausinov На первый взгляд, никакого криминала в коде нет. Е... Apr 12 2018, 12:49 Tausinov На первый взгляд, никакого криминала в коде нет. Е... Apr 12 2018, 12:49  Tausinov Цитата(MAXHAX @ Apr 12 2018, 16:31) мне н... Apr 12 2018, 14:09 Tausinov Цитата(MAXHAX @ Apr 12 2018, 16:31) мне н... Apr 12 2018, 14:09

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|