CODE

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity shift is

Port ( clk : in STD_LOGIC;

reset: in STD_LOGIC;

load : in STD_LOGIC;

shift: in STD_LOGIC;

D : in STD_LOGIC_VECTOR (7 downto 0);

Q : out STD_LOGIC);

end shift;

architecture Behavioral of shift is

signal sr: std_logic_vector(7 downto 0) := (others=>'0');

begin

process (clk,load,D,)

begin

if (load = '1') then

sr <= D;

elsif (clk'event and clk = '1') then

if (shift = '1') then

sr <= sr(0) & sr(7 downto 1);

end if;

end if;

end process;

Q <= sr(0);

end Behavioral;

use IEEE.STD_LOGIC_1164.ALL;

entity shift is

Port ( clk : in STD_LOGIC;

reset: in STD_LOGIC;

load : in STD_LOGIC;

shift: in STD_LOGIC;

D : in STD_LOGIC_VECTOR (7 downto 0);

Q : out STD_LOGIC);

end shift;

architecture Behavioral of shift is

signal sr: std_logic_vector(7 downto 0) := (others=>'0');

begin

process (clk,load,D,)

begin

if (load = '1') then

sr <= D;

elsif (clk'event and clk = '1') then

if (shift = '1') then

sr <= sr(0) & sr(7 downto 1);

end if;

end if;

end process;

Q <= sr(0);

end Behavioral;

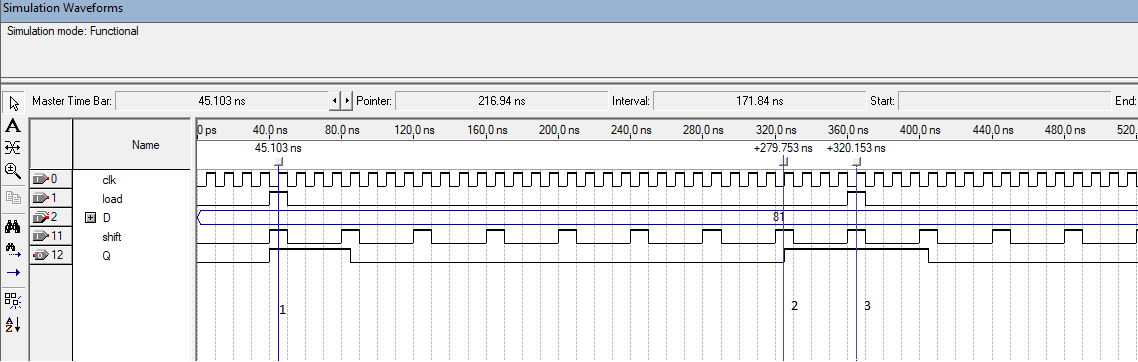

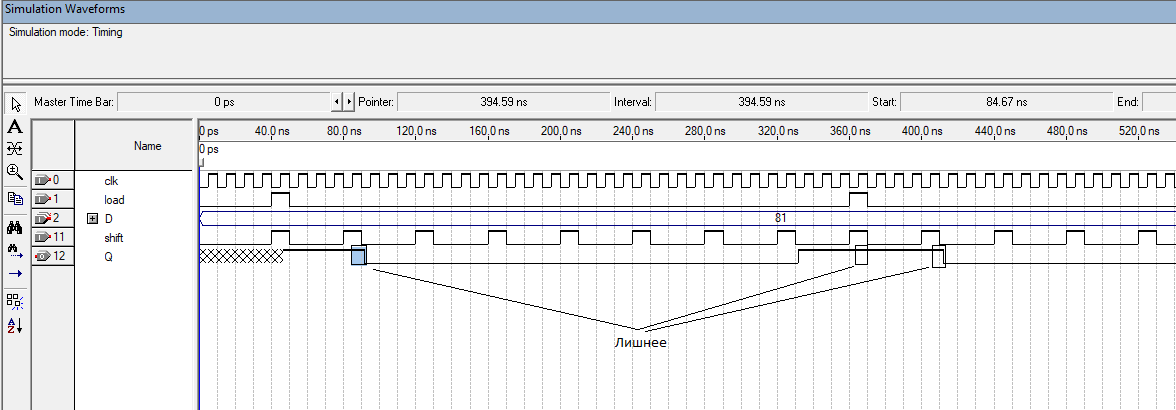

В общем проблема состоит в том, что на выходе выводит неверный сигнал. На скрине я выделил лишнее, т.е. он заканчивает этот сигнал по спаду, хотя должен по фронту по сути идти

Да и второй сигнал тоже смещен на 1 такт по clk