| |

Проблемы с выводом сигнала с ПЛИС Проблемы с выводом сигнала с ПЛИС |

|

|

|

|

Jul 9 2018, 12:44 Jul 9 2018, 12:44

|

Участник

Группа: Участник

Сообщений: 29

Регистрация: 3-06-15

Пользователь №: 86 991

|

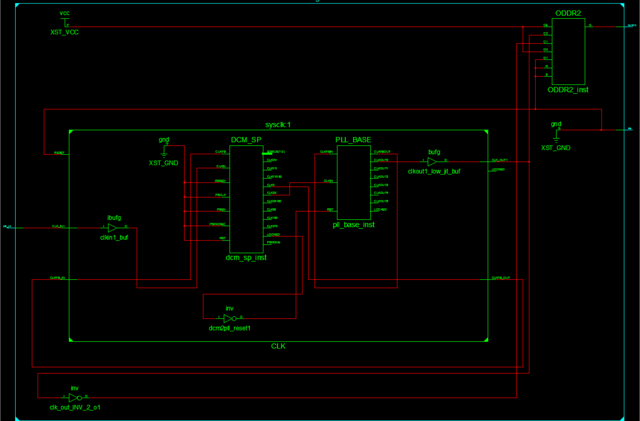

Здравствуйте Пользователи. У меня стоит задача выдать с ПЛИС меандр с частотой 100МГц. На вход ПЛИС (xc6slx100) приходит меандр 50 МГц с кварца. Как показано на приложенном рисунке, я пропускаю сигнал через DCM -> PLL -> ODDR2, чтобы умножить сигнал в два раза. ODDR2 был прикручен, так как при компиляции проекта, шли ошибки о невозможности вывести данный сигнал через обычный IO. Проблема закралась в том, что при выводе сигнала, я получаю вместо меандра с частотой 100МГц получаю синус 100МГц. Прошу дать совета по направлению поиска ошибок. Всю недостающую информацию предоставлю позднее, так как не знаю, что потребуется для решения.

|

|

|

|

|

|

|

|

Ответов

|

|

Jul 10 2018, 07:23 Jul 10 2018, 07:23

|

Участник

Группа: Участник

Сообщений: 29

Регистрация: 3-06-15

Пользователь №: 86 991

|

UPD!

Ранее я смотрел сигнал неосредственно в точке, между выводом ПЛИС и входом шинного формирователя, где и видел свой синус. Но ответ iosifk натолкнул на мысль посмотреть чисто вывод ПЛИС и вуаля, я получил свой меандр, вполне красивый, что говорит, что природа синуса кроется непосредственно в соединении ПЛИС и шинника. Данную проблему буду решать самостоятельно, но от вероятных советов или мыслей не откажусь.

|

|

|

|

|

|

|

|

Jul 10 2018, 10:52 Jul 10 2018, 10:52

|

Участник

Группа: Участник

Сообщений: 29

Регистрация: 3-06-15

Пользователь №: 86 991

|

Цитата(XVR @ Jul 10 2018, 13:42)  А какой у вас шинный формирователь? 100MHz не всякий шинник потянет (в том числе может и вход посадить) 74lvt125

|

|

|

|

|

|

|

|

Jul 11 2018, 18:37 Jul 11 2018, 18:37

|

Участник

Группа: Участник

Сообщений: 29

Регистрация: 3-06-15

Пользователь №: 86 991

|

Цитата(XVR @ Jul 11 2018, 14:40)  Во первых у неё есть так называемый 'bus hold' (по входу). Это значит, что она будет пытаться изнасиловать перетянуть выход FPGA, слава богу что хоть ток не очень большой (порядка 150мка), но на 100MHz это последствия могут быть плачевными. Во вторых у неё воемя распространения сигнала 4ns (в худшем случае). Умножаем на 2 (т.к. фронта 2) - получаем 8ns, а 100MHz - это 10ns. Так что на выходе точно будет нечто напоминающее синусоиду  Насчет качества пропускаемого сигнала я посмотрю отдельным экспериментом, подав на нее сигнал с генератора и посмотрев, что собственно будет на выходе, там думаю можно будет думать, но я этот парамтер tPHL воспринимал лишь как время задержки от входа до выхода, но после вашего комментария пересмотрел графики и вы правы насчет 100 МГц.

|

|

|

|

|

|

Сообщений в этой теме

Naixrim Проблемы с выводом сигнала с ПЛИС Jul 9 2018, 12:44 Naixrim Проблемы с выводом сигнала с ПЛИС Jul 9 2018, 12:44  iosifk Цитата(Naixrim @ Jul 9 2018, 15:44) получ... Jul 9 2018, 12:54 iosifk Цитата(Naixrim @ Jul 9 2018, 15:44) получ... Jul 9 2018, 12:54   Naixrim Цитата(iosifk @ Jul 9 2018, 15:54) Начнем... Jul 9 2018, 13:36 Naixrim Цитата(iosifk @ Jul 9 2018, 15:54) Начнем... Jul 9 2018, 13:36    iosifk Цитата(Naixrim @ Jul 9 2018, 16:36) Станд... Jul 10 2018, 07:32 iosifk Цитата(Naixrim @ Jul 9 2018, 16:36) Станд... Jul 10 2018, 07:32     Naixrim Цитата(iosifk @ Jul 10 2018, 10:32) Я не ... Jul 10 2018, 07:43 Naixrim Цитата(iosifk @ Jul 10 2018, 10:32) Я не ... Jul 10 2018, 07:43      iosifk Цитата(Naixrim @ Jul 10 2018, 10:43) Это ... Jul 10 2018, 08:33 iosifk Цитата(Naixrim @ Jul 10 2018, 10:43) Это ... Jul 10 2018, 08:33       andrew_b Цитата(iosifk @ Jul 10 2018, 11:33) Вот ф... Jul 10 2018, 09:11 andrew_b Цитата(iosifk @ Jul 10 2018, 11:33) Вот ф... Jul 10 2018, 09:11        iosifk Цитата(andrew_b @ Jul 10 2018, 12:11) Зач... Jul 10 2018, 09:28 iosifk Цитата(andrew_b @ Jul 10 2018, 12:11) Зач... Jul 10 2018, 09:28       Naixrim Цитата(iosifk @ Jul 10 2018, 11:33) Вот ф... Jul 10 2018, 09:40 Naixrim Цитата(iosifk @ Jul 10 2018, 11:33) Вот ф... Jul 10 2018, 09:40        iosifk Цитата(Naixrim @ Jul 10 2018, 12:40) А та... Jul 10 2018, 09:49 iosifk Цитата(Naixrim @ Jul 10 2018, 12:40) А та... Jul 10 2018, 09:49  Inanity Naixrim, я думаю, что у вас просто линия не соглас... Jul 10 2018, 13:09 Inanity Naixrim, я думаю, что у вас просто линия не соглас... Jul 10 2018, 13:09   iosifk Цитата(Inanity @ Jul 10 2018, 16:09) Naix... Jul 10 2018, 13:27 iosifk Цитата(Inanity @ Jul 10 2018, 16:09) Naix... Jul 10 2018, 13:27    Inanity Цитата(iosifk @ Jul 10 2018, 16:27) А у Т... Jul 10 2018, 15:33 Inanity Цитата(iosifk @ Jul 10 2018, 16:27) А у Т... Jul 10 2018, 15:33   Naixrim Цитата(Inanity @ Jul 10 2018, 16:09) Naix... Jul 12 2018, 12:58 Naixrim Цитата(Inanity @ Jul 10 2018, 16:09) Naix... Jul 12 2018, 12:58  Naixrim По сути, я могу попробовать дальше насиловать плат... Jul 10 2018, 17:48 Naixrim По сути, я могу попробовать дальше насиловать плат... Jul 10 2018, 17:48   iosifk Цитата(Naixrim @ Jul 10 2018, 20:48) Насч... Jul 10 2018, 18:02 iosifk Цитата(Naixrim @ Jul 10 2018, 20:48) Насч... Jul 10 2018, 18:02    Alex77 Цитата(iosifk @ Jul 10 2018, 21:02) Найди... Jul 10 2018, 18:26 Alex77 Цитата(iosifk @ Jul 10 2018, 21:02) Найди... Jul 10 2018, 18:26     iosifk Цитата(Alex77 @ Jul 10 2018, 21:26) оно ?... Jul 10 2018, 18:31 iosifk Цитата(Alex77 @ Jul 10 2018, 21:26) оно ?... Jul 10 2018, 18:31  Naixrim У меня есть эта книга в печатном варианте, но тако... Jul 10 2018, 21:10 Naixrim У меня есть эта книга в печатном варианте, но тако... Jul 10 2018, 21:10

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|