| |

FIFO на VHDL FIFO на VHDL |

|

|

|

|

Ответов

|

|

Aug 2 2018, 20:30 Aug 2 2018, 20:30

|

Частый гость

Группа: Свой

Сообщений: 199

Регистрация: 17-12-04

Из: Миасс

Пользователь №: 1 519

|

И всё таки, что вы хотите сделать? Есть какая-то RAM. Есть какое-то Fifo. Зачем их нужно скрещивать? Ну хорошо, почему нельзя сделать Ram с разной разрядностью входа и выхода? Ну а сделать FIFO с разной разрядностью входа и выхода в чём проблема?

|

|

|

|

|

|

|

|

Aug 3 2018, 06:28 Aug 3 2018, 06:28

|

Профессионал

Группа: Участник

Сообщений: 1 778

Регистрация: 29-03-12

Пользователь №: 71 075

|

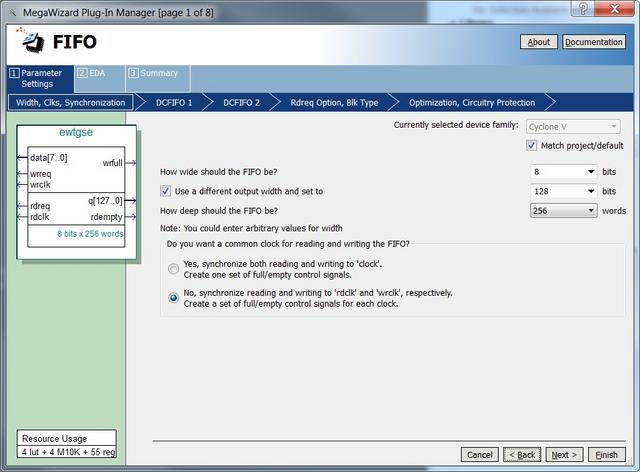

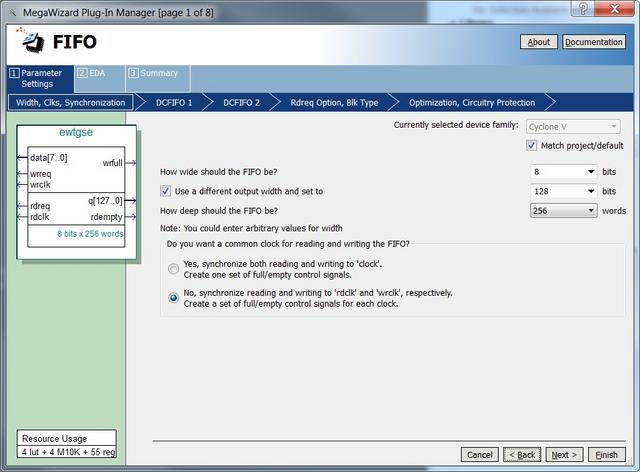

Цитата(andk @ Aug 3 2018, 01:30)  И всё таки, что вы хотите сделать? Есть какая-то RAM. Есть какое-то Fifo. Зачем их нужно скрещивать? Ну хорошо, почему нельзя сделать Ram с разной разрядностью входа и выхода? Ну а сделать FIFO с разной разрядностью входа и выхода в чём проблема?  я пришел к тому же выводу - ФИФО наше все. сериально загонять байты по 13 штук и считывать тоже по 13. единственно я не понимаю - я должен стробировать сигнал wrreq? иначе как ФИФО знает что нужно принять следующий байт? и то же самое при чтении - нужно стробировать rdreq?

|

|

|

|

|

|

|

|

Aug 3 2018, 10:47 Aug 3 2018, 10:47

|

Профессионал

Группа: Участник

Сообщений: 1 778

Регистрация: 29-03-12

Пользователь №: 71 075

|

Цитата(Flip-fl0p @ Aug 3 2018, 11:39)  Рассматривайте сигнал wrreq - как сигнал валидности данных. Т.е подали на шину данные, и одновременно с ними выставили сигнал wrreq на 1 такт, чтобы данные записались в FIFO.

Вообще FIFO не знает ничего, кроме того, сколько в него записано слов, и пустой он или полный. Вы им сами управляете записью и чтением FIFO. Не совсем понимю, что Вы имеете ввиду когда говорите про стробирование wrreq и rdreq. это я и имею в виду - выставить wrreq и потом опустить. и то же самое при чтении, я так понимаю перед каждым байтом выставить rdreq - он вытолкнет байт наружу и опустить rdreq.

Сообщение отредактировал Jenya7 - Aug 3 2018, 10:48

|

|

|

|

|

|

Сообщений в этой теме

Jenya7 FIFO на VHDL Aug 1 2018, 14:36 Jenya7 FIFO на VHDL Aug 1 2018, 14:36  andk Эээ.. Что вы имели ввиду под словом "единица... Aug 1 2018, 16:03 andk Эээ.. Что вы имели ввиду под словом "единица... Aug 1 2018, 16:03   Jenya7 Цитата(andk @ Aug 1 2018, 22:03) Эээ.. Чт... Aug 2 2018, 05:13 Jenya7 Цитата(andk @ Aug 1 2018, 22:03) Эээ.. Чт... Aug 2 2018, 05:13  Flip-fl0p Вместо того чтобы выбирать значения из списка можн... Aug 2 2018, 05:20 Flip-fl0p Вместо того чтобы выбирать значения из списка можн... Aug 2 2018, 05:20   Jenya7 Цитата(Flip-fl0p @ Aug 2 2018, 11:20... Aug 2 2018, 05:22 Jenya7 Цитата(Flip-fl0p @ Aug 2 2018, 11:20... Aug 2 2018, 05:22    Flip-fl0p Цитата(Jenya7 @ Aug 2 2018, 08:22) а как ... Aug 2 2018, 05:30 Flip-fl0p Цитата(Jenya7 @ Aug 2 2018, 08:22) а как ... Aug 2 2018, 05:30     Jenya7 Цитата(Flip-fl0p @ Aug 2 2018, 11:30... Aug 2 2018, 05:34 Jenya7 Цитата(Flip-fl0p @ Aug 2 2018, 11:30... Aug 2 2018, 05:34    quato_a Цитата(Jenya7 @ Aug 2 2018, 08:22) а как ... Aug 2 2018, 05:40 quato_a Цитата(Jenya7 @ Aug 2 2018, 08:22) а как ... Aug 2 2018, 05:40     Jenya7 Цитата(quato_a @ Aug 2 2018, 11:40) Напиш... Aug 2 2018, 05:56 Jenya7 Цитата(quato_a @ Aug 2 2018, 11:40) Напиш... Aug 2 2018, 05:56      quato_a Цитата(Jenya7 @ Aug 2 2018, 08:56) у меня... Aug 2 2018, 06:02 quato_a Цитата(Jenya7 @ Aug 2 2018, 08:56) у меня... Aug 2 2018, 06:02      RobFPGA Приветствую!

Цитата(Jenya7 @ Aug 2 2018,... Aug 2 2018, 06:15 RobFPGA Приветствую!

Цитата(Jenya7 @ Aug 2 2018,... Aug 2 2018, 06:15  Jenya7 А как вам такое решение?

Я создал двухмерный масси... Aug 2 2018, 06:15 Jenya7 А как вам такое решение?

Я создал двухмерный масси... Aug 2 2018, 06:15   andrew_b Цитата(andk @ Aug 2 2018, 23:30) Ну а сде... Aug 3 2018, 04:58 andrew_b Цитата(andk @ Aug 2 2018, 23:30) Ну а сде... Aug 3 2018, 04:58      Flip-fl0p Цитата(Jenya7 @ Aug 3 2018, 13:47) это я ... Aug 4 2018, 08:14 Flip-fl0p Цитата(Jenya7 @ Aug 3 2018, 13:47) это я ... Aug 4 2018, 08:14       Jenya7 Цитата(Flip-fl0p @ Aug 4 2018, 14:14... Aug 5 2018, 04:45 Jenya7 Цитата(Flip-fl0p @ Aug 4 2018, 14:14... Aug 5 2018, 04:45        Flip-fl0p Цитата(Jenya7 @ Aug 5 2018, 07:45) спасиб... Aug 5 2018, 10:06 Flip-fl0p Цитата(Jenya7 @ Aug 5 2018, 07:45) спасиб... Aug 5 2018, 10:06        RobFPGA Приветствую!

Цитата(Jenya7 @ Aug 5 2018, ... Aug 5 2018, 12:07 RobFPGA Приветствую!

Цитата(Jenya7 @ Aug 5 2018, ... Aug 5 2018, 12:07  Jenya7 сделал ФИФОКодcomponent fifo IS port

(

c... Aug 5 2018, 13:46 Jenya7 сделал ФИФОКодcomponent fifo IS port

(

c... Aug 5 2018, 13:46  Flip-fl0p Ничего не понял, что Вы хотите сделать ! Aug 5 2018, 14:21 Flip-fl0p Ничего не понял, что Вы хотите сделать ! Aug 5 2018, 14:21   Jenya7 Цитата(Flip-fl0p @ Aug 5 2018, 20:21... Aug 5 2018, 14:23 Jenya7 Цитата(Flip-fl0p @ Aug 5 2018, 20:21... Aug 5 2018, 14:23    Flip-fl0p Цитата(Jenya7 @ Aug 5 2018, 17:23) записа... Aug 5 2018, 14:28 Flip-fl0p Цитата(Jenya7 @ Aug 5 2018, 17:23) записа... Aug 5 2018, 14:28  Jenya7 кхм...даже стесняюсь спросить...а кто то вообще ра... Aug 6 2018, 05:57 Jenya7 кхм...даже стесняюсь спросить...а кто то вообще ра... Aug 6 2018, 05:57   Flip-fl0p Цитата(Jenya7 @ Aug 6 2018, 08:57) кхм...... Aug 6 2018, 06:12 Flip-fl0p Цитата(Jenya7 @ Aug 6 2018, 08:57) кхм...... Aug 6 2018, 06:12   quato_a Цитата(Jenya7 @ Aug 6 2018, 08:57) кхм...... Aug 6 2018, 07:01 quato_a Цитата(Jenya7 @ Aug 6 2018, 08:57) кхм...... Aug 6 2018, 07:01   RobFPGA Приветствую!

Цитата(Jenya7 @ Aug 6 2018, ... Aug 6 2018, 07:36 RobFPGA Приветствую!

Цитата(Jenya7 @ Aug 6 2018, ... Aug 6 2018, 07:36    Tpeck Цитата(RobFPGA @ Aug 6 2018, 10:36) Приве... Aug 7 2018, 07:42 Tpeck Цитата(RobFPGA @ Aug 6 2018, 10:36) Приве... Aug 7 2018, 07:42

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|