| |

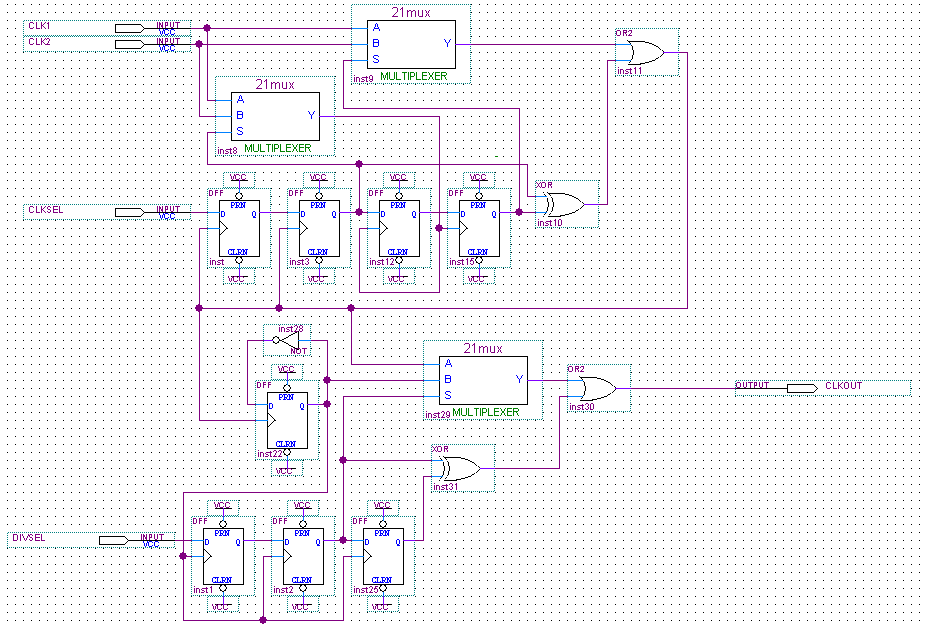

Переключатель двух независимых клоков Переключатель двух независимых клоков, Насколько корректная реализация? |

|

|

|

|

Feb 14 2007, 01:25 Feb 14 2007, 01:25

|

Частый гость

Группа: Участник

Сообщений: 127

Регистрация: 18-10-06

Пользователь №: 21 418

|

Задача: Имеем 2 независимых клока (скажем, 20 и 24 МГц), требуется сделать переключататель, который на выходе даёт 20,10,24,12 МГц (выбор - 2 асинхронными сигналами). Требуется, чтобы на выходе не появлялось импульсов короче, чем полупериод самого быстрого входного клока. Родил вот такую схему (нарисовано в квартусе)  , насколько она корректна? PS: вполне понимаю, что схема асинхронная и на очень быстрых клоках всё равно возможны глюки. Но макс. частота такая, как указана выше, а моделирование вроде бы не выявляет глитчей (целевой чип - epm3032).

Сообщение отредактировал LordVader - Feb 14 2007, 01:27

|

|

|

|

|

|

|

|

Ответов

|

|

Feb 15 2007, 09:57 Feb 15 2007, 09:57

|

Гуру

Группа: Свой

Сообщений: 2 435

Регистрация: 6-10-04

Из: Петербург

Пользователь №: 804

|

переключатель F - F/2 безглитчевый... вроде бы

////////////////////////////////////////////

В этом вроде бы все и заложено. Вы выносите на обсуждение схему, анализ которой требует больших временных затрат. У кого они есть. При этом игнорируете схемные решения с приличным анализом.

Главное отличие Вашей и другой схем это в тактировании триггеров.

Но самое главное, такая схема некорректна по определению. Без констрейнов по всем путям Вы долны получить сплошные clock skew, некорректные clock hold.

Я в лоб первел. Если хотите посмотрите

module switch_clocks

(

input clock1,

input clock0,

input select,

input delitel,

output out_clock_end

);

reg reg_clock1_a, reg_clock1_b;

reg reg_clock0_a, reg_clock0_b;

reg reg_clock1_aa, reg_clock1_bb;

reg reg_clock0_aa, reg_clock0_bb;

reg reg_del;

wire clock0a;

wire a, b, c, d;

wire aa, bb, cc, dd;

always @(posedge clock1)

begin

reg_clock1_a <= a;

end

always @(negedge clock1)

begin

reg_clock1_b <= reg_clock1_a;

end

always @(posedge clock0)

begin

reg_clock0_a <= b;

end

always @(negedge clock0)

begin

reg_clock0_b <= reg_clock0_a;

end

assign a = ~reg_clock0_b & select;

assign b = ~reg_clock1_b & ~select;

assign c = reg_clock1_b & clock1;

assign d = reg_clock0_b & clock0;

assign clock1a = c | d;

always @(posedge clock1a)

begin

reg_del <= ~reg_del;

end

assign clock0a = reg_del;

always @(posedge clock1a)

begin

reg_clock1_aa <= aa;

end

always @(negedge clock1a)

begin

reg_clock1_bb <= reg_clock1_aa;

end

always @(posedge clock0a)

begin

reg_clock0_aa <= bb;

end

always @(negedge clock0a)

begin

reg_clock0_bb <= reg_clock0_aa;

end

assign aa = ~reg_clock0_bb & delitel;

assign bb = ~reg_clock1_bb & ~delitel;

assign cc = reg_clock1_bb & clock1a;

assign dd = reg_clock0_bb & clock0a;

assign out_clock_end = cc | dd;

endmodule

|

|

|

|

|

|

|

|

Feb 18 2007, 10:56 Feb 18 2007, 10:56

|

Частый гость

Группа: Участник

Сообщений: 127

Регистрация: 18-10-06

Пользователь №: 21 418

|

Цитата(sazh @ Feb 15 2007, 09:57)  В этом вроде бы все и заложено. Вы выносите на обсуждение схему, анализ которой требует больших временных затрат. У кого они есть. При этом игнорируете схемные решения с приличным анализом.

Главное отличие Вашей и другой схем это в тактировании триггеров.

Но самое главное, такая схема некорректна по определению. Без констрейнов по всем путям Вы долны получить сплошные clock skew, некорректные clock hold. Ну я в принципе согласен, что некорректная. Но дело в том, что у меня все сигналы выбора - асинхронные, а насколько я понял, в таком случае надо использовать схему переключения для 'unrelated' клоков, даже если сами клоки 'related'. Ведь надо асинхронный сигнал через цепочку из 2 триггеров пропускать. Цитата Я в лоб первел. Если хотите посмотрите Спасибо! Вопрос - почему у вас Цитата always @(posedge clock1)

begin

reg_clock1_a <= a;

end

always @(negedge clock1)

begin

reg_clock1_b <= reg_clock1_a;

end то posedge, то negedge? В этом какой-то глубинный смысл именно для данной схемы, или просто, чтоб быстрее проходило?

|

|

|

|

|

|

Сообщений в этой теме

LordVader Переключатель двух независимых клоков Feb 14 2007, 01:25 LordVader Переключатель двух независимых клоков Feb 14 2007, 01:25  SM Вот корректная схема (делать было нечего, нарисова... Feb 14 2007, 03:06 SM Вот корректная схема (делать было нечего, нарисова... Feb 14 2007, 03:06  Victor® Цитата(LordVader @ Feb 14 2007, 02:25) За... Feb 14 2007, 09:55 Victor® Цитата(LordVader @ Feb 14 2007, 02:25) За... Feb 14 2007, 09:55  LordVader Спасибо всем!

Насколько я понял, обе схемы пе... Feb 14 2007, 14:58 LordVader Спасибо всем!

Насколько я понял, обе схемы пе... Feb 14 2007, 14:58   SM Цитата(LordVader @ Feb 14 2007, 14:58) На... Feb 14 2007, 17:42 SM Цитата(LordVader @ Feb 14 2007, 14:58) На... Feb 14 2007, 17:42  Gate Вот эта статья не поможет - вроде проще: http://ww... Feb 14 2007, 16:16 Gate Вот эта статья не поможет - вроде проще: http://ww... Feb 14 2007, 16:16  sazh еще у ксайлинкса был апнот по безглитчевому перекл... Feb 14 2007, 16:53 sazh еще у ксайлинкса был апнот по безглитчевому перекл... Feb 14 2007, 16:53  LordVader Вот что получилось.

Слева - переключатель клоков, ... Feb 15 2007, 01:29 LordVader Вот что получилось.

Слева - переключатель клоков, ... Feb 15 2007, 01:29   SM Цитата(LordVader @ Feb 15 2007, 01:29) сп... Feb 15 2007, 03:04 SM Цитата(LordVader @ Feb 15 2007, 01:29) сп... Feb 15 2007, 03:04    LordVader Цитата(SM @ Feb 15 2007, 03:04) Только во... Feb 15 2007, 09:02 LordVader Цитата(SM @ Feb 15 2007, 03:04) Только во... Feb 15 2007, 09:02  sazh Я не вникал вглубинный смысл этой схемы. Сходил по... Feb 18 2007, 11:34 sazh Я не вникал вглубинный смысл этой схемы. Сходил по... Feb 18 2007, 11:34   LordVader Цитата(sazh @ Feb 18 2007, 11:34) Обычно ... Feb 19 2007, 13:58 LordVader Цитата(sazh @ Feb 18 2007, 11:34) Обычно ... Feb 19 2007, 13:58  sazh Ну задача глобально уже поставлена и кристалл выбр... Feb 19 2007, 20:13 sazh Ну задача глобально уже поставлена и кристалл выбр... Feb 19 2007, 20:13   LordVader Цитата(sazh @ Feb 19 2007, 20:13) Ну зада... Feb 20 2007, 16:52 LordVader Цитата(sazh @ Feb 19 2007, 20:13) Ну зада... Feb 20 2007, 16:52  vetal Розница на altera : http://www.altera.ru/cgi-bin/p... Feb 20 2007, 17:21 vetal Розница на altera : http://www.altera.ru/cgi-bin/p... Feb 20 2007, 17:21   LordVader Цитата(vetal @ Feb 20 2007, 17:21) Розниц... Feb 22 2007, 13:00 LordVader Цитата(vetal @ Feb 20 2007, 17:21) Розниц... Feb 22 2007, 13:00

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|