| |

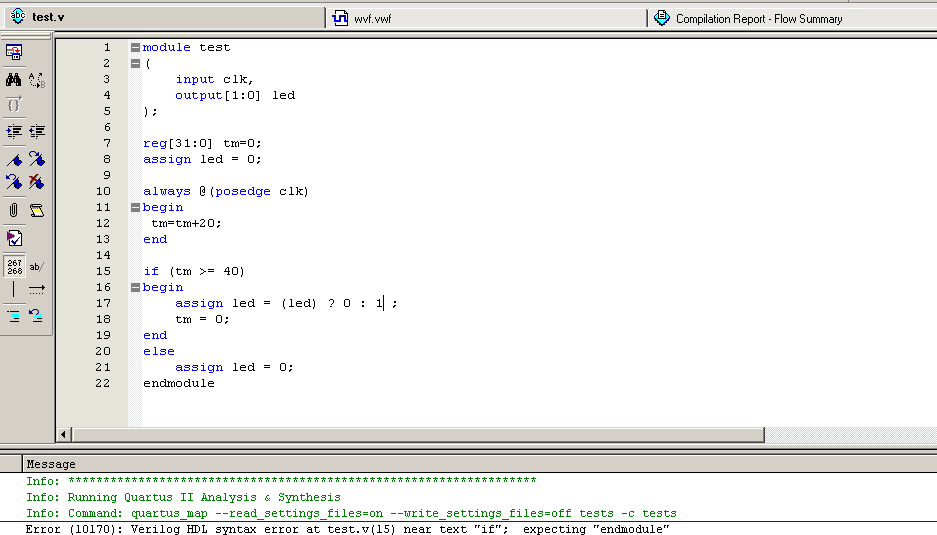

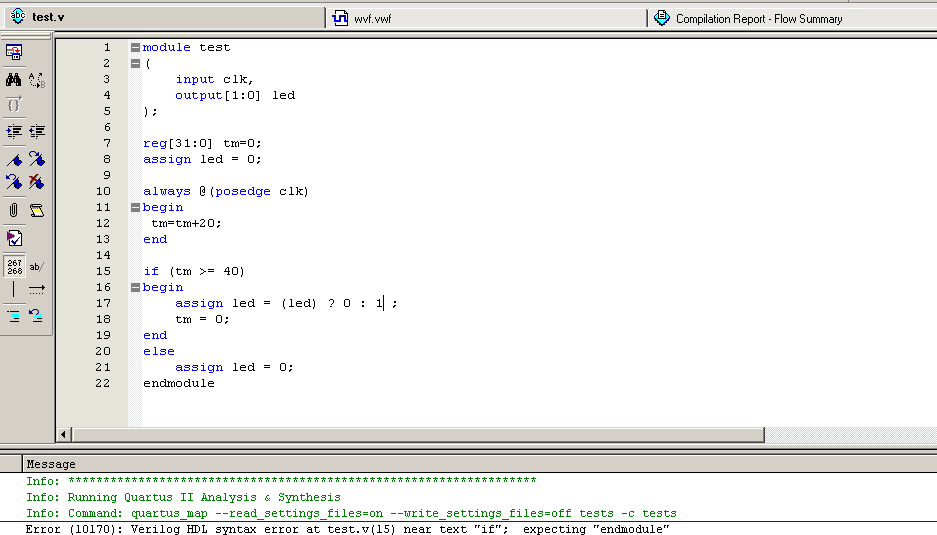

Help the noob with Verilog Help the noob with Verilog, Expected endmodule |

|

|

|

|

Jun 23 2018, 09:21 Jun 23 2018, 09:21

|

Группа: Новичок

Сообщений: 4

Регистрация: 23-06-18

Пользователь №: 105 402

|

Только начинаю изучать Verilog, столкнулся с необъяснимыми трудностями. Второй час бьюсь головой об стену, пытаясь понять причины недовольства компилятора. Знатоки, помогите, пожалуйста. Файл с исходником ниже прилепил.  Сообщение отредактировал Fantasm - Jun 23 2018, 09:23

Сообщение отредактировал Fantasm - Jun 23 2018, 09:23

Прикрепленные файлы

test.v

test.v ( 240 байт )

Кол-во скачиваний: 6

|

|

|

|

|

|

|

|

Ответов

(1 - 11)

|

|

Jun 23 2018, 10:12 Jun 23 2018, 10:12

|

Группа: Новичок

Сообщений: 4

Регистрация: 23-06-18

Пользователь №: 105 402

|

Цитата(Lmx2315 @ Jun 23 2018, 11:02)  у вас комбинация if - else сама по себе болтается, её надо в always сунуть , а assign вытащить из неё.

з.ы.

правда что вы хотите от led-a я так и не понял. Каждые 40 нс меняется состояние led. То есть это имитация светодиода, который горит в течение 40 нс каждые 40 нс. За совет - спасибо. Не знал, что нельзя вне блока always операторы совать

|

|

|

|

|

|

|

|

Jun 23 2018, 10:44 Jun 23 2018, 10:44

|

отэц

Группа: Свой

Сообщений: 1 729

Регистрация: 18-09-05

Из: Москва

Пользователь №: 8 684

|

Цитата(Fantasm @ Jun 23 2018, 13:12)  это имитация светодиода, который горит в течение 40 нс каждые 40 нс. если лед будет гореть 40 нс, каждые 40 нс - то он будет гореть непрерывно. Но я вас понял - вы на самом деле хотите чтобы у вас лед мигал со скважностью 2. Код reg led_reg=0;

always @(posedge clk)

if (tm!=40) tm<=tm+1;

else

begin

tm<=0;

led_reg<=~led_reg;

end

assign led = led_reg; Симулятора у меня под рукой нет - надеюсь не накосячил. Само - собой , тактовая 1 ГГц.

--------------------

b4edbc0f854dda469460aa1aa a5ba2bd36cbe9d4bc8f92179f 8f3fec5d9da7f0

SHA-256

|

|

|

|

|

|

|

|

Jun 23 2018, 11:00 Jun 23 2018, 11:00

|

Группа: Новичок

Сообщений: 4

Регистрация: 23-06-18

Пользователь №: 105 402

|

Можно оффтоп? Есть какие-нибудь наработки для визуализации всего этого дела? Виртуальная эмуляция платы например, которая будет мигать диодами и реагировать на клики мышью по кнопкам? Настоящую ПЛИС приобрести пока нет возможности. В инете не нашел, но, быть может, плохо искал (ибо формулировка такого запроса - дело мутное). Цитата(Lmx2315 @ Jun 23 2018, 11:44)  led_reg<=~led_reg; А что, так можно было??

|

|

|

|

|

|

|

|

Jun 23 2018, 11:41 Jun 23 2018, 11:41

|

Группа: Новичок

Сообщений: 4

Регистрация: 23-06-18

Пользователь №: 105 402

|

Цитата(iosifk @ Jun 23 2018, 12:00)  А симулятор чем плох?

Напишите модуль, напишите тестбенч и любуйтесь на здоровье. Никрасиво! :D

|

|

|

|

|

|

|

|

Jun 27 2018, 12:19 Jun 27 2018, 12:19

|

Участник

Группа: Участник

Сообщений: 31

Регистрация: 24-11-11

Пользователь №: 68 492

|

Цитата(Fantasm @ Jun 23 2018, 12:21)  Только начинаю изучать Verilog, столкнулся с необъяснимыми трудностями. Второй час бьюсь головой об стену, пытаясь понять причины недовольства компилятора. Знатоки, помогите, пожалуйста. Файл с исходником ниже прилепил.  Нет энтера после endmodule , он синим должен быть.

|

|

|

|

|

|

|

|

Jun 27 2018, 12:29 Jun 27 2018, 12:29

|

Профессионал

Группа: Свой

Сообщений: 1 214

Регистрация: 23-12-04

Пользователь №: 1 643

|

Приветствую! Цитата(umarsohod @ Jun 27 2018, 15:19)  Нет энтера после endmodule , он синим должен быть. При чем тут энтер - if не может болтаться в теле модуля сам по себе - он должен быть либо в always либо в generate блоках. Код module ...

generate

if (...) begin

assign var0 = ...

end

endgenerate

always_comb begin

if (..) begin

var1 = ...

end

end

always @(posedge clk) begin

if (..) begin

var2 <= ...

end

end

endmodule Удачи! Rob.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|