| |

|

|

DDR3: Терминация сигналов CK DDR3: Терминация сигналов CK, Выбор топологии |

|

|

|

|

Jun 4 2018, 14:39 Jun 4 2018, 14:39

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Volkov или другие специалисты, вы не подскажете с учётом влияний паразитностей корпуса на задержку?

Необходимо получить данные по задержкам внутри корпуса. Для ПЛИС (xc7a200tffg1156-2) всё просто: есть данные, выгруженные из Vivado. Например, для AL34, задержка составляет от 164,101 до 165,751 пс. Проверяем по IBIS (берём данные из Inductance и Capacitance Matrix): корень(7,22116е-11*3,76679е-12) = 164,92 пс.

Для памяти MT41J128M16JT есть как Inductance и Capacitance Matrix, так и значения в начале модели, причём эти данные не совпадают. Например, для вывода A1 индуктивность в начале указана 1,755 нГн, а в разделе Inductance Matrix 2,28 нГн. Какое значение брать?

Спасибо.

|

|

|

|

|

|

|

|

Jun 4 2018, 19:11 Jun 4 2018, 19:11

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

Изучите JEDEC STANDARD для вашей DDR3L SDRAM, поскольку она соответствует своему стандарту. Задержки там все приведены к "нулю" внутри микросхемы. Можете убедиться, перевернув и посмотрев вашу DDR3L SDRAM под микроскопом, ту многослойку с BGA шариками. Там видны меандры, трамбоны до нужных площадок, шаров BGA. Зачем вам что-то еще брать? Будет другой производитель DDR3L с другими параметрами, но все допуски и разбросы "нуля"оговорены. Думаю вам нужно заниматься другой стороной, вашей ПЛИС, задержкой внутри корпуса и трассой до вашей памяти только. Тем более что скорости у вас "никакие", допуски "огромные".

И еще поймите, что внутри всех DDR2/3/4/5 находится сложный умный логический автомат по подстройки сотни параметров по частотам, времянкам, уровням. Который сильно облегчает жизнь всем вашим точным подгонкам.

|

|

|

|

|

|

|

|

Jun 4 2018, 20:16 Jun 4 2018, 20:16

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

QUOTE (Stepanich @ Jun 4 2018, 22:37)  Aner, спасибо. То есть правило такое: выравниваем трассы только с учётом задержек внутри ПЛИС, а задержки внутри корпуса памяти не учитываем, т. к. они скомпенсированы производителем?

Ещё вопрос в тему: при разводке PCI Express x4 gen. 2 также нужно учитывать задержки внутри корпуса ПЛИС (Artix-7), или они уже скомпенсированы производителем? Еще раз изучайте стандарты того что применяете, на подсказках далеко не уедете! ... задержки внутри корпуса памяти не учитываем, т. к. они скомпенсированы и соответствуют стандартам! Задержки внутри корпуса ПЛИС не могут быть скомпенсированы которые даны пользователю для использование в различных проектах, разных конфигурациях; IP блоки их реализации могут быть исключением, также аппаратный интерфейс DDR, но это все описано и даны подробности в AN. Думаю для PCI Express x4 gen. 2 нужно учитывать задержки внутри корпуса ПЛИС (Artix-7) если в выбранной вами реализации IP Core не поддержана реализация автомата компенсации.

|

|

|

|

|

|

|

|

Jun 4 2018, 20:22 Jun 4 2018, 20:22

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

У Xilinx даже аппаратный контроллер в Zynq требует учёта задержек внутри корпуса; вот тема с их форума. По PCIe напишу здесь, когда выясню.

|

|

|

|

|

|

|

|

Jun 4 2018, 20:43 Jun 4 2018, 20:43

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

Там же вот ответ по Цинку: ... open a synthesized design ... ...The easiest way to export the pin flight time information is to open a synthesized design and in either the IO Ports or Package Pins view right click in the area, select "Export I/O Ports", select CSV, and then press OK. When you open the CSV file you'll see the PS memory interface pins in the "Site Type" column starting with "PS_". QUOTE (Stepanich @ Jun 4 2018, 23:36)  Aner, понятно. Сейчас говорим про Артикс.

Наверное, поэтому для Артикса рекомендуется задерживать такт относительно строба на 150 пс и более (при допустимой задержке от 0 пс) - так проще выбрать задержку с фиксированными дискретами. Непонял, вы что только плату разводите? А сам проект на Артиксе кто-то другой делает?

|

|

|

|

|

|

|

|

Jun 4 2018, 20:59 Jun 4 2018, 20:59

|

Гуру

Группа: Свой

Сообщений: 4 869

Регистрация: 28-02-08

Из: СПБ

Пользователь №: 35 463

|

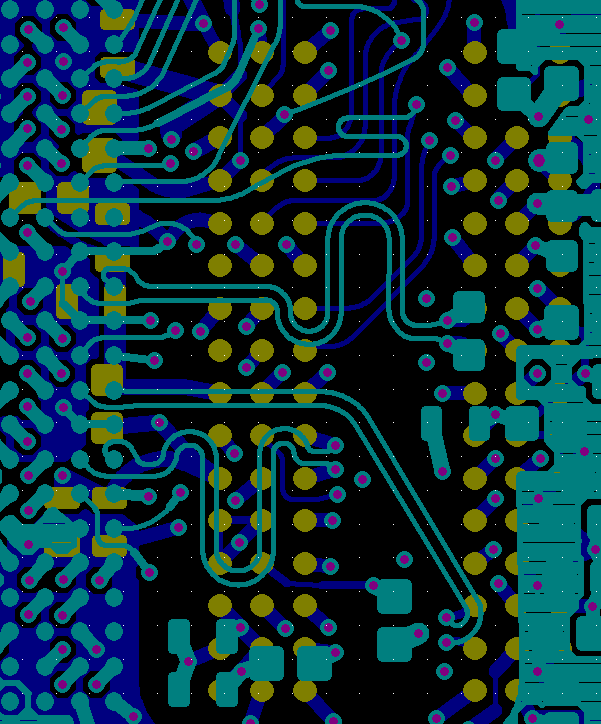

QUOTE (Stepanich @ Jun 4 2018, 23:51)  Aner, несоответствие стандарту по уровню пересечения дифф. сигнала СК. Сейчас симуляция, разумеется. Причин может быть много, разных и неожиданных. Больше походит на влияние окружения, плохой земли, ... может не на самой трассе а на питание LVDS драйверов. Если много слоев, пробуйте перенести в другой слой этот CK (обязательно между земляными) может будет зацепка и найдете влияние. Еще пробуйте ваш меандры перевести в трамбоны, причем только на одной стороне линии, не так как сейчас на вашей каринке. Мой пример для CK.

|

|

|

|

|

|

|

|

Jun 5 2018, 18:17 Jun 5 2018, 18:17

|

Местный

Группа: Свой

Сообщений: 232

Регистрация: 8-06-05

Из: Москва

Пользователь №: 5 847

|

Товарищи, всем спасибо за ответы. На форуме Xilinx ответили про PCI Express: данные задержек применять надо.

|

|

|

|

|

|

|

|

1 чел. читают эту тему (гостей: 1, скрытых пользователей: 0)

Пользователей: 0

|

|

|