Цитата(Plain @ Aug 30 2018, 08:31)

Извлечение из поступающих сигналов полезной информации и создание из полезной информации исходящих сигналов — так понятнее?

Если Вы не способны создать синхронизацию, о чём собственно эта тема, то Вам, как и её автору, придётся делать послабление — сперва создание полного кадра в памяти, для эмоционального ощущения его целостности.

Так тема была создана для того, чтобы уважаемые гуру помогли помочь разобраться как правильно реализовать такую синхронизацию. И есть есть такой способ - то без применения внешнего кадрового буфера. И если мы не понимаем - чтобы нам дали пинка и разъяснили в чем мы не правы, и почему надо делать именно так, а не иначе, и данный процесс повторялся пока не наступит просветление в наших головах. Тогда и нам хорошо - мы поймем и будем знать как делать, и вам плюсик в карму. И база знаний накопится ещё одной толикой мудрости гуру(а форум я считаю в первую очередь отличной базой знаний), и вновь пришедшим и непросветлённым будет дана возможность созерцая эти страницы тоже наполниться мудростью...

Но уважаемые гуру лишь упрекают нас в неспособности создать такую синхронизацию....

Вот вы писали что:

Цитата(Plain @ Aug 30 2018, 08:31)

На вход подано неизвестных размеров изображение, следовательно:

1) измерить его размеры, для чего посчитать в его CLK длину его DE и количество DE за интервал его VS;

2) на основе этих данных пересчитать коэффициенты интерполятора и задать длину всех буферов;

3) измерить интервал от VS до DE и посчитать требуемую положительную или отрицательную задержку для получения в требуемый, т.е. с учётом задержки на FIFO, момент аналогичных выходных сигналов;

4) по очередному входному VS зафиксировать собранные данные в качестве новых настроек выходного автомата и начать выдачу им сигналов;

5) продолжать измерять всё вышеперечисленное.

Тут понятно все кроме пункта 4.

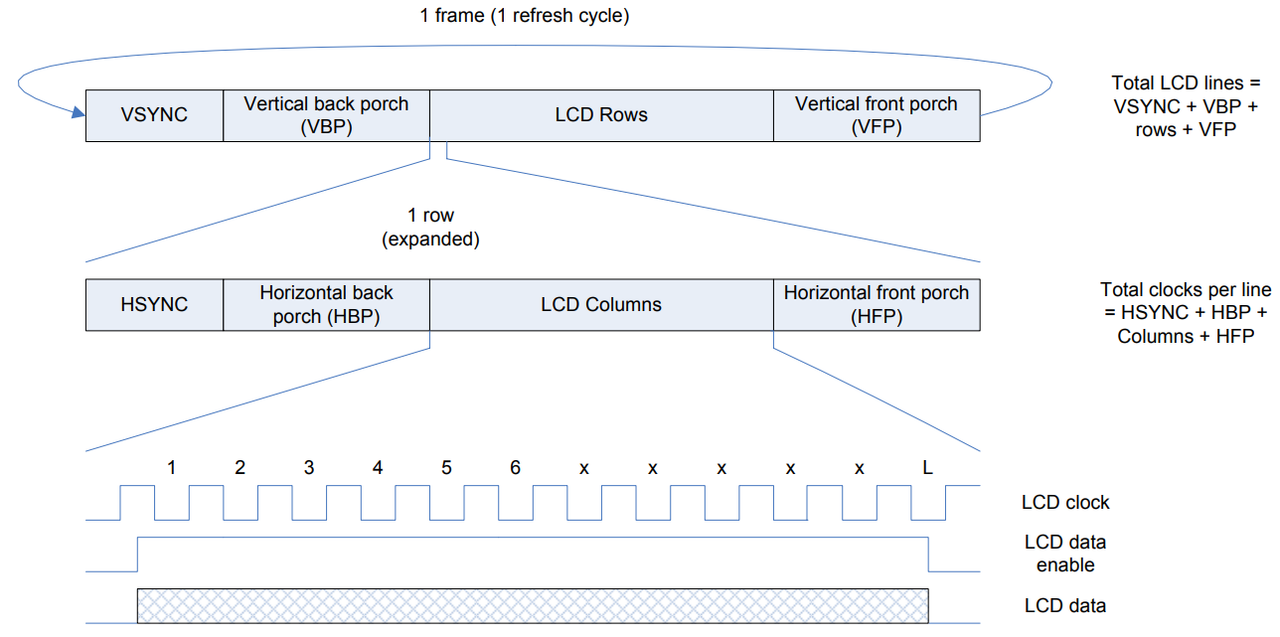

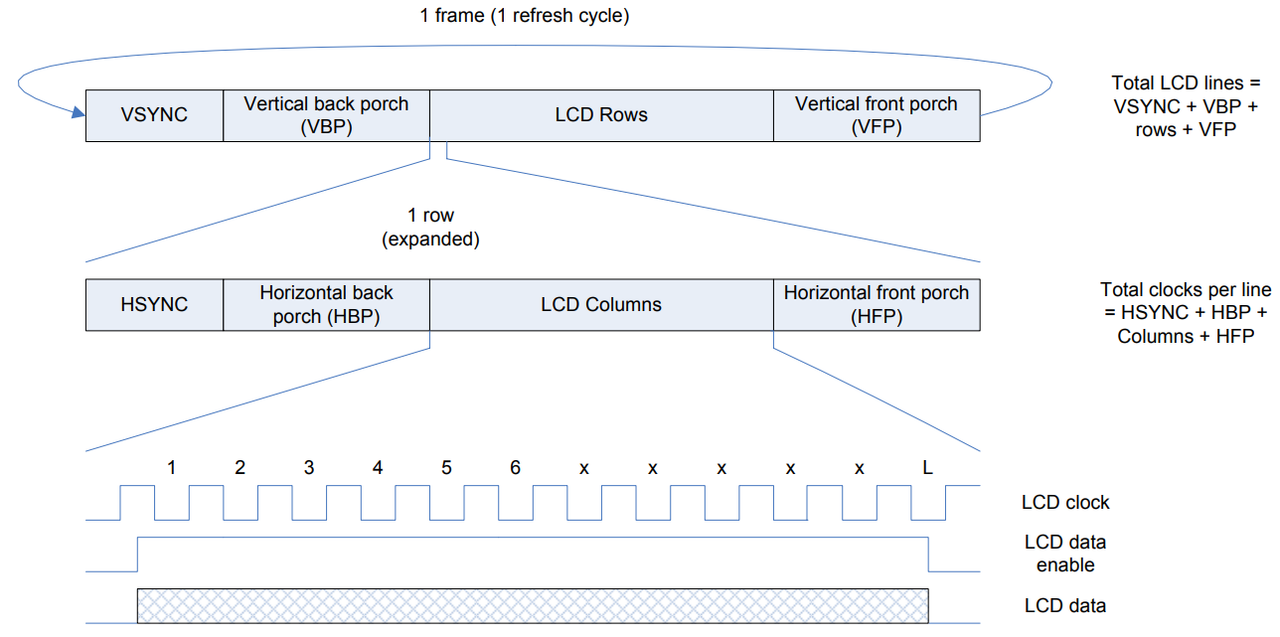

Приведу картину для наглядности:

Из неё следует что одна строка состоит из:

1. Периода строчного импульса горизонтальной синхронизации(HSYNC)

2. Периода задней границы (Horisontal back porch).

3. Периода активных даных (data_enable).

4. Периода передней границы (Horisontal front porch).

Допустим я измерил интервал интервал времени источника от конца импульса VS до начала активных данных.

Получил некую константу. Что мне с ней делать ? Расскажите поподробнее про это, если Вас не затруднит...

Я изучаю исходники альтеры, и мне кажется скоро я плюну на это. Жуть жуткая. Несколько тысяч строк кода без комментариев и какой-либо логики...

PS UPDА вообще тут правильно подметили, что такая синхронизация без применения внешнего буфера невозможна. Тому подтверждение найдено в xilinx appnote:

https://www.xilinx.com/support/documentatio...g-with-vpss.pdf